- 公開日:2020年09月04日

- | 更新日:2022年11月21日

熱設計とは?

- ライター:Daisuke Higa

- 電源

近年、民生品に限らず産業機器製品に対しても、小型化、高効率、大電力化が加速度的に進んでいます。それにより実装面積が非常に小さくなり集積度が高くなったことで排熱がしにくい環境が必然的に整い、結果的に発熱要因での課題や最悪設計の見直しというリスクが高くなります。最悪の場合、再設計や実験検証に人的リソースが繰り返し費やされ、時間効率が大きく低下する要因となってしまいます。そのような背景から、設計初段での熱設計の必要性が非常に重要となってきています。

ではどのように熱設計を行っていけばよいのでしょうか。

求める要求、精度にもよりますが、高精度、高効率を追求すれば高価なシミュレータの導入が最もいいのは明白ですが、本記事では可能な限り、設備投資を最小限に抑えかつ可能な限りのリスクヘッジが可能な手法を3回にわたってお伝えする予定です。

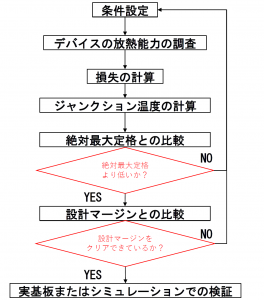

熱設計の手順(フロー)について

まず初めに、熱設計の手順(フロー)を押さえておきたいと思います。 基本となるフローは一般的に右記の通りです。

最も重要な熱源となる対象デバイスが実装される条件の設定からはじまり、次にデバイスの放熱能力の調査を行います。続いてデバイスの損失からジャンクション温度の上昇を計算し、その結果とデバイスの絶対最大定格、設計マージン(デバイス、基板等の劣化を考慮)を比較検証します。その結果でここまでの設計が妥当であるかを判断していきます。最終的に実基板やシミュレーションで設計の妥当性を検証していく流れとなります。

条件設定について

以下に挙げる3項目が主な条件となります。

- 前提条件 : 無風状態(No airflow)

- 周囲温度上限 例:60℃

- 対象デバイスのジャンクション温度上限(設計マージンの設定) 例:Tj<100℃

以下はシミュレーションを使用する際に必要となるパラメータの項目例となります。

- 基板の種類(FR-4等)-> 熱伝導率 例:FR-4 :0.0025 W/cm・℃

- 基板サイズ(銅箔エリア面積) 例:95mm*110mm

- 層数 例:4層(電源、GNDがそれぞれ内層に1層ずつ)

- 銅箔厚 例:35um(すべての層)

- デバイス直下のビア数、ビアサイズ 例 :6個, φ=0.4mm

デバイスの放熱能力を調査する

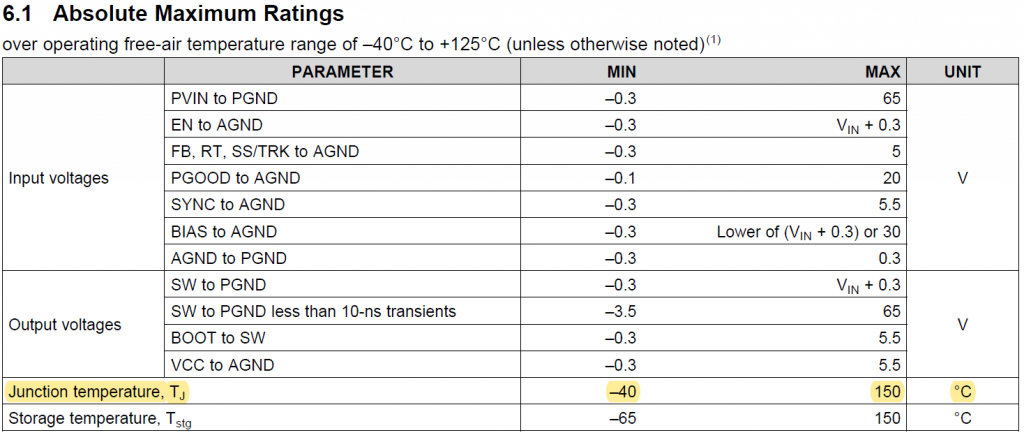

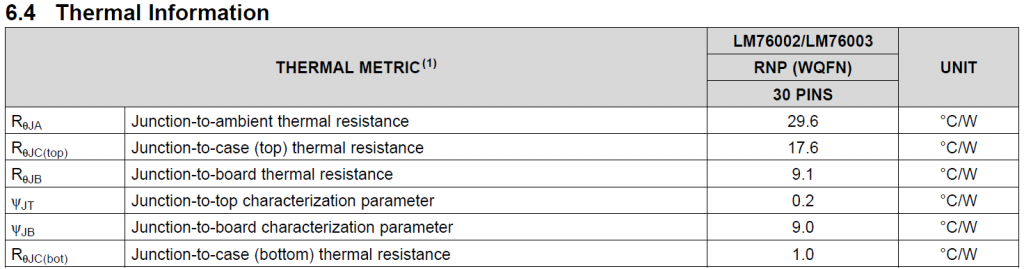

熱伝導特性、ジャンクション絶対最大定格の調査を行います。一般的には、デバイスのデータシートから以下の熱抵抗パラメータを参照します。

例:LM76002

- θja 29.6℃/W

- ψjt 0.2℃/W

- ψjb 9℃/W

- ジャンクション温度の絶対最大定格 150℃

(出典:データシート -LM76002/LM76003 3.5-V to 60-V, 2.5-A/3.5-A Synchronous Step-Down Voltage Regulator : https://www.tij.co.jp/product/jp/LM76002)

損失の計算

デバイスによって損失の計算方法は異なります。ここでは、DCDC降圧コンバータLM76002(テキサスインスツルメンツ社)を例として損失計算を説明します。

【使用条件例】

- 入力電圧:Vin 36V±10%

- 出力電圧:Vout 24V

- 最大出力電流:Iout 2A

入力側の供給電力を求めるために入力電流を知る必要がありますが、方法としては評価基板などを使用して実測定するか、電気回路シミュレータ(Spiceなど)から情報を入手するのが一般的かと思われます。ここでは、オンラインシミュレータWEBENCH Power Designerを使って入力電流の情報を入手しました。

- 入力電流:Iin_average=1.24A

- 入力側電力:Pin=36Vx1.24A=49.104W

- 出力側電力:Pout=24Vx2A=48W

降圧DCDCコンバータ回路による電力損失:Pd=Pin – Pout=1.104W

参考:効率 η=Pout/Pin=48/49.104=0.976 (97.6%)

その他設定 : スイッチング周波数 500kHz

以降では上記のような同期整流タイプのDCDCレギュレータにおいては、全損失の90%以上がデバイスの消費であり、その他周辺素子の損失はインダクタのAC損失が支配的となります。尚、同期整流タイプの製品は多くが内部のFETのスイッチング損失を見積もることが外部からできないため、主にシミュレータを用いて情報を入手する必要があります。この例におけるLM76002の場合、WEBENCH Power designerでのシミュレーション結果として最大で935mWとなっています。

(周辺素子、スイッチング周波数等の設定で変わってくることに注意)

ジャンクション温度の計算

デバイス損失から周囲温度上限時の最大ジャンクション温度Tj_maxを計算します。

計算式 : Tj_max=Ta_max+θja*Pd

- Ta_max:周囲温度上限

- θja:ジャンクション-周囲空間間の熱抵抗

計算例 Tj_max=60℃+29.6℃/W*1.104W=92.7℃

注意点としてθjaという値は、デバイスのデータシートにも記載があるように限定的な測定条件が前提となります。この値はJEDEC standardという規格で決められた条件で規定されていることが多く、測定される基板の設計基準があいまいなところがあり、実際に使用する実装条件とは乖離があると考える必要があります。

ここでは、θjaについて手順を説明するためだけに使用していますので詳細説明は割愛します。

絶対最大定格との比較

対象デバイスにおけるジャンクション温度の絶対最大定格規定と比較をします。

比較例

計算値 92.7℃

絶対最大定格 150℃

比較結果 : 絶対最大定格内のため、品質上問題はありません。

上記の比較結果では絶対最大定格内であるため問題ないと結論付けていますが、多くの場合は条件設定時に設計マージンをさらに追加して、こちらをジャンクション温度上限として設計を進めるほうががいい場合があります。

設計マージンとの比較

熱設計の手順として設計マージンをジャンクション温度の絶対最大定格に追加して検討することをお勧めします。理由としては、FR-4の耐熱は130℃ですが劣化の懸念があるため推奨は100℃以下が一般的であるなど対象デバイス以外への影響も考慮するためです。

例 設計マージン条件 Tj<100℃

マージン設定理由:FR-4の耐熱は130℃であるが劣化の懸念があるため推奨は100℃以下。

最終的には実際に実装された状態での実動作時の温度測定をして設計が問題ないかを検証します。

実基板での検証

最終的に実基板での測定で事前の設計が正しいことを検証で確認しますが、その検証の方法について少し触れていきたいと思います。デバイスのジャンクション温度を実測できる、例えば測定用出力を持っていれば別ですが、実際にジャンクション温度を測定することは難しいことが多いです。ではどうすればいいかというと、測定可能な部分で測定をし、既に調査済みの熱パラメータから推定するという手法を使います。ここで使うパラメータはψjtです。

Ψjtはデバイスのパッケージ表面からジャンクションへの熱伝導特性を表しており、実装条件からの影響が小さいパラメータのため、精度はθjaよりも高いです。以下では実測した温度からジャンクション温度を計算していく例を記載していきます。

例:LM76002の場合

入出力の電力を測定し、損失を計算します。

- 入力電流:Iin_average=1.25A

- 入力側電力:Pin=39.6Vx1.25A=49.5W

- 出力側電力:Pout=24.1Vx2A=48.2W

- 降圧DCDCコンバータ回路による電力損失:Pd=Pin – Pout=1.3W

- 参考:効率η=Pout/Pin=48.2/49.5=0.974 (97.4%)

- その他(実測) : スイッチング周波数 511kHz

次に、パッケージ表面においての温度を測定します。測定時のポイントとしては測定温度に測定環境による測定誤差を生じさせないように非接触温度計または小型の熱電対(サーマルコンパウンド使用)にて測定することが推奨されます。

測定例

- パッケージ測定温度 105℃

- サーマルパッド測定温度 93.6℃

上記実測値から以下計算手順にてジャンクション温度を計算していきます。

計算式 Tj = Tc + ψjt * Pd または Tj = Tb + ψjb*Pd

- Tc:実測したパッケージ表面温度

- Pd:実測したデバイスの損失(実測ではインダクタの損失含が含まれる)

- Ψjt:データシート記載のジャンクション-パッケージ表面間の熱抵抗値

- Ψjb:データシート記載のジャンクション-サーマルパッド間の熱抵抗値

Tc=105℃、Pd=1.3W、ψit=0.2℃/W(LM76002)から、Tj=105.26 または、Tb=93.6℃ ψjb=9℃/WからTj=105.3℃ と計算できます。

上記の例ではパッケージ表面温度の実測から推定されたジャンクション温度は事前に計算した温度よりも若干ではありますが高い結果となっています。実際の実装状態での基板の放熱特性が計算で使用したθjaよりも悪かった可能性があることがわかります。この段階で温度に問題がある場合は、若干のマージン超過であれば損失を下げる工夫(スイッチング周波数を下げる等)で対応できるかもしれませんが大幅に超えてしまっていると、選定したデバイスそのものであったり、基板の実装状態まで見直しが必要になる場合もあり、設計工程に非常に大きな影響がでてしまいます。

まとめ

今回はあくまで一般的な手法、手順について説明をしました。手順を理解することで熱設計では始めの設定が重要であることがわかります。ただ、実装する基板の放熱能力を基板を作成する前に予測することが難しいので、いざ最終的な実装基板での検討で問題がでてしまうと後戻りによる時間ロスが大きく後の工程に影響が甚大です。事前にできる限り正確な見積りができる方法としては、高価なシミュレーションシステムを導入するほうがいいことは明白ですが、費用対効果を考えたときに導入の判断が難しいとお考えの方に、できる限り低コストで実現できる方法、手法を次回より提案していきたいと思います。