- 公開日:2021年02月24日

- | 更新日:2022年11月30日

TI社製 ネットワーク・シンクロナイザー LMK05xxxのメリットとは?

- ライター:mtmt

- クロック

はじめに

クロックジェネレータの製品、「ネットワーク・シンクロナイザー」をご存じでしょうか?

ネットワーク・シンクロナイザーはその名前の通り、入力された信号に同期したクロックを生成する製品です。

ネットワーク機器では、外部から供給された信号に同期した、より低ジッターで高品質なクロックが求められます。

ネットワーク・シンクロナイザーに求められる要求事項は以下です。

①広いオフセット周波数において低ジッター

②Hitless Switch(ヒットレススイッチ)機能

③1ppsのリファレンス入力が可能

④デジタルホールドオーバー

これら、ネットワーク機器に要求される様々な機能を満たす為、ネットワーク・シンクロナイザーはアナログPLL(APLL)とデジタルPLL(DPLL)を併用しました。

なぜAPLLとDPLLを併用したのでしょうか?本稿ではAPLLとDPLLの動作原理、その特徴について説明します。

ネットワーク・シンクロナイザーの構成

ネットワーク・シンクロナイザーの説明に先立ち、APLLとDPLLの原理を説明します。

その後、ネットワーク・シンクロナイザーの構成を説明します。

構成① - APLLの説明

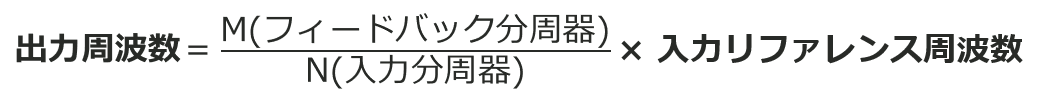

APLLはアナログ方式のPLLです。

以下の通り入力分周器, 位相周波数比較器, チャージポンプ、ループフィルター(アナログ), VCO, フィードバック分周器で構成されます。

入力リファレンス(IN+)とフィードバック(IN-)を位相周波数比較器で比較し、その結果をUP/Downパルスとして出力します。

Up/Downパルスはチャージポンプで+/-の電流量に変換され、後段のループフィルターによって平滑され、電圧に置き換えられます。

その電圧によって VCOの周波数を調整して、IN+とIN-の位相差が無くなるように制御します。

以下計算式に従い、入力リファレンス周波数から、異なった出力周波数を生成することができます

構成② - DPLLの説明

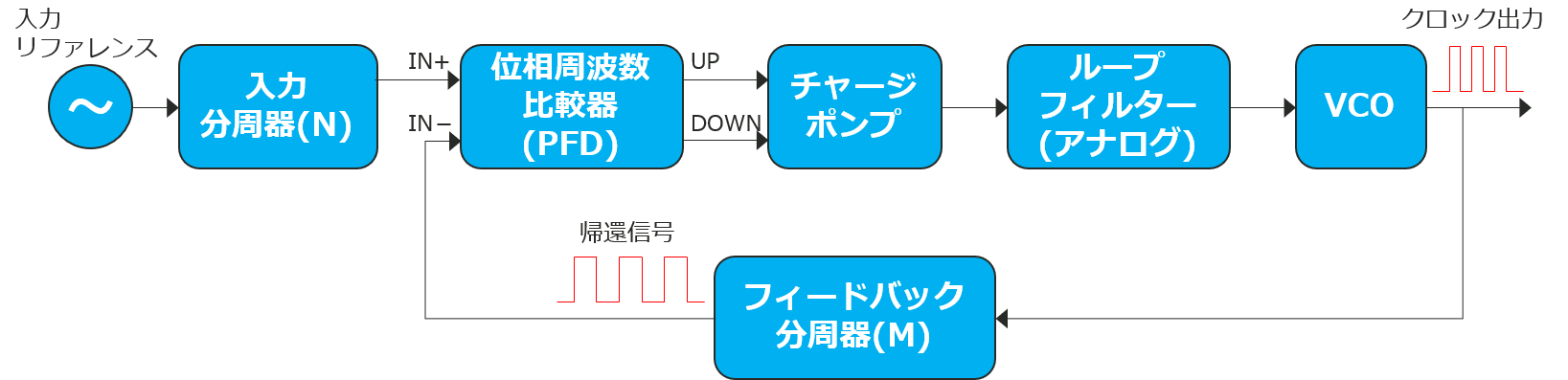

続いてDPLLの仕組みについて説明します。基本的な動作はAPLLと同じです。相違点は以下です。

・位相比較周波数(PFD) → タイムデジタイザー(TDC, 入力パルスを比較しデジタル出力)

・アナログループフィルター → デジタルループフィルター

・VCO → DCO(デジタル制御発振器 )

アナログ制御からデジタル制御に変わり、チャージポンプは存在しません。

APLLと異なり、 ハードウェアを変更せずに、ループパラメータを最適化することができます。

但し、APLL同様に、最適なジッター性能を得るために、リファレンス, DCO周波数, ループフィルターの設計に注意を払う必要があります。

(参考資料:「PLLのループ帯域を決定する4つの要素とは?!」)

構成③ - ネットワーク・シンクロナイザー LMK05028の構成

ネットワーク・シンクロナイザーファミリー製品を紹介します。

各デバイスによってAPLLとDPLLの使用数が異なります。

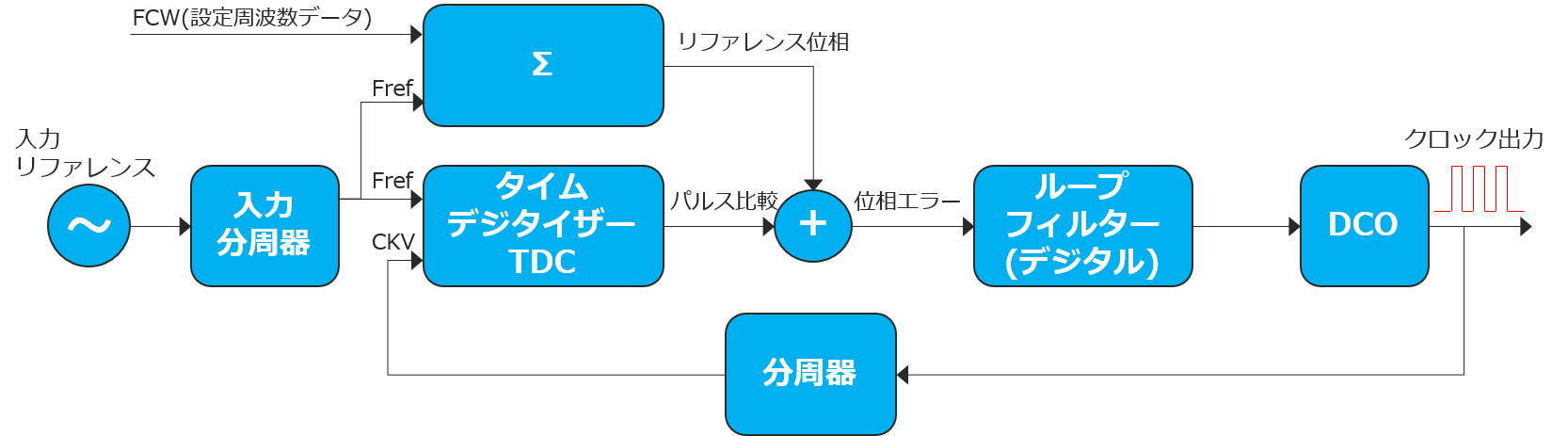

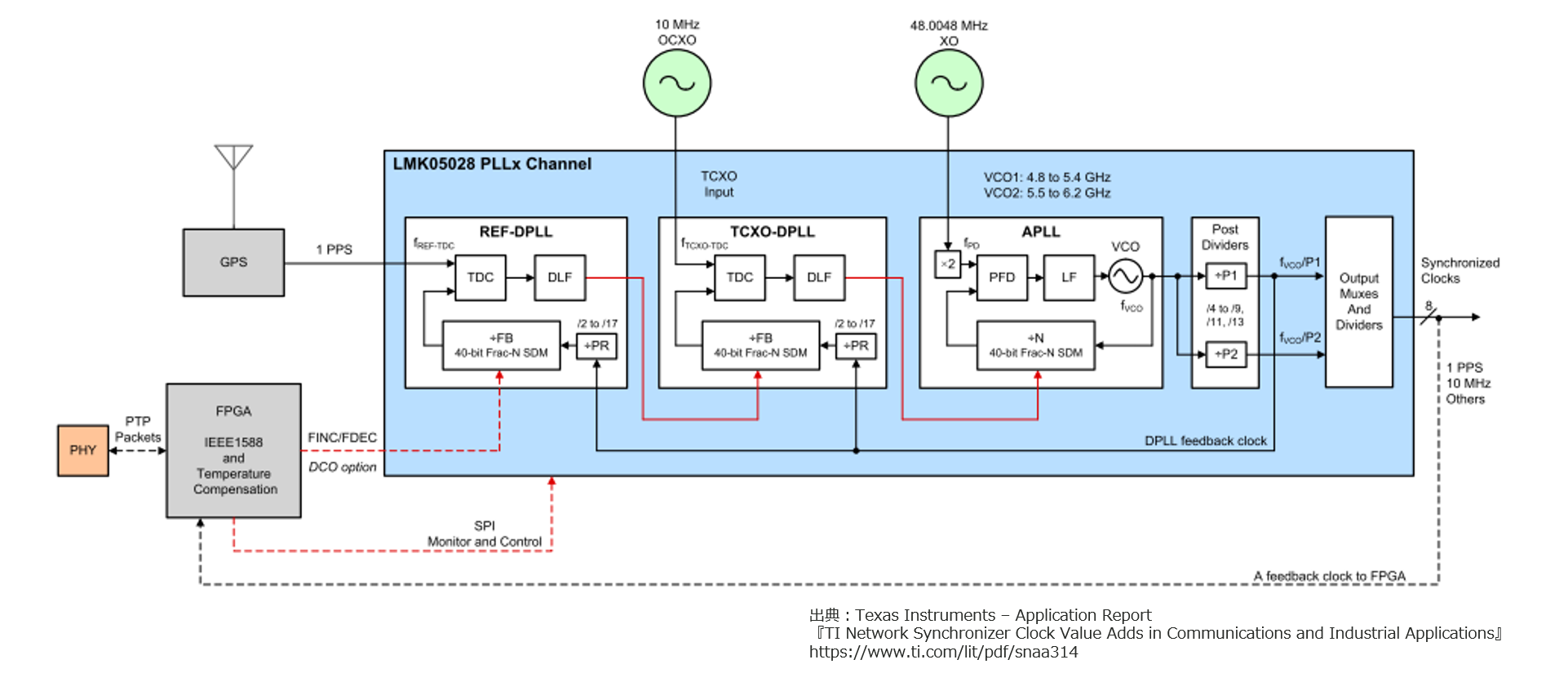

まず初めに、LMK05028の構成を見て行きます。このICはDPLL×2、APLL×1で構成されます。

REF-DPLLは、リファレンスクロックとAPLLからのフィードバッククロック(下図のDPLL feedback clock)との位相を比較します。

TCXO-DPLLはTCXOとAPLLのフィードバッククロックとの位相を比較します。また、TCXOはホールドオーバーのリファレンス入力になります。(※ ホールドオーバーに関しては後程記載があります)

TCXOのフィードバック分周器もREF-DPLLによって制御されます。

リファレンスクロックが無い状態では、APLLはローカルXOリファレンス入力にロックします。

リファレンスクロックが入力されると、補正ワードによって制御されます。APLLは低ジッターVCO1(4.8GHz~5.4GHz), VCO2(5.5GHz~6.2GHz)の2種類から最終的な出力周波数を決定できます。

これにより、フレキシブルな周波数が選択可能です。

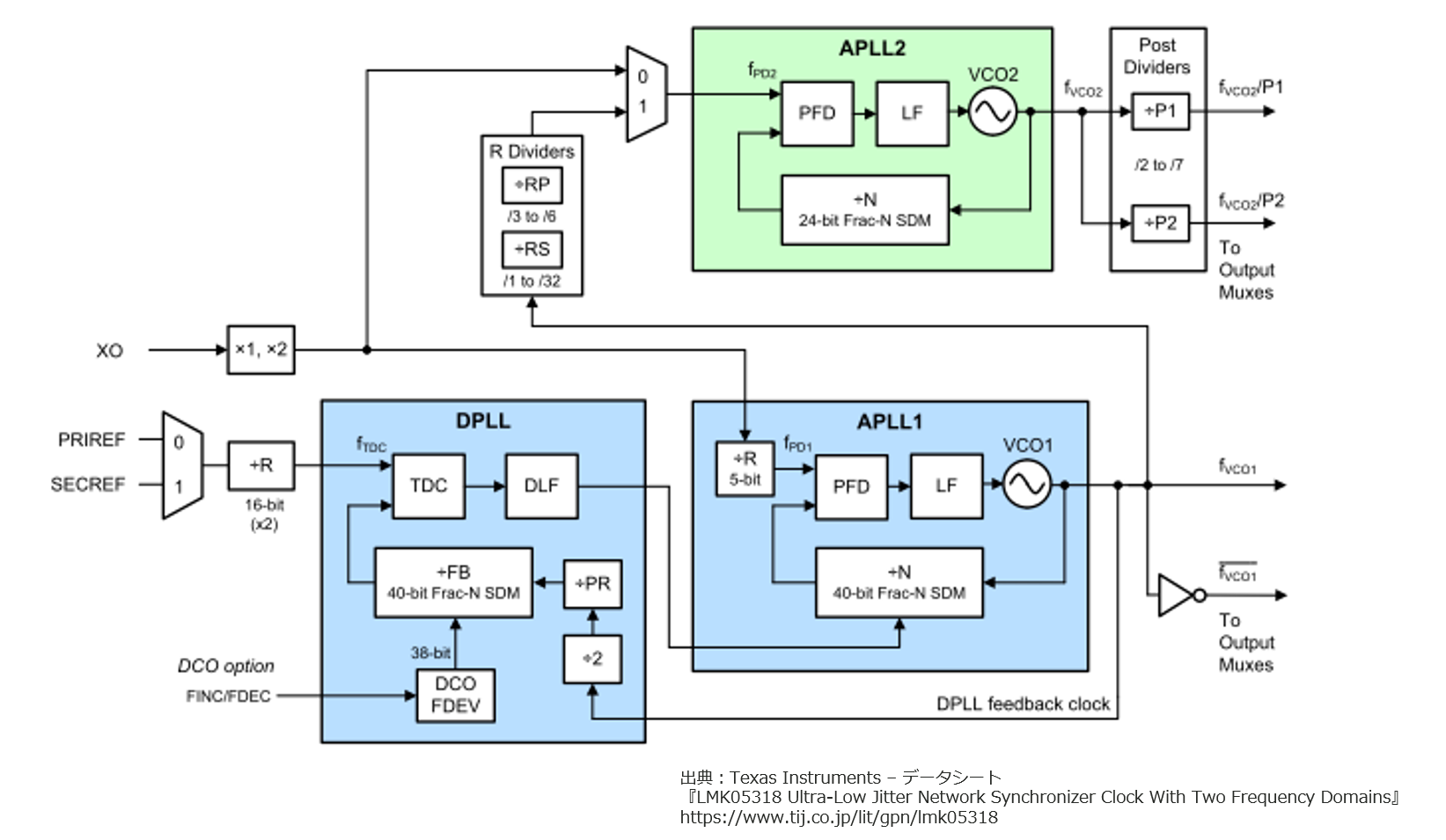

構成④ - ネットワーク・シンクロナイザー LMK05318の構成

次に、LMK05318の構成を説明します。このデバイスはDPLL×1、APLL×2で構成されます。

DPLLは、外部リファレンスクロックとAPLL1からのフィードバッククロックとの位相を比較します。

LMK05028同様に、リファレンスクロックが入力されると、VCO周波数は補正ワードによって制御されます。

リファレンスとVCO位相が一致するように、Fractional Dividerの値で補正します。

DPLL→APLL1→APLL2のカスケード接続が可能です。APLL1はVCBOを採用しているので、超低ジッターです。(なお、APLL2は通常のLC-VCOです。)

APLL1とAPLL2をカスケード接続することで、低ジッターで任意の出力周波数を得ることができます。

ネットワーク・シンクロナイザー 要求事項

それでは、LMK05XXXはネットワーク・シンクロナイザーに求められる4つの要求事項をAPLLとDPLLの併用で実現できたのでしょうか?それぞれ、各項目を説明します。

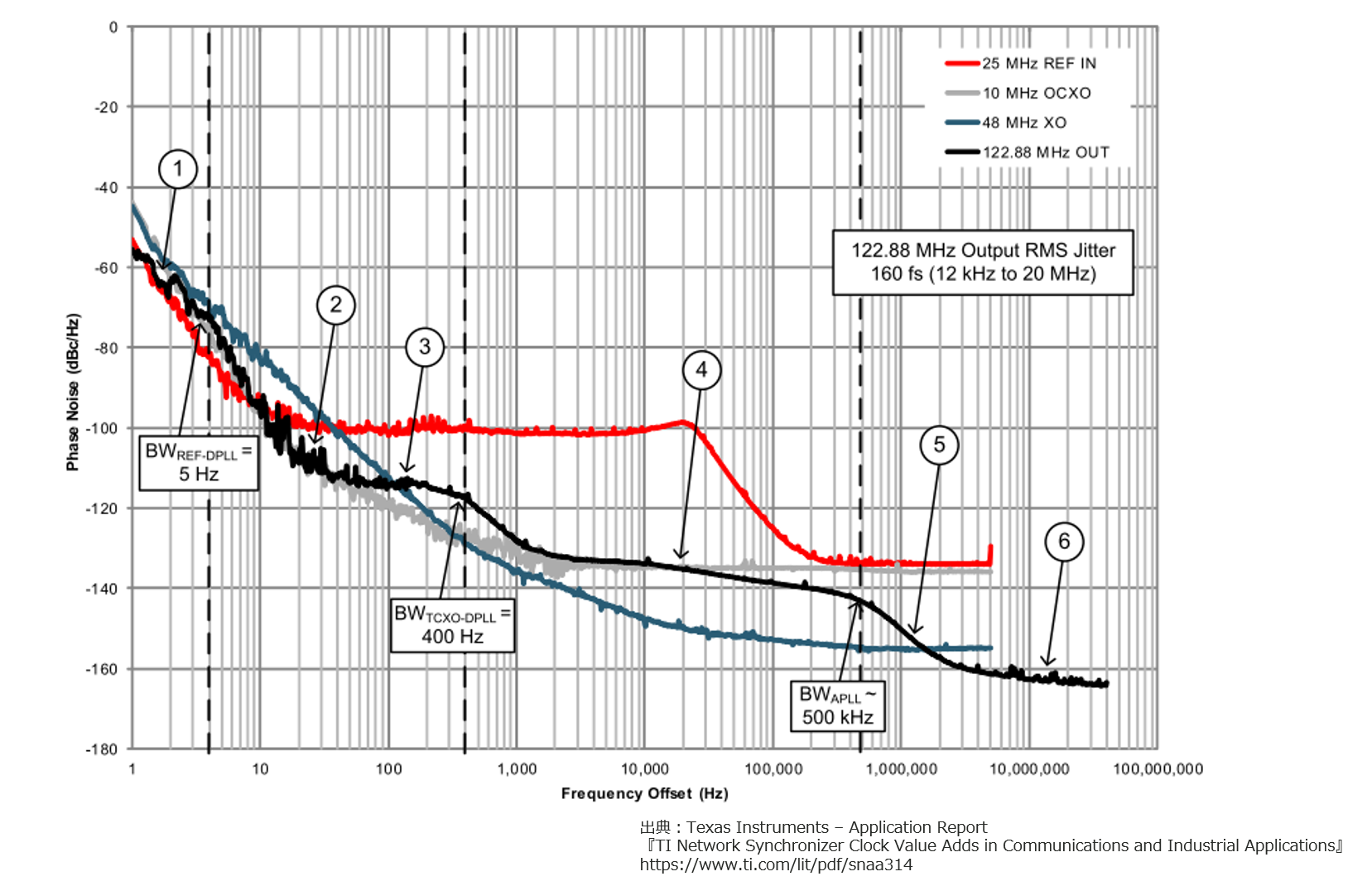

要求事項① - 広いオフセット周波数において低ジッター

以下はLMK05028に内蔵された3つのPLL、DPLL×2, APLL×1の位相ノイズを示します。

DPLL2はTCXOを使用します。APLLはXOを使用します。5Hz~400Hzの範囲ではTCXOの低位相ノイズと安定性を活用します。

400Hz~500kHzの範囲ではXOの低位相ノイズ特性を活用します。

これらの工夫 で、低周波帯域はDPLLによって低ジッター、高周波帯域ではAPLLによって低ジッター化を実現しました。

これにより、最終的なクロック出力122.88MHzの全オフセット周波数で低位相ノイズを実現しました。

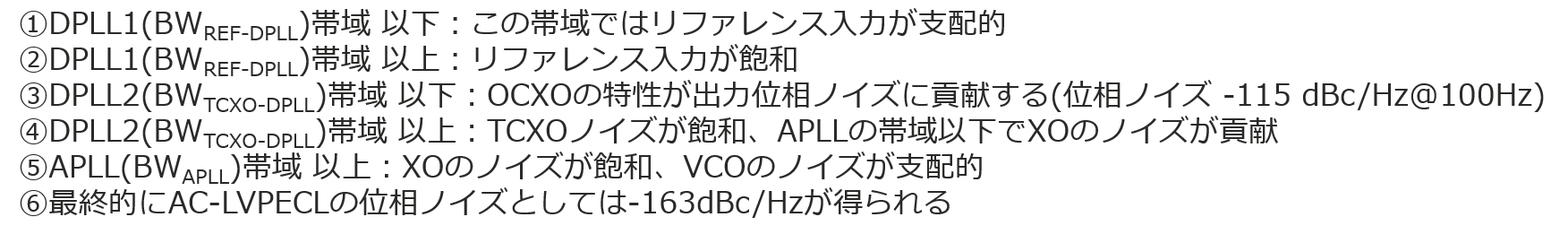

要求事項② - Hitless switch(ヒットレススイッチ)機能

Hitless Switchは入力リファレンスが切り替わった際にPhase Disturbance(位相擾乱)が出ないようにする機能です。

競合他社の製品では、リファレンス入力が切り替わった際のPhase Disturbanceは数nsです。

これに対し、TI社 LMK5xxx製品では50ps(標準) 程度と、非常に優れた位相過渡性能を示しします。

下図は、10MHz出力において、25MHzのリファレンス入力をHitless Switchで切り替え時のPhase Disturbanceです。

Phase Disturbanceは210.37mdegです。時間に換算すると、おおよそ58psです。

要求事項③ - 1ppsのリファレンス入力が可能

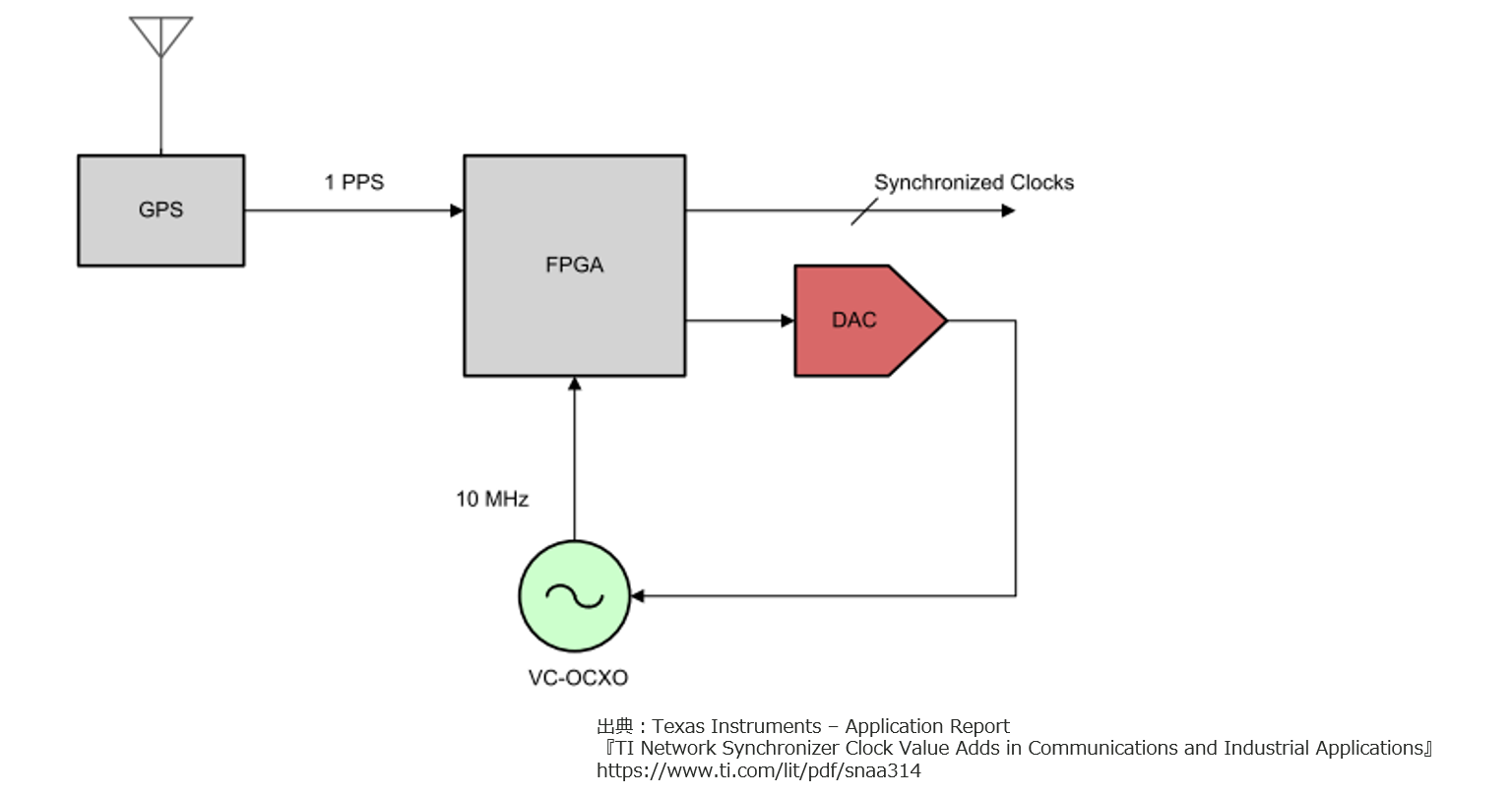

GPS基準入力を利用した同期クロックジェネレータアプリケーションでは、GPSからの1PPS信号と、電圧制御オーブン制御水晶発振器(VC-OCXO)クロックを分周したクロックとの位相を比較します。(以下イメージをご参照下さい)

上図のようにFPGAを使用して、クロック生成回路を構成することもできます。

しかし、FPGAを用いて実現した場合は低ジッターという要求を満たせない場合があります。

低ジッターが必須のアプリケーションでは、ジッタークリーナが必要です。

DPLL+APLL からなるLMK05xxxシリーズICを使えば、1ppsのリファレンス入力から低ジッターのクロックを生成することができます。

要求事項④ - デジタルホールドオーバー

リファレンス入力が喪失した状態で、有効な入力が利用できない場合、PLLはホールドオーバーモードに入ります。

ホールドオーバーモードでは、出力はリファレンス入力喪失前の周波数を正確に維持することが求められます。

LMK05xxxではチューニングワード履歴モニター機能を使用することが可能です。

履歴機能が有効な場合、ホールドオーバーに入ったときの初期出力周波数の精度はロックされたときの過去の平均周波数によって決定します。

一方、履歴が無効な場合、ホールドオーバー周波数の精度は、レジスタ設定によって決定されます。

LMK05xxxのリファレンス入力が有効になると、PLLはホールドオーバーモードを終了します。

出力グリッチを発生させることなく、新しい入力リファレンスクロックに自動的に位相ロックします。

アプリケーションへの応用

ネットワーク・シンクロナイザー、LMK05xxxファミリー製品は以下のアプリケーションに最適です。

いずれのアプリケーションも、 同期クロックが必要かつ、前述記載のメリットである1pps入力, HitlessSwitch, 低ジッター等が要求されます。

■アプリケーション例■

・IEEE-1588 PTP(ネットワーク時刻同期)

・100G OTN(光トランスポートネットワーク)

・無線基地局(BTS)

・業務用ビデオカメラ – 放映映像向けクロック(ビデオクロック)

(参考資料:「放映映像向けクロックに最適なクロックジェネレータとは?」)

まとめ

本稿にてAPLLとDPLLを使用したシンクロナイザー、LMK05xxxファミリー製品の構造やメリットをご理解頂けたと思います。

ネットワーク・シンクロナイザーは、さまざまな範囲の入力リファレンスでのクロック同期対応、かつより優れた位相ノイズ特性を要求されるアプリケーションに最適です。

本稿を通じて、ネットワーク・シンクロナイザーに興味を持ってい頂ければ幸いです。