- 公開日:2021年03月21日

- | 更新日:2022年11月30日

ESD保護素子を適切にレイアウトする方法

- ライター:FI43101

- 電源

初めに

電子機器の試作も終盤にさしかかり、ESD試験を行ったら通らない。アプリケーションに応じたESD保護ダイオードを使っているはずなのに思ったように特性が改善しない。

こんな経験はありませんか?このような場合、ESD保護素子のレイアウトに原因があるかもしれません。

本ブログでは、ESD保護素子を適切にレイアウトする方法について解説します。

なぜESD保護素子が必要なのでしょうか?

ESDは、通常、ケーブル接続やイヤホンなどのユーザーインターフェイス、またはキーボードのキーなどを介して侵入し、ESD電流がシステムに急速に流れます。(図1を参照)

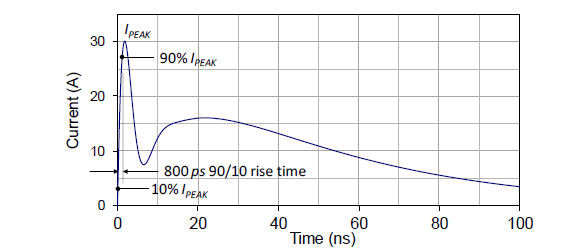

図1 IEC61000-4-2 Level4(8kV ESD)の波形

出展:Texas Instruments – https://www.tij.co.jp/jp/lit/pdf/slva680

TVSダイオードやESDダイオード等(ESD保護素子と称します。)を使用してESDからシステムを保護するには、ESD保護素子を介してESD電流 が適切にグランドに流れるようにバイパスする必要があります。

集積回路(保護したいIC)に与えられるESD電圧は、ESD電流と伝送ラインのインピーダンスを乗算した結果です。

ESD電流は外部から入ってくるため制御できません。

このため、ESD電圧を最小化するためには、GNDへのインピーダンスを下げることになります。

ただ、単純に信号(電源)ラインからGNDのインピーダンスを下げると信号ラインがGNDに短絡してしまいますから、ESD保護素子を使用して、ESDが侵入したときだけインピーダンスを下げるようにします。

ESD保護素子のレイアウトのヒント

ESDを流すためのインピーダンスの最適化

ESD保護の回路を設計する場合、寄生インダクタンスを考慮する必要があります。

寄生インダクタンスによる電流の変化は全体の電圧の変化を引き起こし、ボード全体の性能を不安定にします。

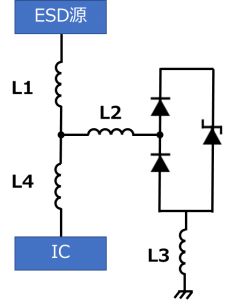

図2は、ESD源とESD保護素子の間の4つの寄生インダクタンスをモデル化したものです。

寄生インダクタンスは、基板のパターン幅および長さによって決定されます。

図2 ESD保護素子周辺の寄生インダクタンス

適切に設計されたシステムでは、ESD源とESD保護素子を介したグランドへのパスの間のインダクタンスが最小限に抑えられます。

インダクタンスを最小限に抑えるには、次の4つのレイアウトのヒントがあります。

- ESD源とESD保護素子を介したグランドへのパスの間のインダクタンスを最小限にします(L1+L2+L3≒0)。

- デザインルールで許可されている限り、ESD保護素子は、ESD源またはコネクタの近くに配置します(L1≒0)。

ESDコネクタから侵入するのが一般的であるため、侵入したESDを基板端で処理することで回路に対する影響を最小限にします。 - 保護されるICは、ESD保護素子からできるだけ離れた場所に配置します(L1+L2<<L4)。

- ESD保護素子とグランド間のインダクタンス(L3)を最小限に抑えます。これについては、次のセクションで詳しく説明します。

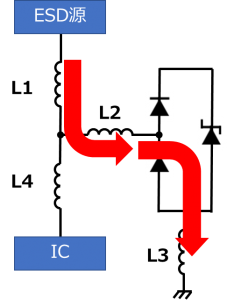

L1~L4が適切に設定されるとESDはTVSダイオードを経由してGNDに流すことができます。

図3 L1、L2、L3、L4を適切に設計にした時のESD電流の流れ

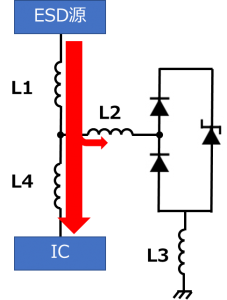

もし、ESD源とESD保護素子を介したGNDの間の寄生インダクタンス(L1、L2、L3)が大きくなるとESD電流が適切に流れないため、ICを適切に保護できない恐れがあります。

L4がL2よりも小さい場合は、ESD電流がICに向かって流れるため、ICを適切に保護することができません。

図4 L1~L4が適切でない場合のESD電流の流れ

ESDによるEMIの放射

ESDは急激にに変化するため、適切に処理しないと電磁干渉(EMI)を引き起こす可能性があります。

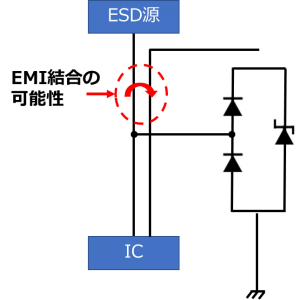

図5は、EMI放射がESD源とESD保護素子までの間で発生することを示しています。

ESDが侵入している間に急速に変化する電界は、基板パターンのインダクタンスがなくても近くの回路に影響を与える可能性があります。

インダクタンスがあると、EMIの影響がさらに大きくなります。

図5 ESD源とTVSダイオードまでのEMI放射

このため、保護されていない領域でパターンの引き回しを回避する必要があります。

ESDが発生すると、保護されていないラインとEMIが結合してICと直接影響したり、EMIをシステム内に入り込んだりして影響を与える可能性があるためです。

EMIの発生を防ぐためには、次の4つのヒントがあります。

1.ESDソースとESD保護素子の間の領域に保護されていない回路を配線しないようにします。

2.ESD保護素子は、極力ESDソースまたはコネクタの近くに配置します。

3.可能であれば、ESDソースとESD保護素子の間を直線でトレースします。

4.コーナーを使用する必要がある場合は、直角の引き回しを避け、最大45°で引き回すようにします。

ビアを使用したパターン設計

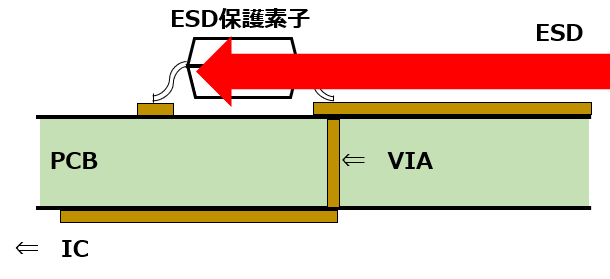

ビアによって層を切り替えることなく、PCB上のトレースをESD源からESD保護素子にルーティングすることが最も推奨されます(図6)。

ビアによる容量やインダクタンスの影響を少なくするためです。ESD電流はビアを通過して保護するICに送られる前に、ESD保護素子に自然に流れます。

図6 ESD源とTVSが同一面にある時のESDの流れ

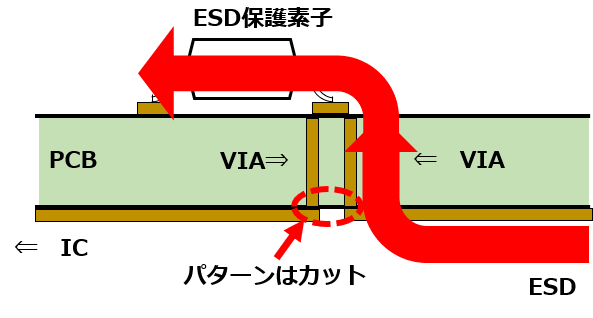

ただし、基板設計によってはビアを使用せざるを得ない場合があります。

その場合、図7のようにビアを二つ使用します。

ESD電流はビアを経由し、ESD保護素子に流れるため、ICを保護することができます。

信号は、二つ目のビアを経由してICに接続されます。

図6と比較すると、ESD保護素子に入力される前にビアの容量、インダクタンスの影響を受けますが、ESD電流を確実にESD保護素子に流すことができます。

図7 ビアを二つ使用した時のESDの流れ

図8の例では、ESD電流は保護されたICとビアで分岐してESD保護素子に向かいます。

ビアは、インダクタンスとして働くため、ESD保護素子に向かってESD電流はほとんど流れず、保護されるICに向かって流れてしまいます。

このため、この方法は避けなければなりません。

図8 ビアを一つ使用したときのESDの流れ

ビアで配線する場合は、次の2つのヒントがあります。

1. ESD電流とESD保護素子の間のビアを避ける。

2. ESDソースと保護されたICの間にビアが必要な場合は、分岐構成を避け、ビアを二つ使用して、ESD電流が確実にESD保護素子が向かうようにします。

ESD保護のためのGND配線の最適化

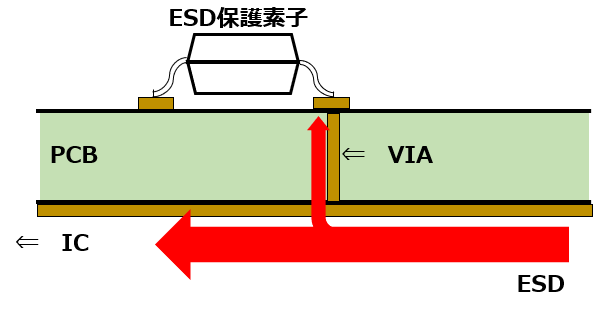

ESD保護のためには、グランドへのインピーダンスを低くすることが非常に重要です。

ESD源とTVSの間のすべての寄生インダクタンスを最小化することは、ESD保護素子が最適に接地されていることが前提になります。

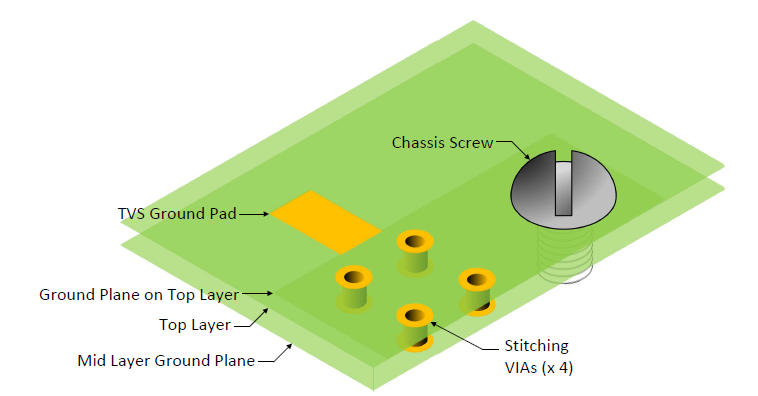

図9に、最上層のグランドプレーンに接続されたESD保護素子のグランドパッドを示しています。

図9 基板の表層から内層パターンへのGND接続の例

出展:Texas Instruments – https://www.tij.co.jp/jp/lit/pdf/slva680

ESD保護素子のグランドピンは、同じ層のグランドパターンに接続され、すぐ隣の層の別のグランドプレーンと接続します。

これらのグランドパターンはビアで接続する必要があり、1つのビアはTVSのグランドピンの直近にあります。

次のヒントを使用して、非常に低いインピーダンスで接地方式を最適化します。

1. ESD保護素子のグランドピンを同じ層のグランドパターンに接続し、すぐ隣の層の別のGNDパターンに接続します。

2. 可能な場合は複数のグランドプレーンを使用します。グランドプレーンの層数を増やすことでインピーダンスを下げることができます。

3. 接地されたシャーシネジを使用してPCBのグランドをシャーシに接続し、コネクタの接地シールドとしてESD保護素子およびESD源の近くに配置します。

4. 大径のビアを使用してインピーダンスを下げることができます。

より詳細な説明が必要な場合は、Texas Instruments社アプリケーションノート(SLVA680)を参照してください。 https://www.tij.co.jp/jp/lit/pdf/slva680

まとめ

ESD保護素子を適切に動作させるためには、以下の3つのポイントがあります。

1. ESD源からESD保護素子の寄生インダクタンスを抑える必要があります。

2. ESD源からESD保護素子は同じパターンに配置するのが最適ですが、別の面に配置しなければならない場合は、ビアを二つ使用して確実にESD保護素子を経由するようにします。

3. ESD保護素子のGNDはできるだけ他のGND面と接続してインピーダンスを下げます。

ESD保護素子の性能を引き出すことができるよう、考慮いただければ幸いです。