- 公開日:2021年03月24日

- | 更新日:2022年11月30日

ドロップアウト電圧の正体!

- ライター:Nishie

- 電源

はじめに

リニアレギュレーターを検討する際に、ドロップアウト電圧(VDO)という言葉を耳にすることがあると思います。

リニアレギュレーターのデバイス毎にドロップアウト電圧の値が異なります。

*ドロップアウト電圧についてはこちらをご参照ください。

ではなぜデバイス毎にVDOが異なるのでしょうか。それは内部構造の種類によって違いが生じるからです。

本記事では内部構造の種類や原理・問題点についてご説明いたします。

内部構造の種類と原理・問題点

内部構造の種類

まずはリニアレギュレーターの内部構造の種類をご説明いたします。

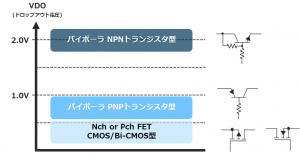

リニアレギュレーターのタイプには、図1のようにVDO=2.0VのバイポーラNPNトランジスタ型、VDO=0.3~1.2VのバイポーラPNPトランジスタ型、VDO≦0.6VのNch FETやPch FETを使用したCMOS型やBi-CMOS型がございます。

バイポーラNPNトランジスタ型が初めに登場し、3.3Vから2.5Vをつくりたいという市場要求から低VDOのバイポーラPNPトランジスタ型が開発されました。しかしPNPトランジスタ型は自己消費電流が大きくなるという問題がございました。

バイポーラPNPトランジスタ型の自己消費電流を何とかしようと開発されたのが、制御トランジスタにPch MOSFETを、エラーアンプにCMOSを使用したリニアレギュレーターです。

自己消費電流が低く、さらなる低VDOを実現したPch MOSFET/CMOS型ですが、負荷変動により発生した電圧変動がエラーアンプを介しての負帰還のみで制御される・応答速度の制約があるといった問題があり、これらを解決するためにNch MOSFET/Bi-CMOS型が開発されました。

図1 リニアレギュレーター内部構造の種類とVDOの関係

ドロップアウト電圧発生の原理・問題点

■バイポーラNPNトランジスタ型

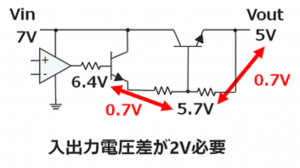

まず、バイポーラNPNトランジスタ型リニアレギュレーターの内部がどのようになっているのか・なぜVDO=2.0Vとなるのか、その原理について図2を基にご説明いたします。

内部構造は、差動アンプを使用したエラーアンプにバイポーラNPNトランジスタを2個使ったダーリントン接続を追加しています。このダーリントン接続によって大きな電流増幅度を稼いでいますが、VDOが大きくなる原因にもなります。

出力電圧(Vout)=5Vで動作させたい場合、ダーリントン接続前段のNPNトランジスタのエミッタ(Vout側)は5Vになりますので、ベースにはダイオードの順方向電圧(Vf=0.7V)だけ高い5.7Vを印加する必要がございます。同様にダーリントン後段のNPNトランジスタのベースには、5.7+0.7=6.4Vの電圧を印加する必要がございます。

これだけ見れば、「入力電圧(Vin)は6.4Vでいいじゃないか。」と思うかもしれませんが、エラーアンプが6.4Vを出力するために電源電圧にマージンが必要なので、電源電圧としては7Vが必要になります。

つまり、リニアレギュレーターで5Vを出力するためにはVinが7V以上ないと動作できないということになります。

これがVDO=2Vとなる原理です。

図2 バイポーラNPNトランジスタ型リニアレギュレーター内部構造

■バイポーラPNPトランジスタ型

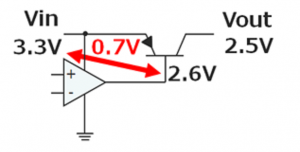

次に、バイポーラPNPトランジスタ型リニアレギュレーターの内部がどのようになっているのか・なぜVDO=0.3~1.2Vとなるのか、その原理について図3を基にご説明いたします。

内部構造は、エラーアンプにバイポーラPNPトランジスタを1個接続したものとなっており、Vinがエミッタ、Voutがコレクタになります。

トランジスタを制御する電圧は、エミッタより0.7V低い電圧になりますので、Vin=3.3Vの時ゲートには0.7V低い2.6Vの電圧で駆動することができます。

また、3.3VのVinを低下させてVoutを作りますが、トランジスタはベースドライブを大きくしてコレクタ-エミッタ間を飽和領域手前の0.3V程度まで低下させることができます。これによってVDOを0.3Vまで下げたリニアレギュレーターを作る事が可能となります。

バイポーラPNPトランジスタの種類にもよりますが、これがVDO=0.3~1.2Vとなる原理です。

しかし、PNP制御にした結果、VDOは小さくなりましたが自己消費電流が増加しました。

これは制御電流がエミッタから入り、ベースに抜け、エラーアンプがGNDに流すことにより制御されていますので、出力電流の一部がGNDに流れ回路内の消費電流が増加するためです。

図3 バイポーラPNPトランジスタ型リニアレギュレーター内部構造

■Nch FET, Pch FETのCMOS型とBi-CMOS型

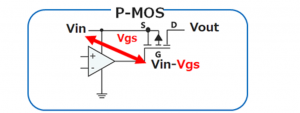

最後に、Nch FETやPch FETを使用したCMOS型やBi-CMOS型リニアレギュレーターの内部がどのようになっているのか・なぜVDO≦0.6Vとなるのか、その原理について図4, 図5を基にご説明いたします。

P-MOS型の内部構造(図4)は、制御トランジスタにPch MOSFETを、エラーアンプにC-MOSを使用したものになります。

FETはバイポーラトランジスタとは異なり電圧駆動素子ですので、Vinより低いゲート電圧(Vin-Vgs)を印加することで出力電圧を制御することができます。VDOはFETのOn抵抗分になりますのでVgs<Vfとなり、FETを使用することで低VDOを実現しております。

ここで問題となるのがPch FETの場合、ソース-ゲート間の電圧はVinとエラーアンプの出力間電圧であり、Voutの電圧はドレインになるため負荷変動によって発生した電圧変動は100%エラーアンプが負帰還して制御するしかありません。さらに出力コンデンサによる位相遅延した電圧を負帰還しているので制御が発振しないように、位相補償回路が必要となり、リニアレギュレーターの応答速度はCMOSのエラーアンプの制御能力で制約されてしまいます。

図4 Pch FETを使用したCMOS型(P-MOS)リニアレギュレーター内部構造

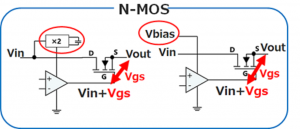

これらの問題を解決するため、Pch FETをNch FETに変更し、CMOSをBi-CMOSに変更したN-MOSのチャージポンプ型(図5左)と外部バイアス型(図5右)です。

Nch FETを使用することにより、ゲート駆動電圧はVoutよりも1V高い電圧が必要ですが電流はほとんど必要としません。

そこでチャージポンプ型は、Nch FETとBi-CMOSのエラーアンプから構成されるリニアレギュレーターに超小型のチャージポンプ回路(赤丸部分)を組み込み、Vinを2倍か3倍に昇圧してエラーアンプに供給することで、Voutよりも高いゲート駆動電圧(Vin+Vgs)を作る事が可能となります。これによりFETのOn抵抗によるVDOのみで動作可能なリニアレギュレーターとなります。

また、外部バイアス型はVinを昇圧するチャージポンプ型とは異なり、ゲート駆動電圧を外部からバイアス電源(3.3Vや5.0V)として供給してNch FETを駆動する構成になっております。

FETを駆動する電源を外部から供給することで、入出力電圧差(Vin-Vout)は、ある程度FETのOn抵抗で自由に選択できるようになります。

例えばフルOn時の抵抗が50mΩのFETを使えば、1A流しても最小50mVのドロップアウト電圧まで制御が可能です。それにより、VDOを極めて小さくした、大電流が流せるリニアレギュレーターを実現しております。

図5 Nch FETを使用したBi-CMOS型(N-MOS)リニアレギュレーター内部構造

おわりに

リニアレギュレーターのVDOの種類や原理・問題点についてご説明させて頂きました。

なにかご不明な点がございましたらお気軽にご相談ください。