- 公開日:2021年12月27日

- | 更新日:2022年11月18日

FPGAを使用したLMH12xxのSPI制御

- ライター:Miki

- インターフェース

概要

TI社のLMH12xx ファミリーICは、SDIと呼ばれる放送機器用インターフェースに使われる半導体製品群です。 これらの製品は、SPIやI2Cと言ったシリアルバスを使うことで、デバイスの持つ豊富な機能を使い熟すことができます。 そこで、FPGAを使って、SPIバスを経由し、内部レジスタをアクセスするためのVHDLコードサンプルを作成しました。

本書では、最初に、簡単にLMH12xx製品群を紹介し、SPIインターフェース経由でこれらのICを制御するための手順を説明します。 続いて、VHDLコードのシミュレーション結果に触れ、最後に、VHDLコード各部の役目について解説します。 SDIインターフェースを備えた機器を設計されるハードウェアエンジニアの方々にとって役立つものと思います。

はじめに

1989年にハイビジョンの実験放送が始まって以来、凡そ30年が経ち、4Kテレビの時代に移行しました。 この4kテレビ放送を支えるのが12G SDI技術です。SDI(Serial Digital Interface)は俗称で、米国映画テレビ技術者協会SMPTE(Society of Motion Picture and Television Engineers)によって策定された規格です。

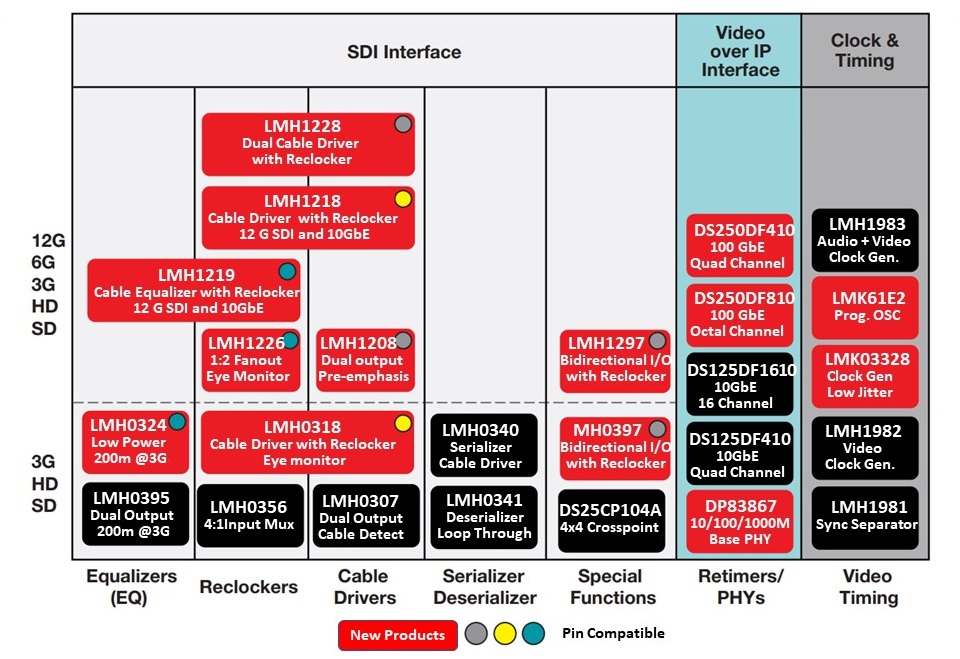

この規格に従えば、4kテレビの持つ大量のデジタル情報(12Gbps)を、リアルタイム、且つ、非圧縮で、75Ω同軸ケーブルを使い、数十メートル以上離れた機器に伝送することができます。 TI社のLMH12xxファミリーICは12G SDI物理層に使われる製品群です。 図‐1にTI社の放送機器用半導体製品一覧を示します。

図‐1 TI社のプロフェショナル放送機器用半導体製品一覧

出典:Texas Instruments – セレクションガイド”Broadcast and Professional Video Interface Solutions” (Rev E) https://www.ti.com/lit/pdf/SNAC042

代表的製品を挙げます。

LMH1218はケーブルドライバICです。 SMPTE ST-2082-1 (12G)、ST-2081-1 (6G)、ST-424 (3G)、 ST-292 (HD)、 ST-259 (SD) 各規格に準拠した電気信号を生成して75Ω同軸ケーブルを駆動します。

LMH1219は、ケーブルイコライザICです。 同規格に準拠した信号を受信し、長いケーブルで損失した高周波信号を再生するICです。 このICを使用すれば、最長、約70メートルの長いケーブルを使用しても確実な伝送が可能になります。

LMH1297はケーブルドライバ、ケーブルイコライザの両機能を一つのパッケージの収め、外部制御信号により入出力を切り替えて使用できるICです。

これらのICには、その動作モードを設定するための制御端子やステータス表示用の端子が備わっています。 この為、ICを基板に半田付けし、電源を供給さえすれば、レジスタ群の初期設定をすること無く、直ちに使用できます。 しかし、I2C、もしくは、SPIと言ったシリアル・インターフェースを通じ、IC内部のレジスタにアクセスすることで、これらのICが持つ豊富な機能を活用することができます。

シリアル・インターフェースを通じて内部レジスタをアクセスするには、マイクロプロセッサを使うのが一般的です。 ただ、わざわざマイクロプロセッサを実装したくない、あるいは、ソフトウェアエンジニアの手を借りたくないと言った事情から、FPGAを使ってレジスタアクセスを実現したいという声をよく耳にします。 そこで、FPGAを使い、SPI 経由でLMH12xx内のレジスタをアクセスするVHDLコードサンプルを作成しました。

LMH12xxファミリーICのSPI通信手順

SPIインターフェースは標準規格が無く、メーカー、あるいはデバイス毎に通信手順が異なります。 VHDLコードの説明に先立ち、LMH12xxファミリーデバイスのSPI通信手順について説明します。

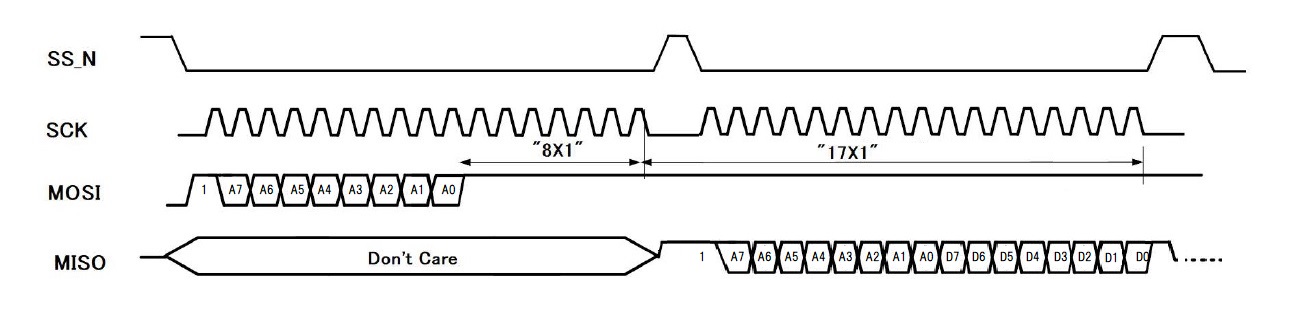

SPIホストコントローラからSS_N、SCK、MOSIが出力されます。 LMH12xxからはMISOが出力されます。 図‐2にSPIを経由してLMH12xxレジスタに書き込む手順を示します。

① アイドル状態ではSS_Nは論理High。

② ホストコントローラがSS_Nを論理Lowにすることで通信を開始。

③ ホストコントローラはMOSIに最初のデータを出力した後、SCKをトグル。

④ LMH12xxはSCKがLowからHighに遷移する時MOSI上のデータをサンプリング。

・ この動作を17回繰り返す。

・ MOSI上のデータは書き込みか読み出しを示すR/Wビット(Low=書き込み)を先頭に

・ アドレス8ビット(MSBからLSBの順)

・ 続いてデータ8ビット(MSBからLSBの順)と続く。

⑤ ホストコントローラは17ビットの転送が終わるとSS_NをHighに戻す。

⑥ この時、LMH12xxは入力されたデータをIC内部に取り込み、IC設定に反映。

図‐2 SPIを経由したLMH12xxレジスタ書き込み手順

次に、SPIを経由してLMH12xxレジスタ情報を読み出す手順を図‐3に示します。 書き込みと違い、読み出しは、2回の17ビット転送サイクルが必要です。 最初の17ビットの転送サイクルではアドレスを転送します。 続く17ビットの転送サイクルで、先のサイクルで指定したレジスタ・アドレスのデータを取得します。

図‐3 SPIを経由したLMH12xxレジスタ読み出し手順

加えて、LMH12xxのSPIアクセス手順では、各SPIアクセス後、次にアクセスに入るまで 1us 以上の休止時間が必要です。

また、LMH12xxのレジスタへの書き込みに際しては、Read-Modify-Writeと呼ぶ方法を使うと便利です。 LMH12xxのレジスタは8ビットです。 レジスタの中には複数の異なる制御機能が一つのアドレスに割り当てられているものが存在します。 あるいは、リザーブビットと呼ばれ、ユーザーには公開されず、変更禁止で、値も不確定なものも存在します。

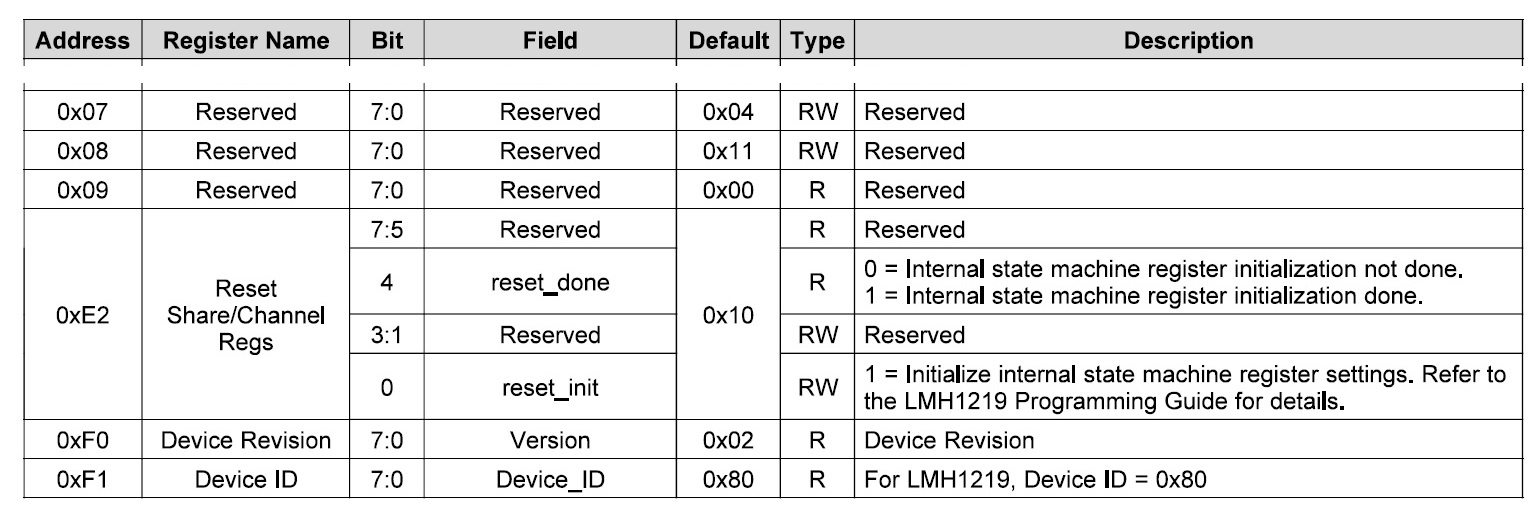

LMH1219ケーブルイコライザICに内蔵されたリクロッカを初期化する手続きを例に、詳しく見て行きます。 図‐4はLMH1219のレジスタマップの抜粋です。 リクロッカを初期化する信号は、アドレス0xE2番地、ビット0に割り当てられています。 他方、このアドレスには、リセット制御とは関係が無い、IC内部で使われる信号も割り当てられています。それらはReserved ビットと呼ばれます。 Reservedビットを変更すると、ICは正常な動作を続けられなくなります。 そこで、Read -Modify-Write手法を使い、リクロッカを初期化します。

図‐4 LMH1219 Share Register抜粋

出典:Texas Instruments –データシート” LMH1219 Low Power 12G UHD Adaptive Cable Equalizer

with Integrated Re-clocker Datasheet”, SNLS530D–REVISED JUNE 2018,

https://www.tij.co.jp/lit/gpn/lmh1219

Read -Modify-Writeではマスクビットを使用します。 マスクビットは、8ビットのレジスタデータの内、変更したいビットには‘1’を、変更したくないビットには‘0’を指定します。

例えば、マスクビット0xF0を指定すると、上位4ビットは書き替えるが、下位ビットはレジスタ内にある情報を保持します。 Read -Modify-Writeは下記の手順でレジスタをアクセスします。

① 書き換えたいレジスタ・アドレスの情報を読み出す。

② それに対し、書き換えたくないビット情報にマスクを掛ける。

③ マスクの掛っていないビットに変更を加える。

④ 処理した8ビット情報を該当レジスタに書き戻す。

この例では、Shear Registerアドレス0xE2を読み出し、マスクビット0x01を適用します。 その後、0x01、乃至0x00、何れかを上書きすると、ビット0を除くビットは保護され、ビット0のみが書き換わります。 これにより、他の機能に影響を与えることなく、リクロッカを初期化できます。

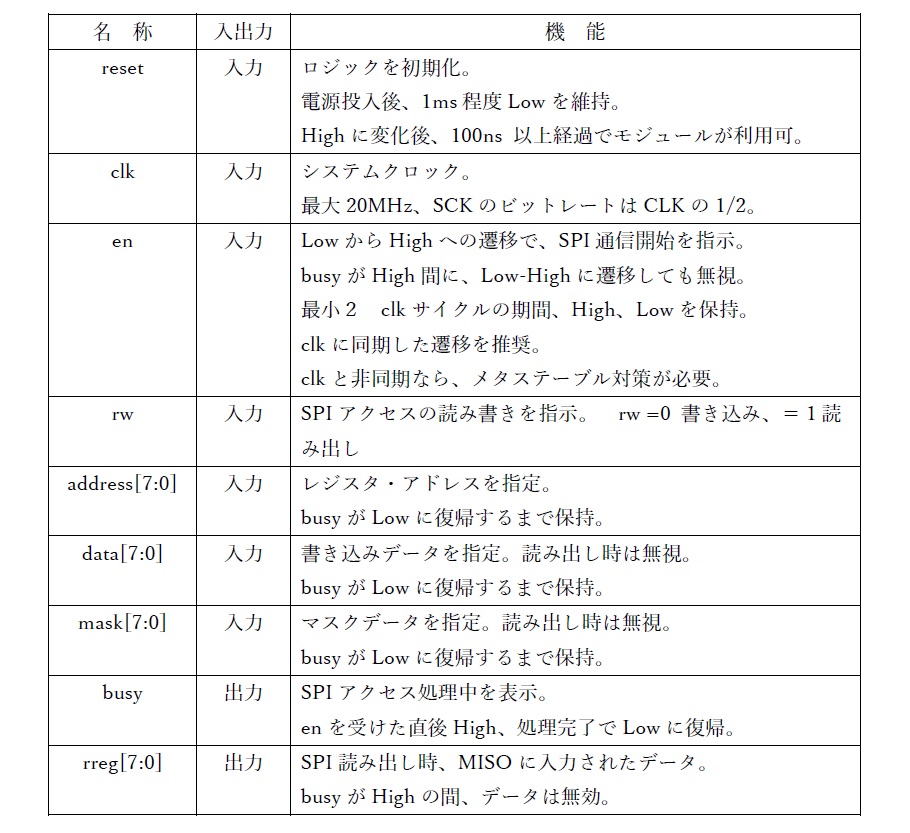

VHDLモジュールのAMI (Application Module Interface)

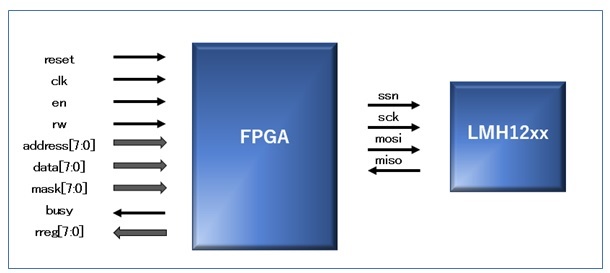

VHDLモジュールのAMIを図5に示します。

図‐5 VHDLモジュールのAMI

アプリケーション側の入出力信号は以下です。

今回作成したVHLDモジュールは、SPIの読み出しと書き込み、両方に対応します。

読み出し時は、rw信号をHighにします。 addressを入力し、その後、en信号をHighにします。 これに呼応して、VHDLモジュールはbusy信号をHighにしてSPIアクセスを開始します。 2回の17ビット転送サイクルを実行し、SPIアクセスの休止時間の経過を待って、busyをLowに戻します。

書き込みは、Read-Modify-Writeを実行します。 書き込み時はRW信号をLowにします。 address に加え、data、mask情報を入力し、en信号をHighにします。 mask情報は、変更したいビットのみを‘1’にします。 maskに0xFFを指定すると、通常の書き込みができます。 Read-Modify-Writeでは、2回の読み出しと、1回の書き込み動作、並びに、SPIの休止時間を経た後、busyをLowにします。

VHDLコードのシミュレーション結果

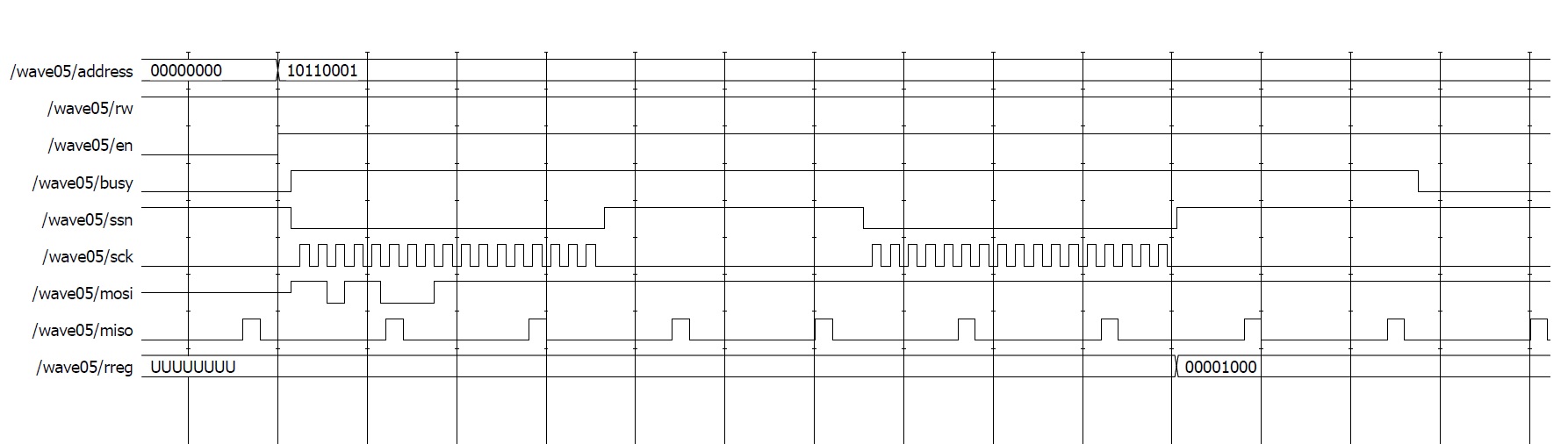

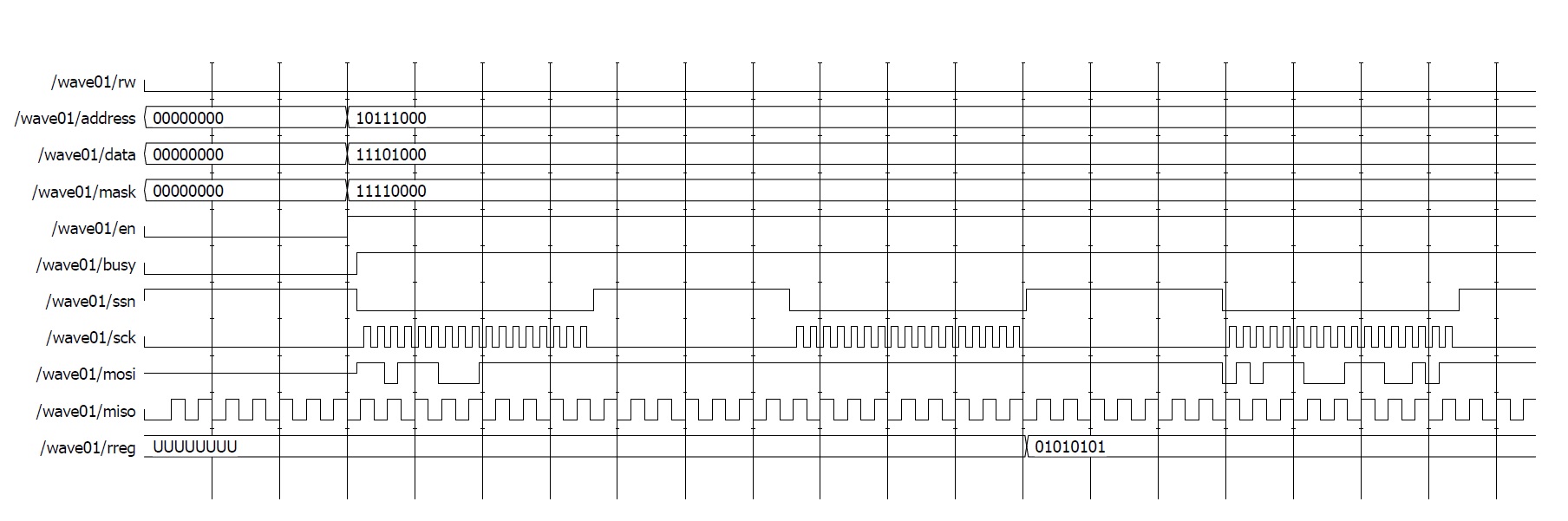

ModelSim® – Intel® FPGA Edition ソフトウェアシミュレータを使った、サンプルコードのファンクショナル・シミュレーション(配置配線を行う前で、遅延時間を0nsと見積もった)結果を図‐6~ 図‐12に示します。

SPI Readのシミュレーション結果を図‐6に示します。 2回の17ビットの転送サイクルを実施し、SPI休止時間を待ってbusyをLowにしています。

図‐6 Model SIM®を使ったSPI Readのシミュレーション結果

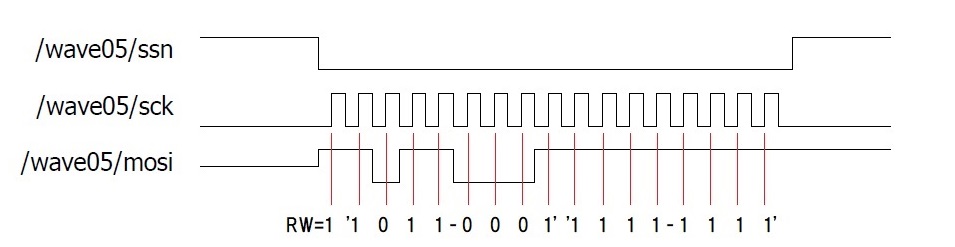

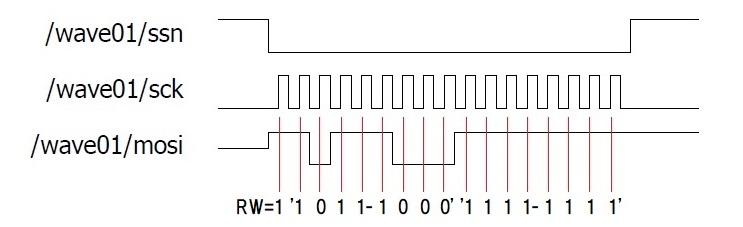

Read一回目の17ビット転送サイクル拡大図を図‐7に示します。 mosi波形に注目すると、読み出しを指示する‘1’に続き、指定したアドレスデータ “1011-0001” がMSBを先頭に、mosi上にシリアルに送信されます。 データはすべて‘1’が埋め込まれます。

図‐7 Read一回目の17ビット転送サイクル拡大図

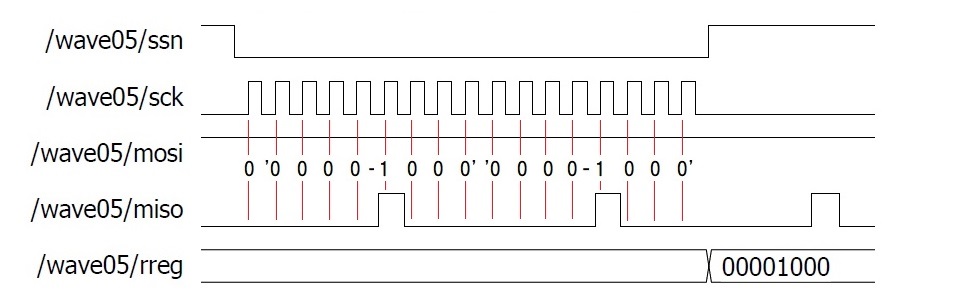

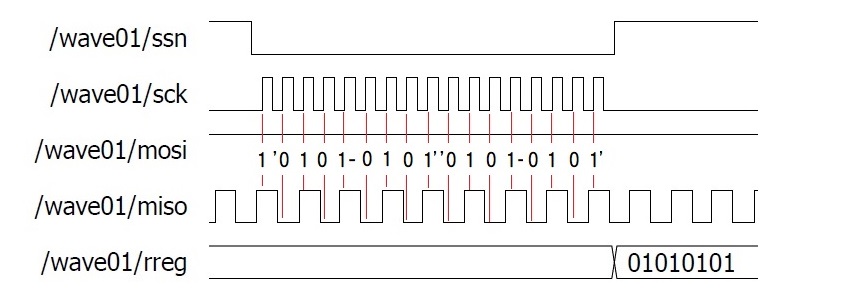

図‐8 はRead二回目の17ビット転送サイクル拡大図です。 miso上のデータ “0-0000-1000-0000-1000” を、ssnがLowからHighに遷移するタイミングで、下位8ビットをrregに取り込みます。

図-8 Read二回目の17ビット転送サイクル拡大図

SPI Read-Modify-Writeのシミュレーション結果を図‐9に示します。 このモードでは、Readのため、2回の17ビット転送サイクルを実行後、Writeのため1回の17ビット転送サイクルを行っています。 また、各サイクル後、1us以上の休止時間を確保しています。

図‐9 Model SIM®を使ったSPI Read-Modify-Writeのシミュレーション結果

図‐10はRead-Modify-Write 一回目の17ビット転送サイクル拡大図です。 読み出しを指示する‘1’に続き、アドレスデータ “1011-1000” がMSBを先頭に、mosi上にシリアルに送信されます。 データはすべて‘1’が埋め込まれています。

図‐10 Read-Modify-Write 一回目の17ビット転送サイクル拡大図

Read-Modify-Write 二回目の17ビット転送サイクル拡大図を図‐11に示します。 miso上のデータ “1-0101-0101-0101-0101” の下位8ビットを、ssnがLowからHighに遷移するタイミングでrregに取り込みます。

図‐11 Read-Modify-Write 二回目の17ビット転送サイクル拡大図

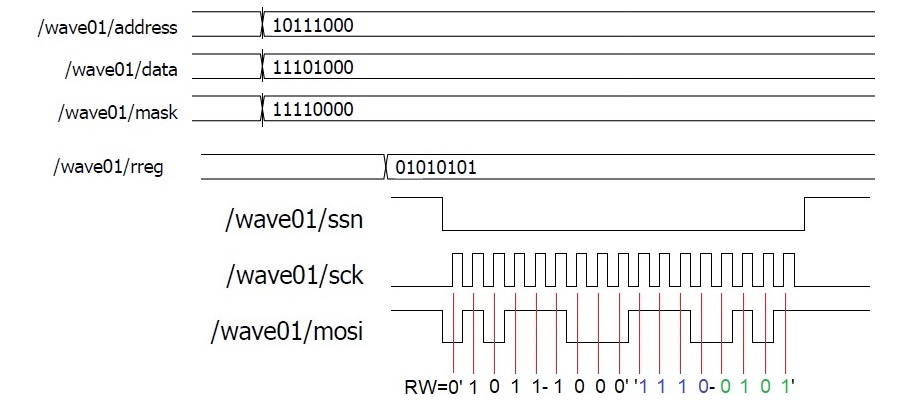

図‐12はRead-Modify-Write三回目の17ビット転送サイクル拡大図です。 このサイクルでは、書き込みを指示する‘0’に続き、指定したアドレスデータがMSBを先頭に、mosi上に、順次、送信されています。 続くデータ部に着目すると、マスクビット “11110000“ で保護された、下位4ビットは、先のReadサイクルでMISOから入力された情報 ”xxxx0101” が反映されます。 他方、保護の掛かっていない上位4ビットは、data に入力されたデータの上位4ビット ”1110xxxx“ がmosi上に送出されます。

図‐12 Read-Modify-Write三回目の17ビット転送サイクル拡大図

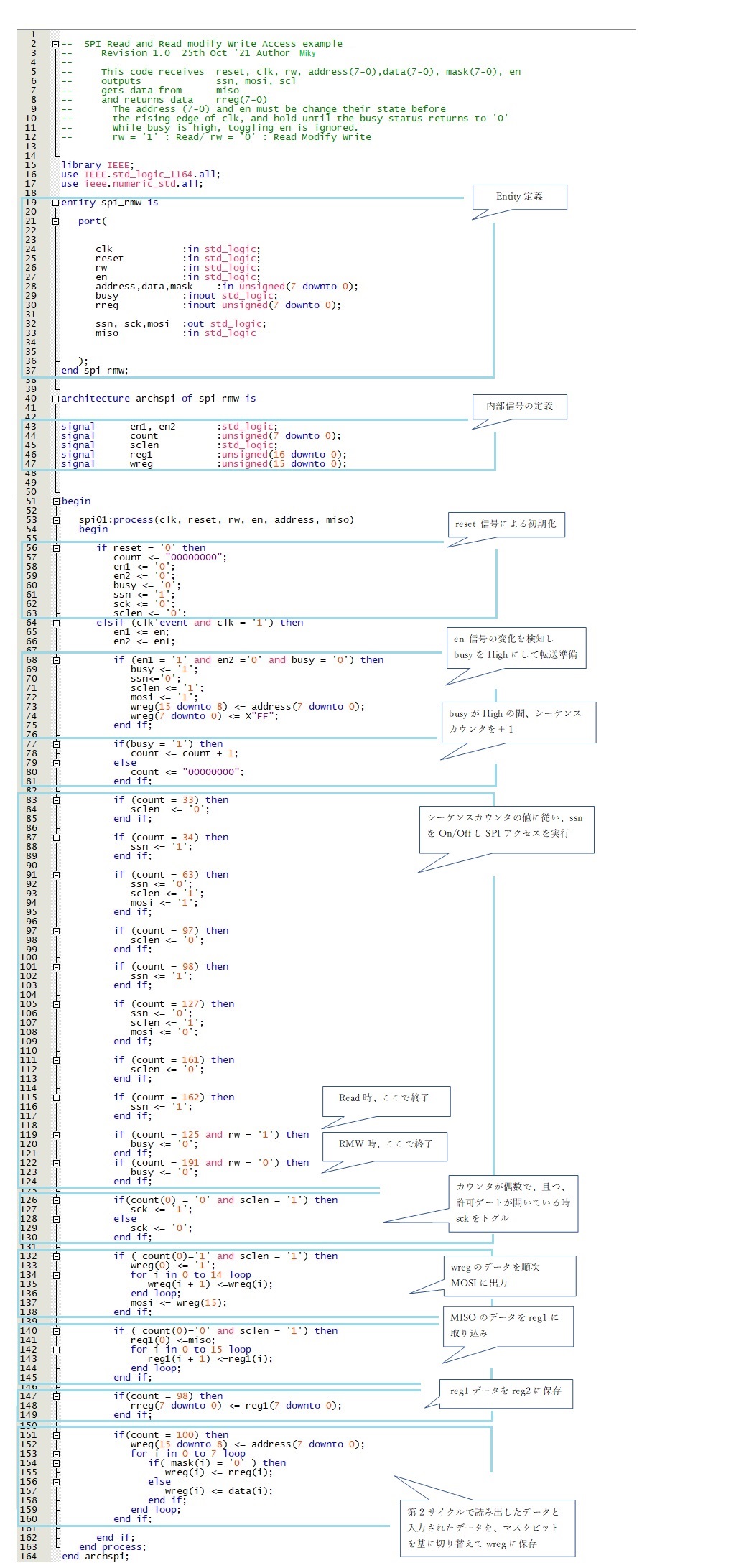

VHDLコード解説

右にテキスト形式のデータがあります。 ☞spi-rmw01

まとめ

FPGAからSPIバスを経由して、LMH12xx ファミリーIC内部レジスタをアクセスするためのVHDLコードサンプルと、そのシミュレーション結果を紹介しました。

SPIインターフェースは統一されたインターフェース規格が無いため、デバイス毎に微妙な違いがあります。 このため、このコードを他のデバイスの制御にそのまま使うことはできません。 しかし、添付したソースコードを変更すれば、各デバイスに合わせることは可能です。 例えば、SPIインターフェースを持つADコンバータの制御に使用することも可能です。

是非、ご活用ください。 なお、このコードは無償でご使用頂くことができます。 但し、このコードを使用したことによる結果については如何なる責任も負い兼ねます。 この点をご了承頂いた上でご使用ください。 また、このコードそのもの、あるいは、改版を加えたものに対し、著作権を主張されることはご容赦願います。

今後、シングルボードコンピュータ、Raspberry Piを使い、PythonによるGUI(Graphical User Interface)モードでのSPI制御プログラム作成を計画しています。 ご期待ください。