- 公開日:2022年06月06日

- | 更新日:2022年11月18日

LMK05028ネットワーク・シンクロナイザー 放送用映像機器に使用する前に覗いてみて!

- ライター:Miki

- クロック

はじめに

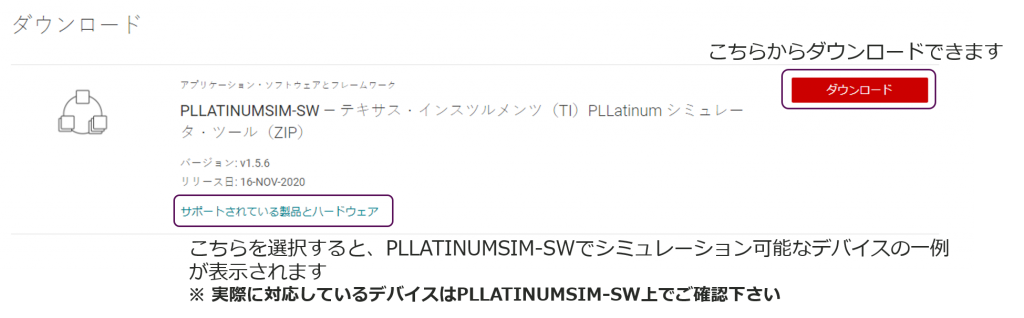

LMK05028 はネットワーク・シンクロナイザーと呼ばれ、デジタルPLLを用いた第4世代のジッタクリーナーICです。 このデバイスの詳細な特徴につきまして、以下をご参照下さい。

*「TI社製 ネットワーク・シンクロナイザー LMK05xxxのメリットとは?」 https://emb.macnica.co.jp/articles/15829/

このデバイスはネットワーク機器用途の他、放送用映像機器にも最適なデバイスと言えます。 しかし、 放送用映像機器用途では、そのアプリケーション特有の事情から、トラブルに直面することがあります。 本ブログでは、それらの事例に触れ、問題回避方法について解説します。 放送用映像機器を設計される方の一助になれば幸いです。

放送用映像機器アプリケーション特有の事情

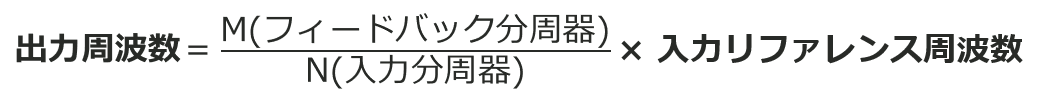

放送用映像機器では、各装置を同期して動作させることが求められます。 この為、基準となるビデオ同期信号を機器に入力し、その信号を基にビデオクロックを生成します。 詳細は以下をご参照下さい。

*「放映映像向けクロックに最適なクロックジェネレータとは?」 https://emb.macnica.co.jp/articles/13758/

多くの場合、基準となるビデオ同期信号には水平同期信号が使われます。 水平同期信号と、ビデオクロックの周波数は一定の比率を保つことが要求されます。 この比率が少しでも狂うことは許されません。 例として、ハイビジョンシステム(1080P59.98フォーマット)では、水平同期信号と、ビデオクロック周波数の比は1:2200を保つ必要があります。

TICSPRO-SWを使用する際注意すべきこと

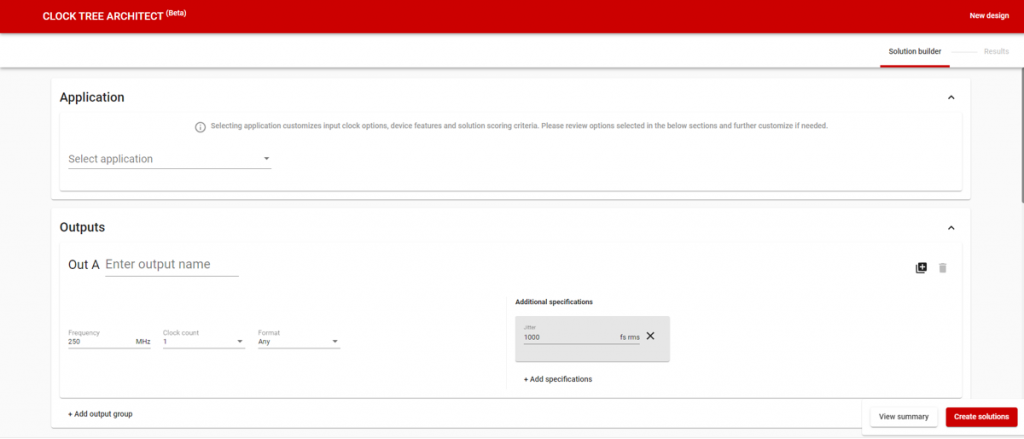

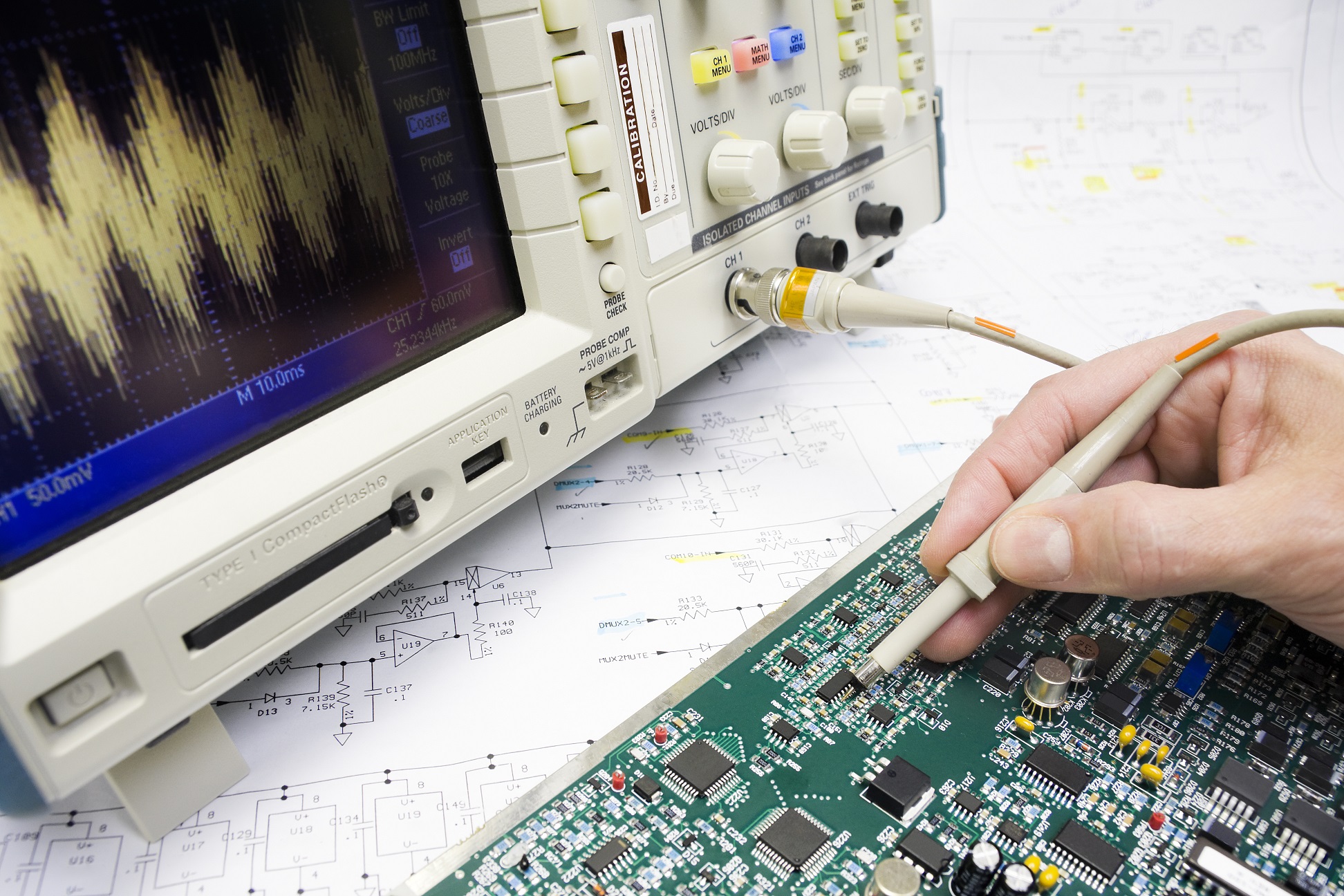

LMK05xxxを使用する際、TICSPRO-SWと呼ぶ、PC上で動くアプリケーションソフトを使用すると、複雑なレジスタ設定を、GUI(Graphical User Interface)を通じて簡単に設定することができます。 TICSPRO-SWを使い、LMK05028で 1080P59.98フォーマットに対応するクロックを生成する手順を見て行きます。 要求されるビデオクロックは 148.5/1.001MHz(148.35164MHz)です。 入力する水平同期信号の周波数は67.5/1.001 kHz(67.432567kHz)です。 図―1はTICSPRO-SWのMain Start Pageです。 以下の手順で設定します。

-

- リファレンス・クロック入力、IN0に水平同期信号の周波数、 67.5/1.001kHzを指定

- OUT0の出力周波数、148.5/1.001MHz(148.35164MHz)を指定

- Update Frequency Planボタンをクリック

- RUN Scriptボタンをクリック

- Reference Input Monitor 項目のIN0 Validationチェックマークを外す

- Main タブのWrite All Registerをクリック

- Main タブのSoft-reset-chipをクリック

図―1. TICSPRO-SWのMain Start Page画面

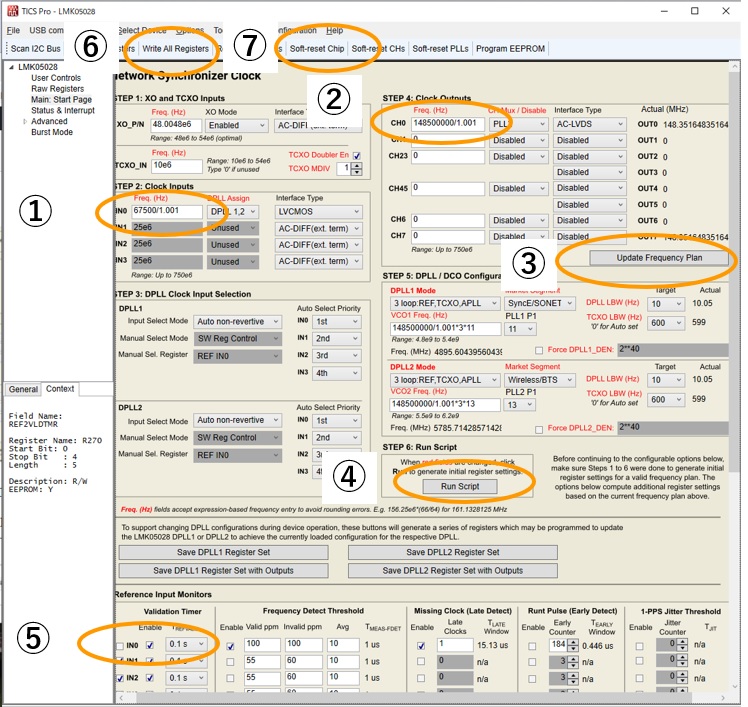

この結果、図―2に示す様に、PLL2 VCO周波数 5785.71428571 MHzが得られ、その出力を13分周し、更に3分周することで148.351648351 MHzが得られます。

図―2. TICSPRO-SWのOutput 画面

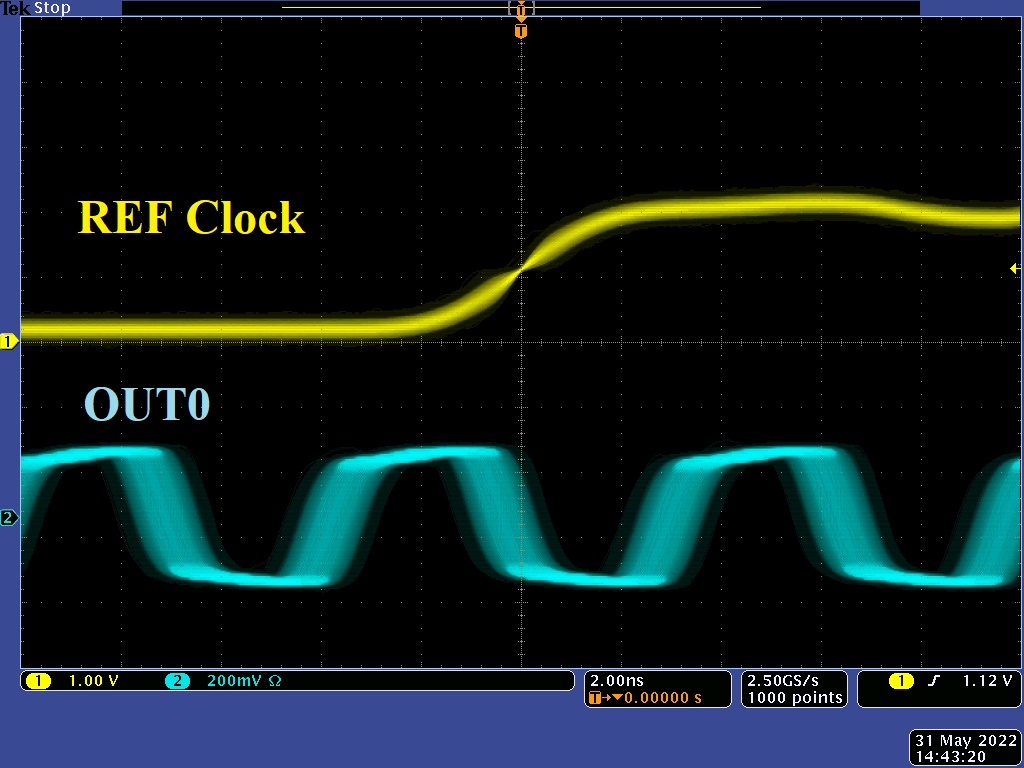

この設定を、LMK05028に書き込み、リファレンス・クロックをトリガーに出力クロックOUT0を観測すると、一見、同期がとれている様な波形を観測できます。 しかし、図―3に示す様に、オシロスコープをパーシスタンス・モードにして、長い時間観測すると、OUT0は時々刻々とずれて行きます。 何故でしょう?

図―3. パーシスタンス・モードで観測した波形

その理由を明らかにして行きます。

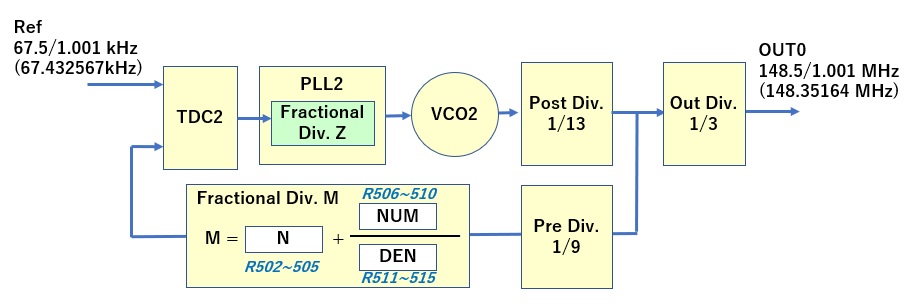

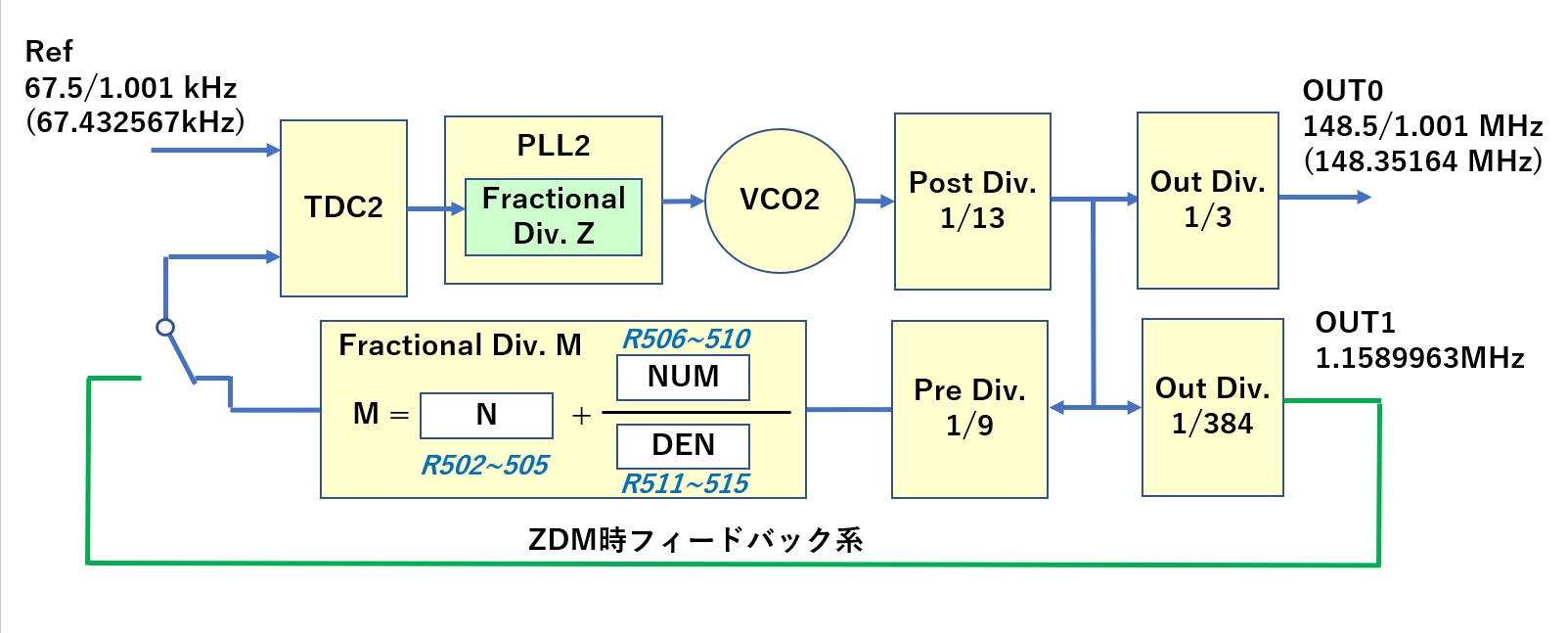

図―4にLMK05028内にあるDPLL2のブロック図を示します。 LMK05028は、リファレンス入力とフィードバックされたクロックの位相を比べ、その結果に応じてPLL2内にあるFractional Div. Zの値を変更します。 これにより、VCO2の周波数を変え、リファレンス入力とフィードバックされたクロックの位相を合わせます。 VCO2の出力はPost Div. (この例では1/13)で分周され、フィードバックされます。 更にPre Div. (この例では1/9)、Fractional Div. Mで分周されDPLLに入力されます。 Fractional Div. Mは帯分数表記で、整数部Nと分子NUM、分母DENで構成されます。

図―4.DPLL2のブロック図

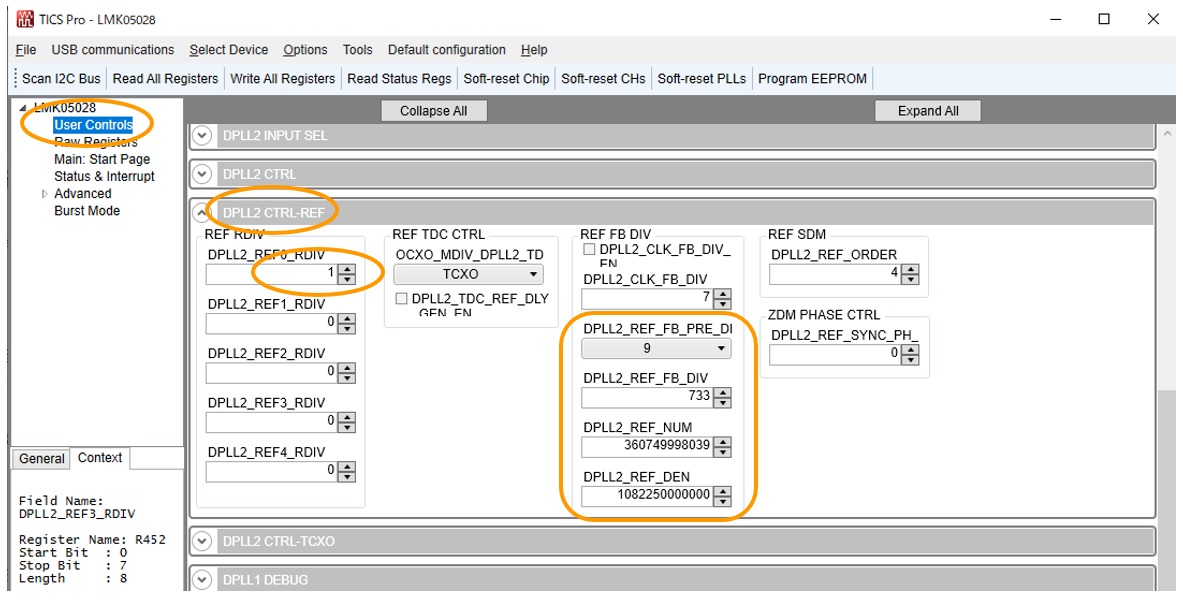

図―5に示す様に、User Control タブでDPLL2 CTRL REF画面を開くと、DPLL2に関する分周関係を確認できます。

図―5.DPLL2 CTRL REF画面

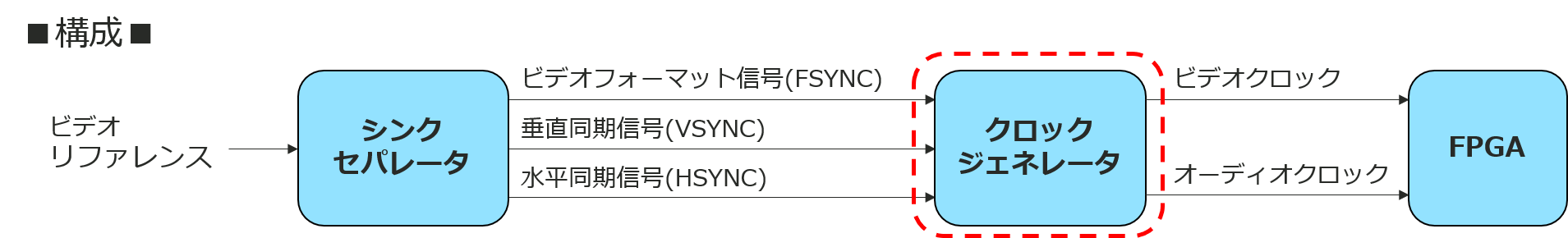

ここで、入出力の比を基に、Fractional Div. Mの各レジスタに設定されるべき期待値を計算します。 入力リファレンス・クロックとして水平同期信号を使用した場合、1080P59.98フォーマットでは1走査線にあるピクセル数は2200個であることから次式が成り立ちます。

Ref *2200 = OUT (1)

出力クロックはVCO2を13分周後更に3分周するので以下の関係が成り立ちます。

OUT*13 *3 = VCO2 (2)

(1)(2)式から

Ref * 2200 = VCO2/13*3 (3)

また、以下の関係も成り立ちます。

VCO2/13*9* M = Ref (4)

(3)のRefに(4)の左辺を代入して、Mを求めます。

(VCO2/13*9* M) *2200 = VCO2/13*3 (5)

M = 2200 / 3 (6)

= 733 + 1/3

上記結果から各レジスタ群は以下の値であるべきことが分かりました。 NUMとDENは、比率を保てば、必ずしも1、3である必要はありません。

N = 733

NUM = 1

DEN = 3

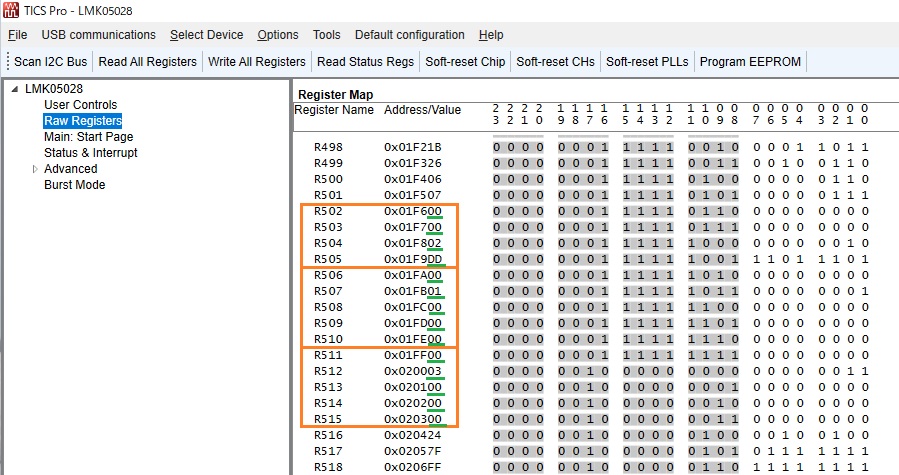

図―5から、NUMには360,749,998,039、DENには1,082,250,000,000が設定されていることが確認できます。 NUMに対するDENの比は、3.000 000 016 307 69です。本来あるべき比、3.0からずれています。 このため、リファレンス入力周波数と、出力周波数の比を正確に、1:2200に保つことはできません。 このわずかな誤差が周波数誤差を引き起こし、累積され、時間経過と伴に位相がズレて行く現象を起こします。 誤差が小さい程、その存在を認識することが難しくなります。 (長い時間をかけて観測しないと検知できない) この対策として、NUMとDENを強制的に書き換えて、正しい比率を保ちます。 DPLL2 CTRL REF画面内で各値を変更したいのですが、現在のTICSPRO-SWでは、この画面で数値を変更することができません。 これらの変数を書き換えるには、図―6に示す様に、Raw Register画面内で行います。

図―6.TICSPRO-SWのRaw Register 画面

DPLL2のFractional Div. M に関するレジスタを表―1に示します。 それらは、R502~R516にマッピングされています。 DPLL2のNはレジスタAddress R502からR505に、MSBから順に、8ビット毎に、30ビット割り当てられます。 NUMはレジスタAddress R506からR510にMSBから順に、8ビット毎に、40ビット割り当てられます。 DENはレジスタAddress R511からR515にMSBから順に、8ビット毎に、40ビット割り当てられます。

表―1.DPLLのFractional Div. Mに関係するレジスタ情報

周波数精度の観点からは、NUMとDENは、その比を、正確に1:3を保てば幾つでも構いません。 他方、ジッタ性能の観点からは、NUMとDENはできるだけ大きな値が望まれます。 なぜなら、Fractional タイプのPLLではDigital Boundary Spurが生じ、ジッタ性能を低下させるからです。 NUMとDENが大きな程、Digital Boundary Spurの影響を低減できるからです。 例として、NUM = 0x0100 0000、DEN =0x300 0000 を設定します。

この問題は、ツール(TICSPRO-SW)のバグではなく、ツールの設計意図と、アプリケーション側からの要求のズレに起因するものです。 本来のTICSPRO-SWの目的は任意の周波数のリファレンス・クロックから、任意の周波数のクロックを生成することです。 両者の正確な比を維持する様には設計されていません。 TICSPRO-SWがFractional Div. Mの値を計算する際、有限長の桁数で計算するので、量子化誤差が生じるためです。 電卓で 1÷3x3を計算すると、結果が0.9999になることと同じです。 放送用映像機器用途を含め、アプリケーションにより、両者の正確な比を維持する必要がある状況では、システム設計者はこの点考慮頂く必要があります。

ZDM (Zero Delay Mode)の必要性

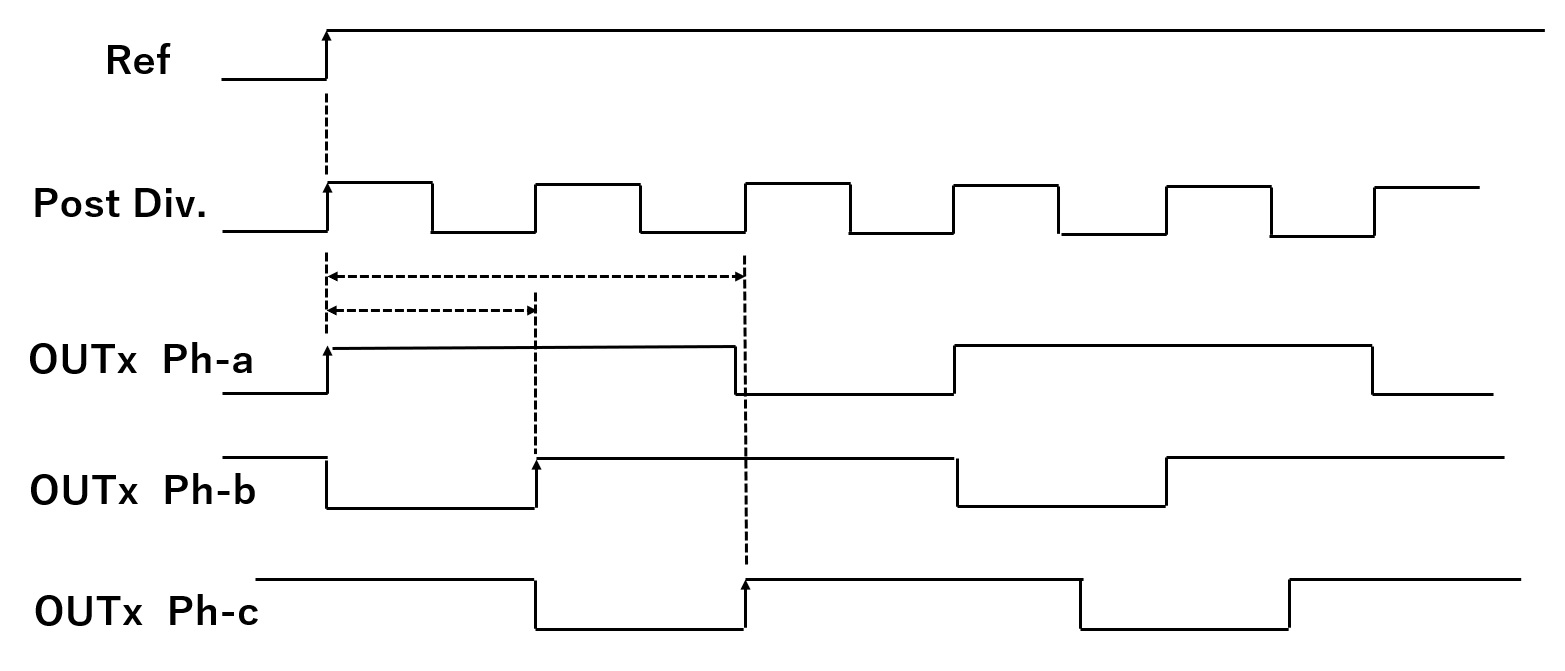

放送用映像機器では、リファレンス・クロックとして使用するビデオ同期信号の周波数とビデオクロックの周波数は一定の比率を保つことが重要と言うことを説明しました。 これに加え、この分野では、リファレンス・クロックとして使用するビデオ同期信号と、出力されるビデオクロックの位相を合わせることが求められることもあります。 この場合、LMK05028に備わった、ZDMを使用します。ZDMはリファレンス・クロックと出力クロック(OUT0)の位相を合わせる機能です。 通常モード時、LMK05028はVCOクロック(Post Div.後)とリファレンス・クロックの位相は一致します。 しかし、出力クロックは出力デバイダにより分周されるので、リファレンス・クロックの位相に対し出力クロックの位相は一意に決まりません。 なぜなら、 図-7のOut x Ph-a~OutxPh-cが示す様に、 Out Div.で分周されたクロックの位相はOut Div.の分周比の数だけ存在するからです。 これら異なる位相を持つクロックの中で、どの位相のクロックがOut Div.から出力されるかはOut Div.の初期値に依存しますが、Out Div.の初期値は管理できません。

図―7.リファレンス・クロックとOUTxとの位相関係

リファレンス・クロックと出力クロックの位相を合わせたければ、LMK05028が持つ、ZDMを使用します。 ZDMに設定するには以下の手順に従います。

- リファレンス・クロックと出力クロックの分周比に従いREF_DPLL modeに設定

- SOFT RESETコマンドを発行

- DPLL がロックするまで待つ

- SYNC_SW controlをトグルする (R12 Bit 6=‘1’、Bit 6=‘0’)

- ゼロディレイにしたい出力クロックを選択 (DPLL1 R84 Bit[5:3]、DPLL2 R84 Bit [2:0]) DPLL1はOut4~7、DPLL2はOut3~0 を選択可

- ZDM modeに切り替え (DPLL1 R594 Bit 0=‘1’、DPLL2 R610 Bit 0=‘1’)

図―8にZDMを含めたDPLLのブロック図を示します。 ZDMでは、図―8に示す様に、緑色の信号経路を通って、出力クロックをTDC(Time to Digital Convertor)にフィードバックします。 TDCでは、フィードバックされた出力クロックとリファレンス・クロックとの位相比較を行います。 Fractional Div. M等は経由しません。 このため、ZDM使用時には、次の2点に注意点が必要です。

第1は、TDCが処理できる最大レートが26MHz以下と言うことです。 今回の例では、OUT0は148.5/1.001MHzです。 この場合、TDCの対応可能な上限を超えます。 そこで、図―8に示す様に、OUT1をZDMのフィードバックに使用します。 OUT1はZDMを使用しリファレンス・クロックと出力クロック(OUT0)の位相を合わせる目的で設置しています。 OUT1では、Out Div.値を追加し、例えば、本来3であるべきOut Div.値を384(128*3)とします。 これにより、TDCに入力されるクロック周波数は(148.5/1.001MHz) /(384/3) = 1.1601562 / 1.001MHzとなり、動作可能範囲に収まります。

第2は、リファレンス・クロックと、フィードバックされた出力クロックは1/K(Kは任意の整数)の関係を維持する必要があると言うことです。 繰り返しになりますが、ZDMでは、図―8に示す様に、緑色の信号経路を通って、出力クロックをTDC(Time to Digital Convertor)にフィードバックします。 ZDMでは、通常のDPLLモードにあった、Fractional Div. Mはバイパスされます。 ZDMでは、リファレンス・クロックが遷移する度に、フィードバックされた出力クロックとの位相を比較し、その位相を合わせるように動きます。 1/Kに分周された出力クロックとリファレンス・クロックの位相を揃えるフィードバックループと見なすことができます。 このことから、ZDMを正しく動作させるには、リファレンス・クロックと、フィードバックされた出力クロックは1/K(Kは整数)の関係を維持する必要があります。

図―8.ZDMを含めたDPLLのブロック図

まとめ

LMK05028 ネットワーク・シンクロナイザーはネットワーク機器用途の他、放送用映像機器にも最適なデバイスです。 しかし、 放送用映像機器用途特有の事情からトラブルに直面することがあります。 そこで、起き得る問題と、その回避方法について解説しました。 本書を参考に、事前に問題を回避し、速やかなシステム開発にお役立て頂ければ幸いです。