- 公開日:2018年06月12日

- | 更新日:2025年10月17日

DCDCコンバータのスナバ回路、流用していませんか?

- ライター:QT

- 電源

はじめに

DCDCコンバータのスイッチングノードとGNDの間に直列に接続された抵抗とコンデンサ。何だかよくわからないけど今までの回路に入っていたし、特に問題も起きていないし、今回もそのままで良いか・・・

ちょっと待ってください!その抵抗と容量はスナバ回路です。スナバ回路にはメリットもありますが、(世の中の多くのものがそうである様に)当然デメリットもあります。最適な回路を設計するために、改めてスナバ回路の設計方法を学んでみませんか?

スナバ回路とは?そのメリットとデメリット

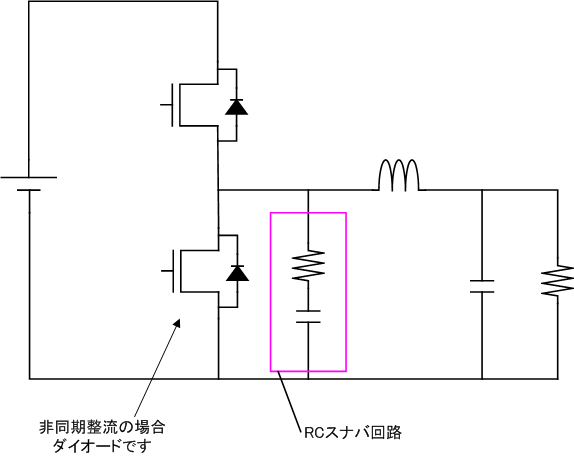

スナバ回路とは、スイッチング回路において発生するリンギングを抑制するための回路で、種類としては、抵抗と容量で構成されるRCスナバ回路、抵抗、容量、ダイオードで構成されるRCDスナバ回路等があります。この記事では非絶縁DCDCコンバータで一般的なRCスナバ回路について記述します。

図 1 RCスナバ回路

DCDCコンバータにおいて、スナバ回路はスイッチングノードとGND間に接続され、原理としては高周波成分のエネルギーを抵抗に消費させる事でリンギングを吸収します(入力電圧が大きい、もしくはスイッチング周波数が高い場合は、スナバ抵抗で結構な電力が消費される事があるため、注意が必要です)。但し、抵抗をスイッチングノードに直接接続してしまうと、抵抗で定常的に電力が消費されてしまうため、容量を直列に接続する事で低周波成分をカットしてしまいます。

上記の通り、リンギングは熱に変換される事で抑制されます。つまり、回路としては損失が増え、効率は悪化する傾向となります。また当然ながら部品点数が増えてしまうため、コストや基板面積に多少なりとも影響を及ぼします。

スナバ回路追加を検討する前に

上記の様にスナバ回路を追加すると必ず損失が増えてしまうため、できればスナバ回路は無い方が好ましいです。スナバ回路を入れる前に、スナバ回路を搭載しなくても良くなるように、まずは基板のレイアウトを最適化して、リンギングを最小限に留める様にしていただければと思います。

※レイアウト最適化の記事は今後公開予定です。

スナバ回路の定数設計方法

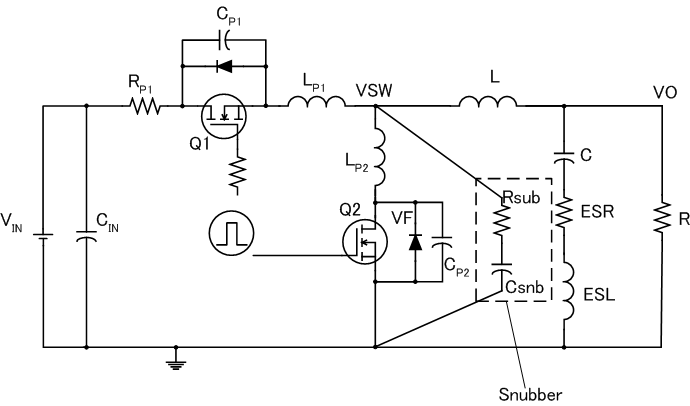

それでは、スナバ回路の設計方法に移ります。スナバ回路は、FET、ダイオードや基板の配線による寄生成分を基に設計されます。寄生素子を含めたDCDCコンバータの回路図を以下に示します。

図 2 寄生成分を含めたDCDCコンバータ回路図

図 2 寄生成分を含めたDCDCコンバータ回路図

手順は以下の通りです。

1.初めに、デフォルト状態で発生しているスイッチング波形のリンギング周波数f0を計測します。

2.スイッチングノード-GND間に容量C1を追加し、リンギングの周波数f1を測定します。

この時、f1がf0の50%~75%程度になる様にC1の値を調整ください。

C1は目安として100pF程度から初めていただければと思います。

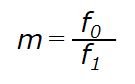

3.以下式より、f0とf1の比を算出します。

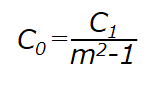

4.以下式より、寄生容量値C0を算出します。

4.以下式より、寄生容量値C0を算出します。

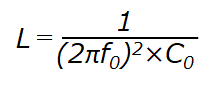

5.以下式より、寄生インダクタンス値Lを算出します。

6.以下式より寄生成分による特性インピーダンスを求め、その値がスナバ抵抗の目安値となります。

(抵抗で消費するエネルギーを最大化するため、スナバ抵抗と特性インピーダンスを合わせます)

7.スナバ容量は、スナバ容量とスナバ抵抗値で構成されるHPFのカットオフ周波数がリンギング周波数より十分小さくなる様に設定する必要があります。

C0の3倍の容量値がスナバ容量の目安となります。

部品選定時の注意点として、先程も少し触れましたが、スナバ抵抗での消費電力を考慮する必要があります。

スナバ抵抗での消費電力は以下式より求められますので、求められた電力に十分耐えうる抵抗を選定する必要があります。

![]()

また、スナバ回路に対して寄生インダクタンス成分があるとリンギング抑制効果が弱まってしまうため、なるべくスナバ回路をローサイドFET(もしくはダイオード)のそばに配置する必要があります。ですので、スナバ回路を使用するかは別として、レイアウト設計の段階でパターンだけでも準備しておく事を推奨します。

実際にスナバ回路を設計し、効果を確認してみた

上記の手順にてTexas Instruments社の評価基板 TPS53319EVM-136を使用してスナバ回路を設計してみました。動作条件は以下の通りです。

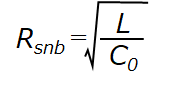

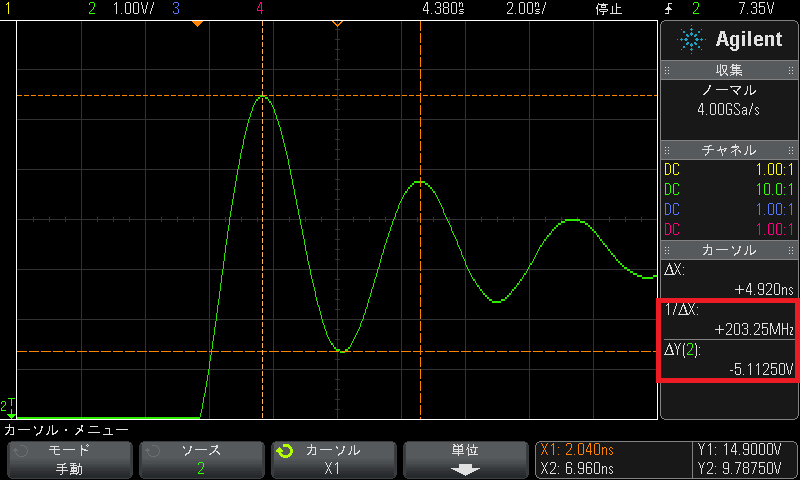

まず、現状のリンギングの波形を観測した所、周波数は203.25MHz、レベルは6.05Vppでした。

図 3 デフォルト状態でのリンギング波形

図 3 デフォルト状態でのリンギング波形

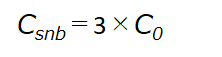

次にスイッチングノード-GND間に容量を追加し、リンギングの周波数を測定しました。

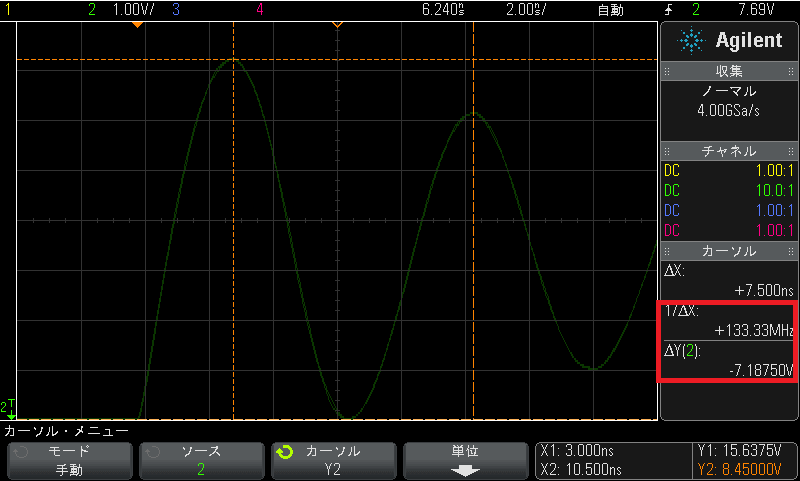

初めに100pFを追加して測定したのですが周波数の変化が小さかったため、C1=470pFを追加して周波数を測定した所、133.3MHzとなりました。

図 4 C1として470pF追加したときのリンギング波形

図 4 C1として470pF追加したときのリンギング波形

これらの結果より、寄生容量値C0が352pF、Lが1.7nHとなり、特性インピーダンスが2.2Ωとなりましたので、スナバ抵抗を2.2Ω、スナバ容量を1500pFに決定しました。

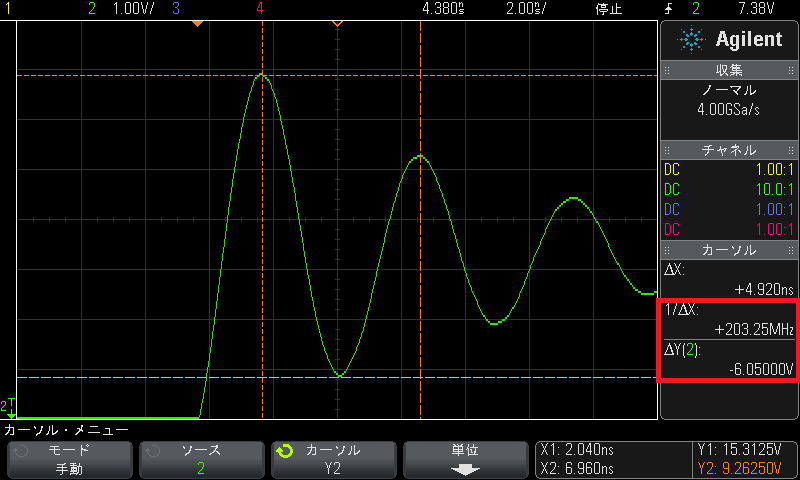

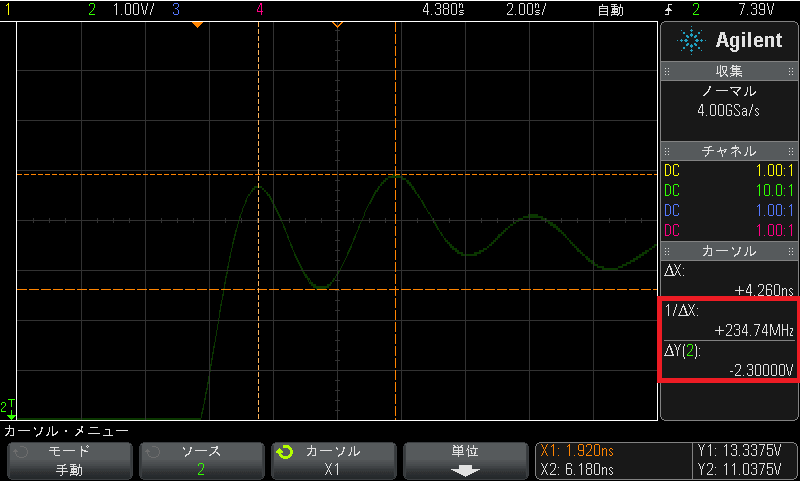

その時の波形が以下となります。

図 5 スナバ抵抗2.2Ω、スナバ容量1500pFを追加したときのリンギング波形

図 5 スナバ抵抗2.2Ω、スナバ容量1500pFを追加したときのリンギング波形

上記波形の通り、Vpp=2.3Vまで低減する事ができました。

試しにスナバ抵抗を22Ωとしたときの波形がコチラです。

図 6 スナバ抵抗22Ω、スナバ容量1500pFを追加したときのリンギング波形

図 6 スナバ抵抗22Ω、スナバ容量1500pFを追加したときのリンギング波形

Vpp=5.11Vとなりました。リンギング低減はできておりますが、効果としては最適化できていない事がわかるかと思います。

ちなみに、この設定値での消費電力は500pF*12^2*400kHz=8.64mWとなります。

まとめ

今回はスナバ抵抗の設計方法について紹介させていただきました。スナバ回路を使用する前に、まずはレイアウトが最適化できているかどうかの確認が必要です。レイアウトでの改善余地がなかった場合はご紹介した手順でスナバ回路を設計し、適切な定数でリンギングを抑制していただければ思います。設計時の参考になれば幸いです。

Texas Instruments社の製品をお探しの方は、メーカーページもぜひご覧ください。

Texas Instruments社

メーカーページはこちら

関連情報