- 公開日:2024年06月28日

- | 更新日:2024年07月17日

スイッチ素子の発熱量を予測、MOSFETのスイッチング損失算出方法

ある客様からこんなお声を頂きました。

「電源ICを変更したらMOSFETが以前の回路より熱くなった。効率も下がった。これってICが悪いの?それともMOSFET?」

結論を言ってしまうと どっちも ですね。

確認したところ、電源ICの変更に伴い、LとCは小型化、スイッチング周波数(以下fsw)が大幅に高速化していました。

このfswの高速化により、MOSFETでの損失が増大していました。

本記事では、スイッチング周波数と、MOSFETの損失の関係を解説します。

MOSFETの損失

MOSFETにおける電力損失は、以下の種類があります。

- MOSFETがターンONするに際発生するON損

- MOSFETがON状態で発生する導通損

- MOSFETがターンOFFするに際発生するOFF損

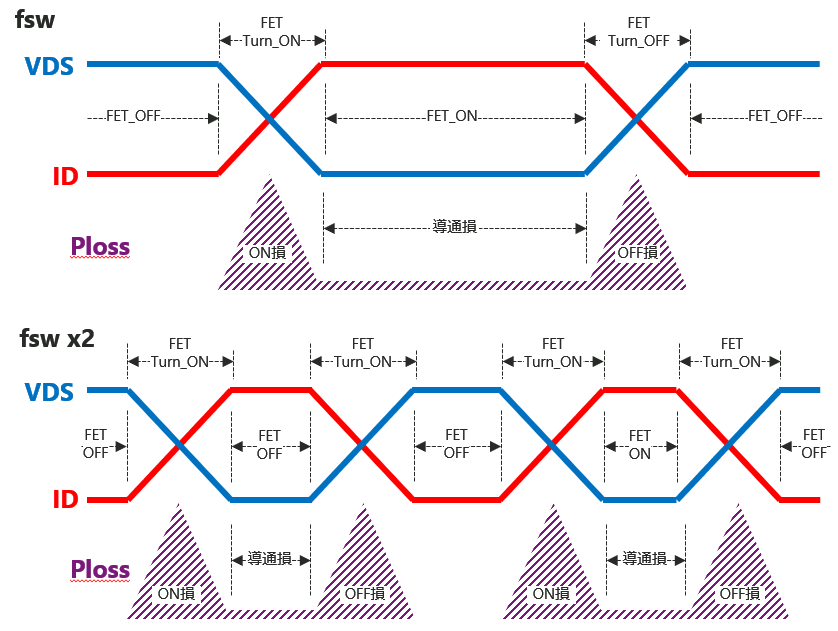

今回の事例では、この1)と3)の割合が大きくなってしまったことが原因です。それぞれの損失を図にしてみました。

イメージし易くするため、周波数が2倍になった場合との比較です。

VDSがHighからLow、LowからHighに遷移する際にも電流IDは流れています。このときに発生するのがON損とOFF損です。このON損とOFF損をまとめてスイッチング損とも言います。

VDSの遷移時間は、使用するICのMOSFETをドライブする能力と、MOSFETのQg(ゲート容量)、Rg(ゲート抵抗)で決定されます。もしVDSの遷移時間が一定であれば、fswが高くなると、単位時間当たりのスイッチング損の割合が大きくなります。

これが、fswの高速化による損失の増加の原因です。

fswを上げることでLとCを物理的に小さいものが使用可能となりますが、それに合わせてVDSの遷移時間が短い(速くスイッチングする)MOSFETを選ぶ必要があります。

スイッチング損の算出方法

では、MOSFETで発生する損失を事前に見積もることはできるのでしょうか?

可能です。 但し、あくまでも近似です。また、VDSとIDとの波形を正しく定義する必要があります。

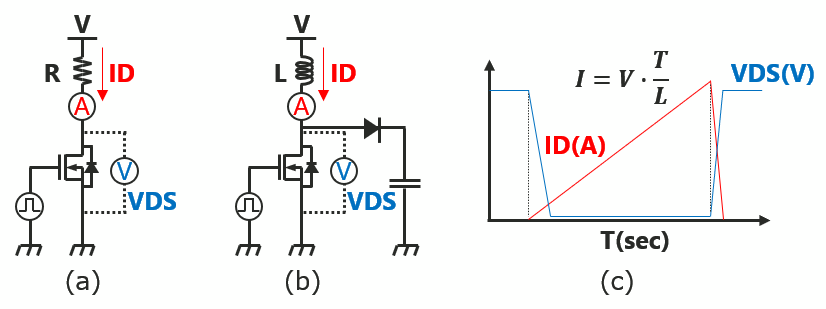

上の図ではMOSFETがONの時、電流が横一直線ですので、図(a)回路であることが読み取れますが、電流をガンガン流す回路でこのような使い方は行いません。そのため、ここではRをLに置き換え、昇圧DC/DCのような図(b)の回路で考察します。

図(b)の回路では、DCM(電流不連続モード)の場合、IDは図(c)の式に従い三角波となります。

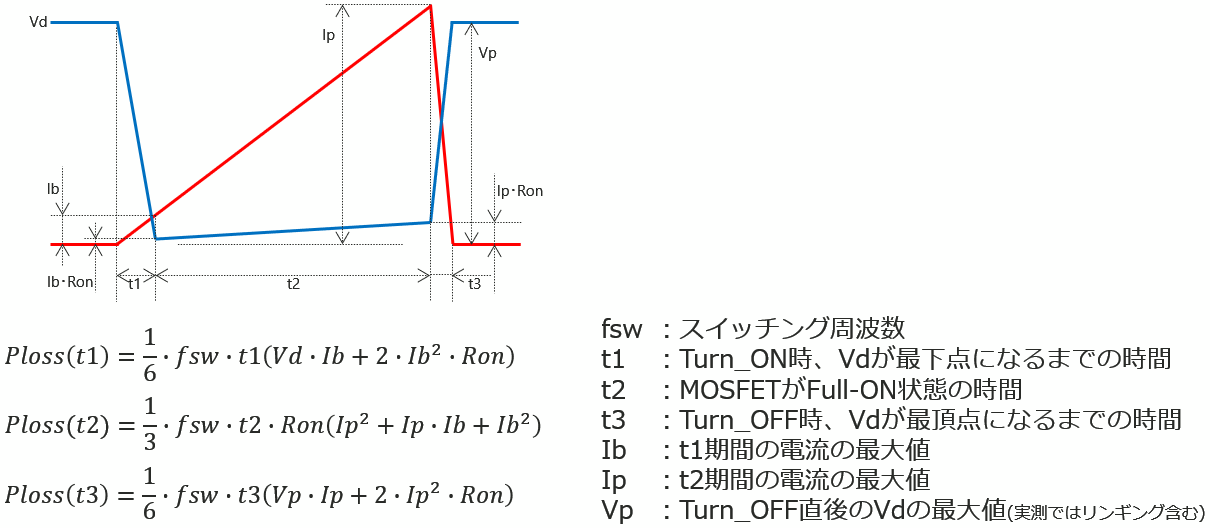

さて、この波形における各損失の計算式は下記の通りです。

VdとVpは理想的には同じ電圧になりますが、回路パターン上に存在する寄生成分によりスイッチングサージが発生するため、実際としてはVd≦Vpとなります。

演算実例

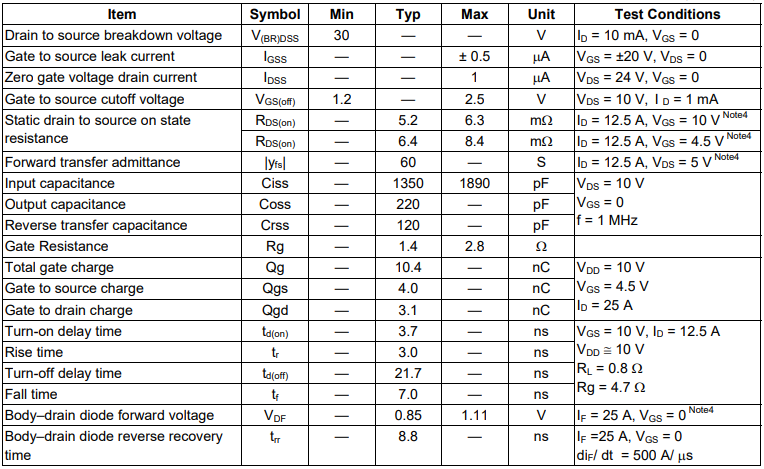

ルネサスエレクトロニクス社のMOSFET、RJK03M5DNSを用いて、損失計算をしてみます。

[ 引用:ルネサスエレクトロニクス RJK03M5DNS データシート ]

Ronは8.4mΩ、Vdは10V、Ipは12.5Aとします。trとtfは10%~90%の時間で定義されておりますので、0%~100%に比例換算すると、tr=3.75nsec、tf=8.75nsecとなります。

図(b)のLは4.7uH、fswは100kHz、Dutyは50%としましょう。Ibは図(c)の式に、Vd,L,tfの各値をそのまま代入し、0.017Aとします。Ronはデータシート記載の最大値である8.4mΩをそのまま使用します。

すると、各パラメータは次のようになります。

fsw :100kHz

t1 :8.75nsec

t2 :4.94usec

t3 :3.75nsec

Ib :0.017A

Ip :12.5A

Vp :10V(今回はリンギング含まない)

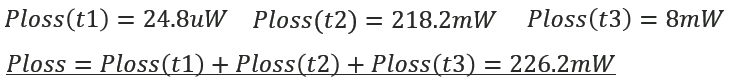

その結果、前述の各Ploss算出の式に代入すると、

となりました。

最後に熱抵抗を加味したジャンクション温度を算出します。

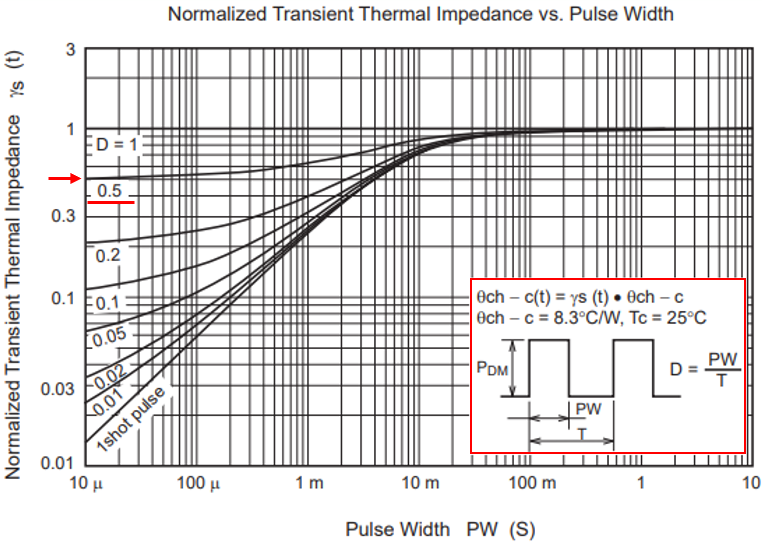

[ 引用:ルネサスエレクトロニクス RJK03M5DNS データシート ]

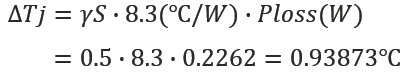

今回の例ではパルス幅は約5usecですが、上図の最小値である10usecに当てはめます。Dutyは50%なので[D=0.5]のカーブが適用できますので、熱抵抗係数[γS=0.5]とすることができます。

熱抵抗は8.3℃/Wなので、MOSFET内部のジャンクション温度の上昇値ΔTjは、

1℃未満 であることが分かります。

今回の例では、fswを100kHzとしており、DC/DCとして用いるには非常に低速です。損失計算の式にはfswが含まれますので、fswが高くなると、

・単位時間当たりの損失が最も小さい導通損(Ploss(t2))が縮小

・tr,tf(Ploss(t1、t3))で発生する損失の割合が増大

となり、効率が低下する可能性があります。また、Ronとtr,tfはトレードオフの関係にあり、Ronが小さいMOSFETはtr,tfが大きくなる傾向にあります。

従って、fswを高くするのであれば、敢えてRonが大きいMOSFETを選定した方が、回路トータルの損失を減らせる場合があります。

実機での損失測定,評価

今回は設計前の机上計算の方法を紹介いたしました。

実機での損失計算は、もっと簡単です。実は、MOSFETの損失はオシロスコープで測定することが可能です。

次回はその手法をお伝えします。

お問い合わせはこちら

ルネサスエレクトロニクス社ではMOSFETの他にもパワーバイポーラトランジスタやパワーIGBTを取り扱っており、市場における様々な設計要件に対し、最適なソリューションを提供しております。

電源設計、高電圧大電流アプリの設計において、お困り事がありましたら、是非弊社へお声がけ下さい。

ルネサス製品をお探しの方は、メーカーページもぜひご覧ください。

【マクニカ ルネサスページはこちら】