- 公開日:2024年08月13日

- | 更新日:2024年08月30日

オープンドレイン出力コンパレータのヒステリシス幅設定方法

- ライター:sato

- その他

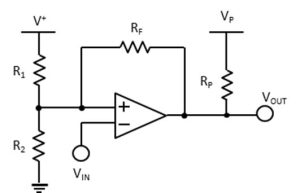

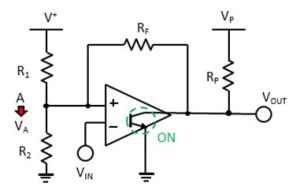

オープンドレイン出力の汎用コンパレータ(μPC177、μPC277など)でヒステリシスコンパレータ回路を

組む場合のヒステリシス幅の設定方法について、お客様よりご質問を良く頂きます。本記事ではその計算方法について、紹介します。

計算結果

まず初めに計算結果を示します。

以下の回路を構成した場合のヒステリシス幅を示します。

■ヒステリシス幅

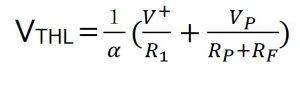

■出力がH→Lに入れ替わるしきい値VTHL

■出力がL→Hに入れ替わるしきい値VTLH

(*1)VOUT:コンパレータの出力電圧,V+:電源電圧など, VP:プルアップ電圧

(*2)今回は入力オフセット電圧や入力バイアス電流などの影響は考慮していません。

(*3)本記事では机上での計算である為、改めて実機での検証も必要となります。

導出方法

本回路はコンパレータの出力状態によって変化するA点(非反転入力端子/IN+)の電位にヒステリシスを生じさせています。

出力状態ごとのA点の電位を求める事によってヒステリシス幅を求めていきます。

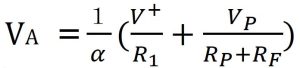

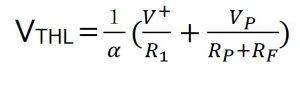

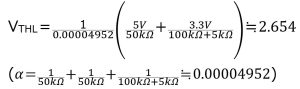

■出力がH→Lに入れ替わるしきい値VTHL

まずは、出力がHigh(H)の際のA点の電位VAを求めていきます。この時のコンパレータの出力トランジスタはOFFに

なっており、電流が流れない状態で計算していきます。

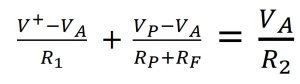

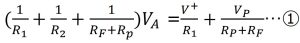

A点に対して、キルヒホッフの第一法則にて電流式を立てます。

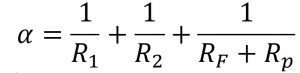

以下の部分をαとして定義する。

式①についてVAについて求めると以下のようになります。

この時のVAがH→Lに入れ替わるしきい値VTHLとなる。

![]()

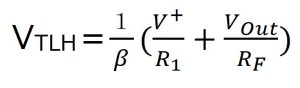

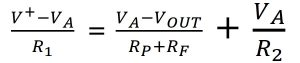

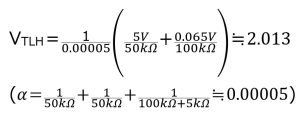

■出力がL→Hに入れ替わるしきい値VTLH

まずは出力がLow(L)の際のA点の電位VAを求めていきます。この場合はコンパレータの出力段のトランジスタはONしており、

電流が流れる状態で計算していきます。

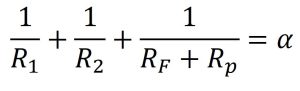

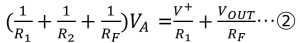

A点に対して、キルヒホッフの第一法則にて電流式を立てます。

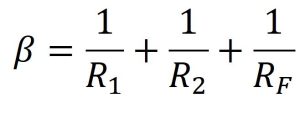

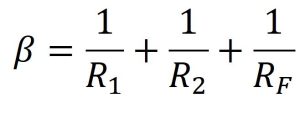

以下の部分をβとして定義する。

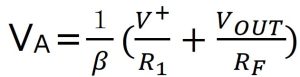

式②についてVAについて求めると以下のようになります。

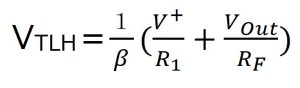

この時のVAがL→Hに入れ替わるしきい値VTLHとなる。

![]()

■ヒステリシス幅

以下のように閾値の差がヒステリシス幅となります。

検証結果

■上記の式に基づいて、計算してみた。

R1=50kΩ, R2=50kΩ, RF=100kΩ, RP=5kΩ, VP=3.3V, V+=5V,VOUT=0.065mVとして

実際にヒステリシス幅を計算結果を記します。

出力がH→Lに入れ替わるしきい値は以下になります。

出力がL→Hに入れ替わるしきい値は以下になります。

上記結果よりヒステリシス幅は0.641Vとなります。

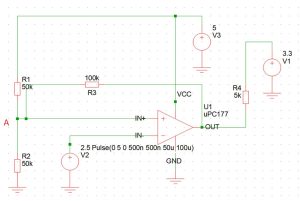

■回路シミュレータisim:PEで検証

ルネサスが提供している回路シミュレータisim:PEを使用して、ヒステリシス幅を確認します。

ダウンロードは以下のURLからお願いします。

isim:PEで記載した回路は以下になります。

(*)入力(IN-端子)には0 to 5Vの矩形波入力。

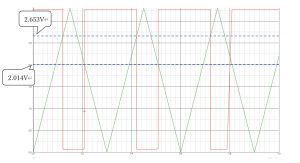

シミュレーション結果は以下の通り、出力の切り替わりに応じて、

A点の電圧が切り替わっており、ほぼ上記の計算通りの結果が得られています。

(*)赤色の波形:コンパレータ出力、緑色の波形:入力電圧(IN-端子電圧)波形

まとめ

上記の計算式よりヒステリシス幅を設定し、シミュレーションでも検証することができました。

ルネサスエレクトロニクス社では、汎用のコンパレータ以外にも低消費や高速など用途に合わせた

様々なコンパレータラインアップを提供しております。ぜひ、コンパレータを始めとする

アナログ回路全般で困り事がありましたら、是非弊社へお声がけ下さい。

ルネサス製品をお探しの方は、メーカーページもぜひご覧ください。