- 公開日:2024年09月30日

ECC(Error Checking and Correcting)機能の動作

はじめに

昨今、半導体の微細化が進むにつれ、揮発性メモリでの「ソフトエラー」を懸念する声をよく聞きます。

「ソフトエラー」の発生は、

従来は半導体パッケージ材料:モールド樹脂にごく微量に含まれる放射性同位元素から発生するアルファ線(α線)が主因でしたが、現在は地球外から降り注ぐ宇宙線起因の高エネルギー粒子、特に中性子によるソフトエラーが顕在化しています。

中性子線は遮蔽が困難である為、揮発性メモリでの「ソフトエラー」の発生は避けて通れない事象と言えます。

この様に「ソフトエラー」発生は避けられない事象である事から「ソフトエラー」発生においてもシステムが誤動作しないようにシステムでは各種対策を行っております。

この対策の一つとして揮発性メモリにECC回路を付加する手法がありますが、昨今のMCUではSRAMにECC機能をサポートする多くの製品がリリースされています。

今回はこのECC回路の動作についてご説明いたします。

1.ECC機能におけるエラー検出/訂正の仕組み

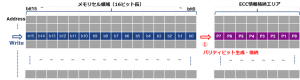

ECC機能対応メモリエリアにデータを書き込むと、データに対する下図の様にパリティビットを生成・格納されます。

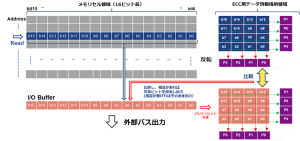

一方、ECC機能対応メモリエリアからデータの読み出すと、読み出したデータに対して書き込み時と同様に8ビットのパリティビットを生成します。その後、その「読み出し時に生成したパリティビット」と「書き込み時に生成したパリティビット」と比較し、相違があった場合、対象ビットを反転出力し、訂正されたデータ(正規のデータ)を外部バスに出力します。(相違がなければ、正常データとしてそのままメモリセルの外部バスに出力にします。)

このパリティビットの生成は16ビット長のデータに対し、下図の様に4ビット毎に8個の①パリティビットを生成・格納します。

(備考)本生成方式イメージを分かりやすくする為、8個のパリティビットの生成の一例ですが、最適化は可能です。

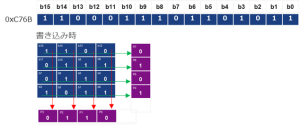

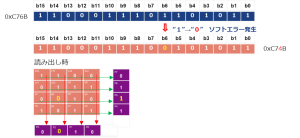

例えばあるアドレスに0xC76Bを書き込んだ時、下図の様にP7~P0にパリティビットが生成されます。

例) ”1”, ”0”, ”1”, ”1” →Px=”1”

2.ソフトエラー発生時のECC機能動作

データ=0xC76Bを書き込み時、パリティビットは以下の様に生成・格納されます。

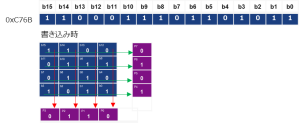

ここでbit6においてソフトエラーが発生していた場合、読み出し時に生成されたパリティビットと相違が発生します。

書き込み時のパリティと読み出し時のパリティを比較すると “P5”、“P2”に相違がある事から“b6”にソフトエラーが発生した事

が把握できます。

このb6の “0“データをメモリセルから外部バスに出力するI/O Buffer上で”1”に反転(エラー訂正)し、メモリセルの外部バスに0xC74B→0xC76Bと訂正してデータを出力します。

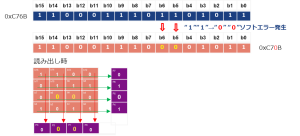

また、2bitのソフトエラー発生においてはエラーが発生した事は判りますが、下図の様にエラービットを特定できず、訂正する事はできません。

P2,P1から2bit以上のソフトエラーが発生した事は判りますが、 P7~P4のどのラインで発生したか判別できません。

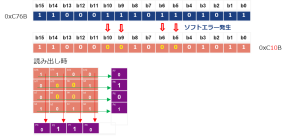

尚、対象データに対し、3bit以上のエラー発生時にはエラー発生の場合、所定のエラー検知もできない場合があります

ここではソフトエラーが発生し、書き込み時と4ビット分のデータが反転していますが、読み出し時のパリティビットからエラーを検知できず、そのままエラーデータを出力してしまい、システムが誤動作となる可能性があります。

まとめ

以上の様にECC機能搭載により、ソフトエラー発生時(1bit エラー時)においても正規のデータを読み出すことができる様になります。

但し、ここでの注意点としては正規のデータを読み出せたとしても、メモリセル内にあるデータはエラー状態を保持しています。この為、更にソフトエラーの影響を受け、多ビットエラーとなりデータを修復できなくなる可能性を秘めている事になります。

従って、対応としてはECC機能が働いた事を検知した時、対象アドレスにライトバックする等、ソフトエラー状態を回復させる必要があります。尚、ECCエラーの発生を検知できないシステム構成の場合は、確率論になりますが定期的に重要データに対してリフレッシュ(ライトバック)をする事も有効な手段です。

お問い合わせ

以上