- 公開日:2025年04月03日

- | 更新日:2025年04月17日

ルネサス製品ForgeFPGAの評価ボードを使ってロータリエンコーダを動かしてみた

- ライター:Hideyuki Naruhashi

- プロセッサー

背景

日頃より、現在ご使用中のCPLDをもっと安価で低消費電力のICに置き換えたい、または、GreenPAKよりもう少しだけ容量があるといいのにな、、といったお客様はForgeFPGAにきっとご興味を頂けていると思います。しかし、開発環境の立ち上げから始まり、評価ボードを実際にどうやって動かしたらよいかわからないので、ちょっと検討は後で。。と思われているお客様もおられるかと存じます。そのようなお客様に向けて、ForgeFPGAはこんなに簡単に開発環境を立ち上げることができ、評価ボードを動かせるんだというクイックなスタート方法をご案内できればと思い、本技術記事を作成致しました。

製品概要

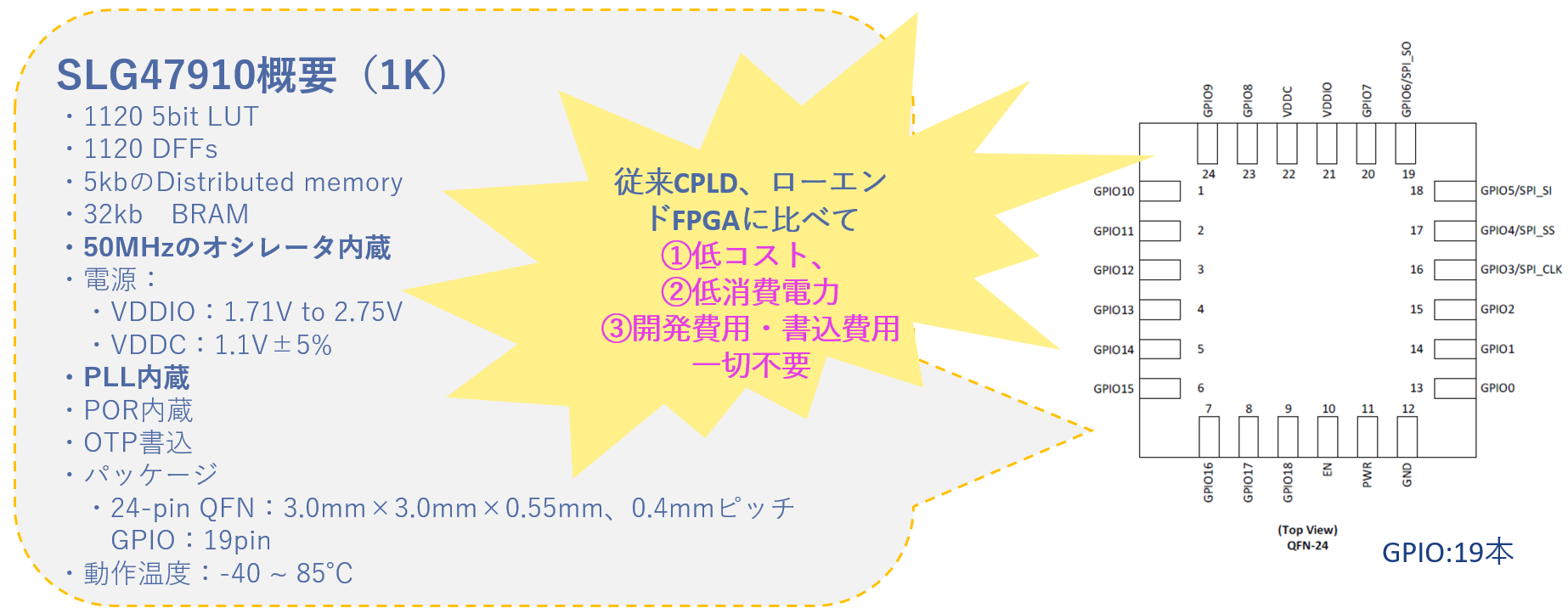

ForgeFPGAとは。

ルネサスエレクトロニクス社がローエンドFPGA市場に参入するために打ち出した製品ファミリです。10Kゲート以下のロジックを必要とするアプリケーションに向けて、低消費電力かつ低価格なFPGA製品群を、順次ご提供していく予定です。その第一段階として、1K個のルックアップテーブルの製品が24年6月に正式リリースされました。

★強み・特徴★

従来のCPLD、ローエンドFPGAに比べてForgeFPGAは

①低コスト、②低消費電力、③開発費用、書き込み費用が一切不要

が大きな強み・特徴となります。

・URL SLG47910 – 1K LUT ForgeFPGA | Renesas

次に、内部ブロック図を見ていきましょう。

50MHzのオシレータやPLLを内蔵していることに加え、384kBのOne Time Programメモリ(OTP)を内蔵しており、FPGAの接続情報やマクロセルの設定といったデータをIC内部のメモリに格納しています。発振器やコンフィグレーションメモリなどは、従来のFPGAでは外付け部品として必要だったものですが、ForgeFPGAはこれらを内蔵することで、BOMコスト低減を実現します。

開発ツール

ソフトウェアとハードウェアの必要な環境は下記の通りです。

<ソフトウェア環境>

・Go Configure Software Hub ・・GUIエディタ。ファイル生成やVerilogコーディング用

・Icarus Verilog ・・波形シミュレーション用アプリ( GTKwave )

・サンプルコード ・・ルネサスが提供するサンプルプログラム または、 Git Hubのフリーソフトプログラム

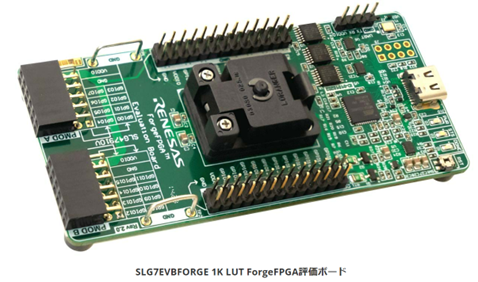

<ハードウェア環境>

・SLG7EVBFORGE ・・ForgeFPGA評価用ボード

・モバイルPC

SLG7EVBFORGE Renesas / Dialog | Mouser Japan

開発環境の事前準備(必要ツールのインストール)

1.Go Configure Software Hubをインストールしよう

開発環境であるGo Configure Software Hubを下記をクリックしてインストールしましょう!

Go Configureソフトウェアハブ | Renesas ルネサス

ディスクトップに↑のアイコンが表示されればインストール完了です。

なんとライセンス費用等、一切不要です!

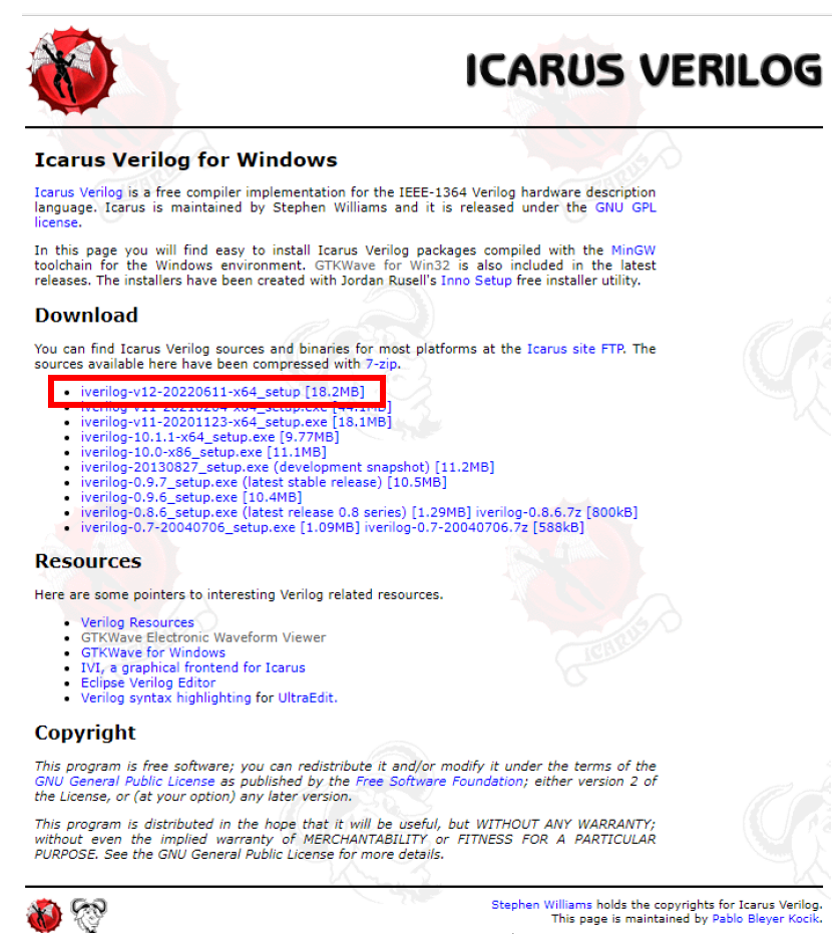

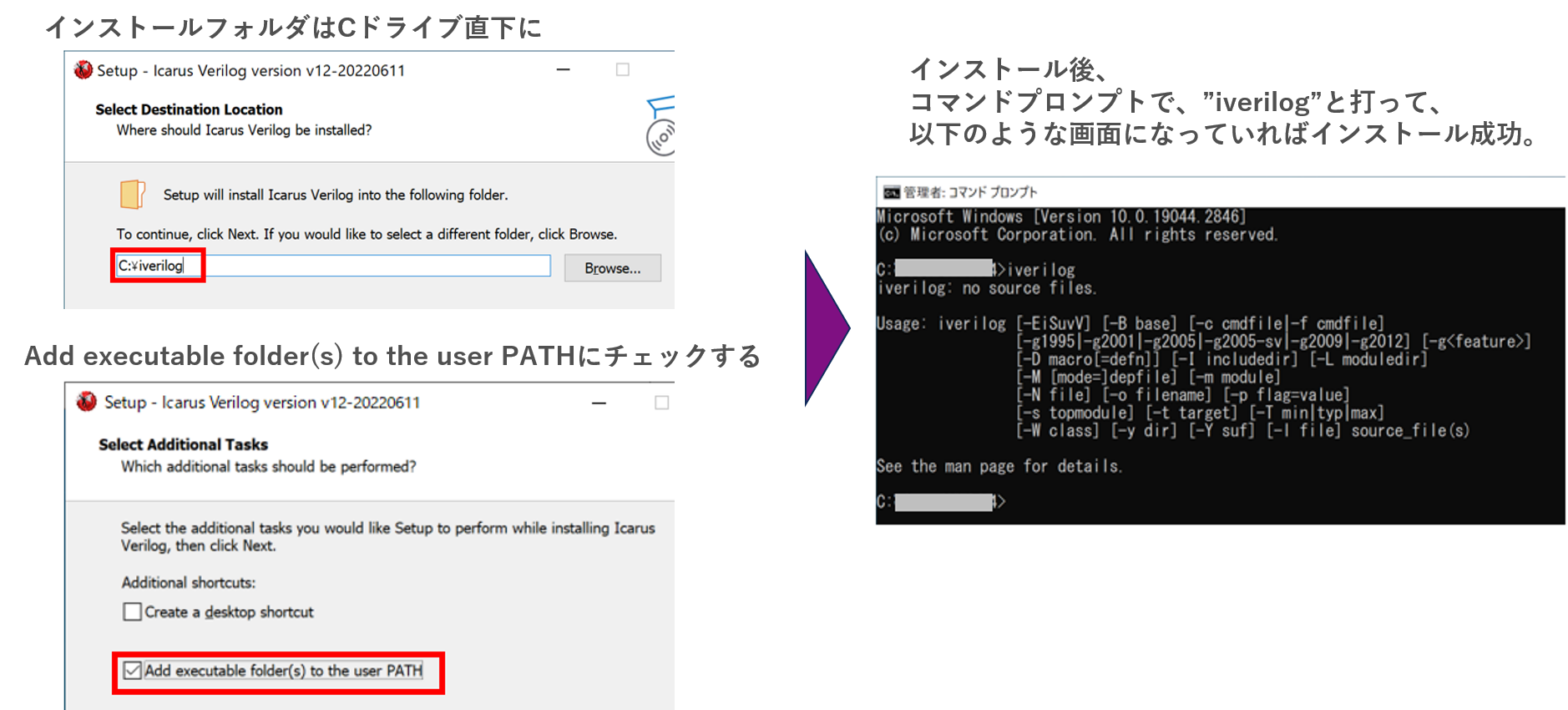

2.Icarus Verilogをインストールしよう

次にIcarus Verilogをインストールしましょう。こちらは、ForgeFPGAで作ったプログラムをシミュレーションする際の

GTKwave立ち上げ時に必要なソフトウェアになります。

Icarus Verilog for Windows (bleyer.org)

Webにジャンプしたら、下記の赤枠をクリックしインストールを進めてください。

Icarus Verilogをインストールの際の注意事項は下記の通りです。

開発環境の立ち上げ

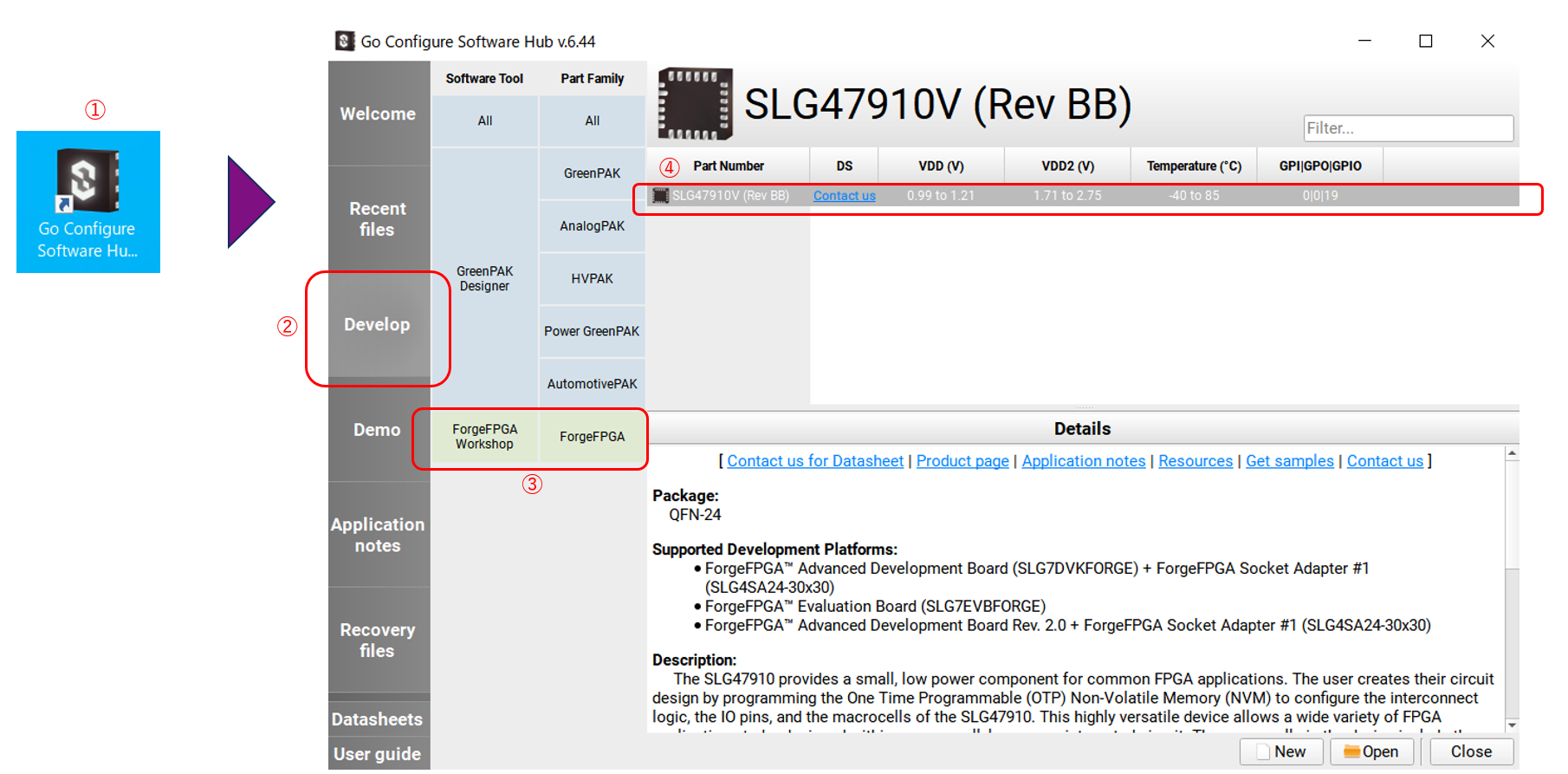

さあ準備が整ったら、いよいよ開発環境GUIを立ち上げましょう!

まず下記の①のアイコンをクリックしてください。すると、Go Configure Software Hubが立ち上がります。

ここで②、③、④の順にクリックしてください。ForgeFPGAのICであるSLG47910(RevBB)を選択できます。

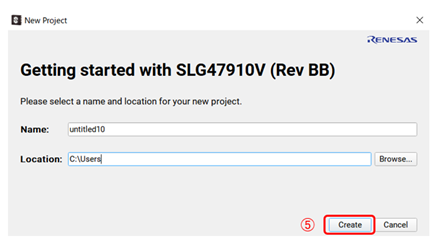

更に進めると下記のような表示になりますが、赤枠の番号をどんどんクリックして進めてください。

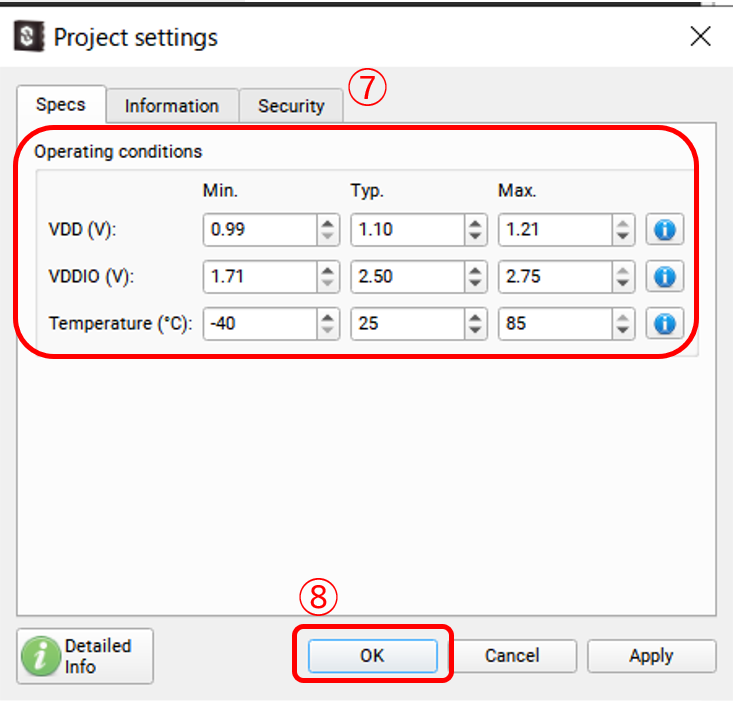

VDDを設定する画面が登場しますが、N/Dの右横の矢印の上を押すと最大値に変化しますので、順番にN/Dをすべて最大値に設定ください。

完了すると赤枠の⑦のようになります。ここで⑧の通りOKをクリックします。

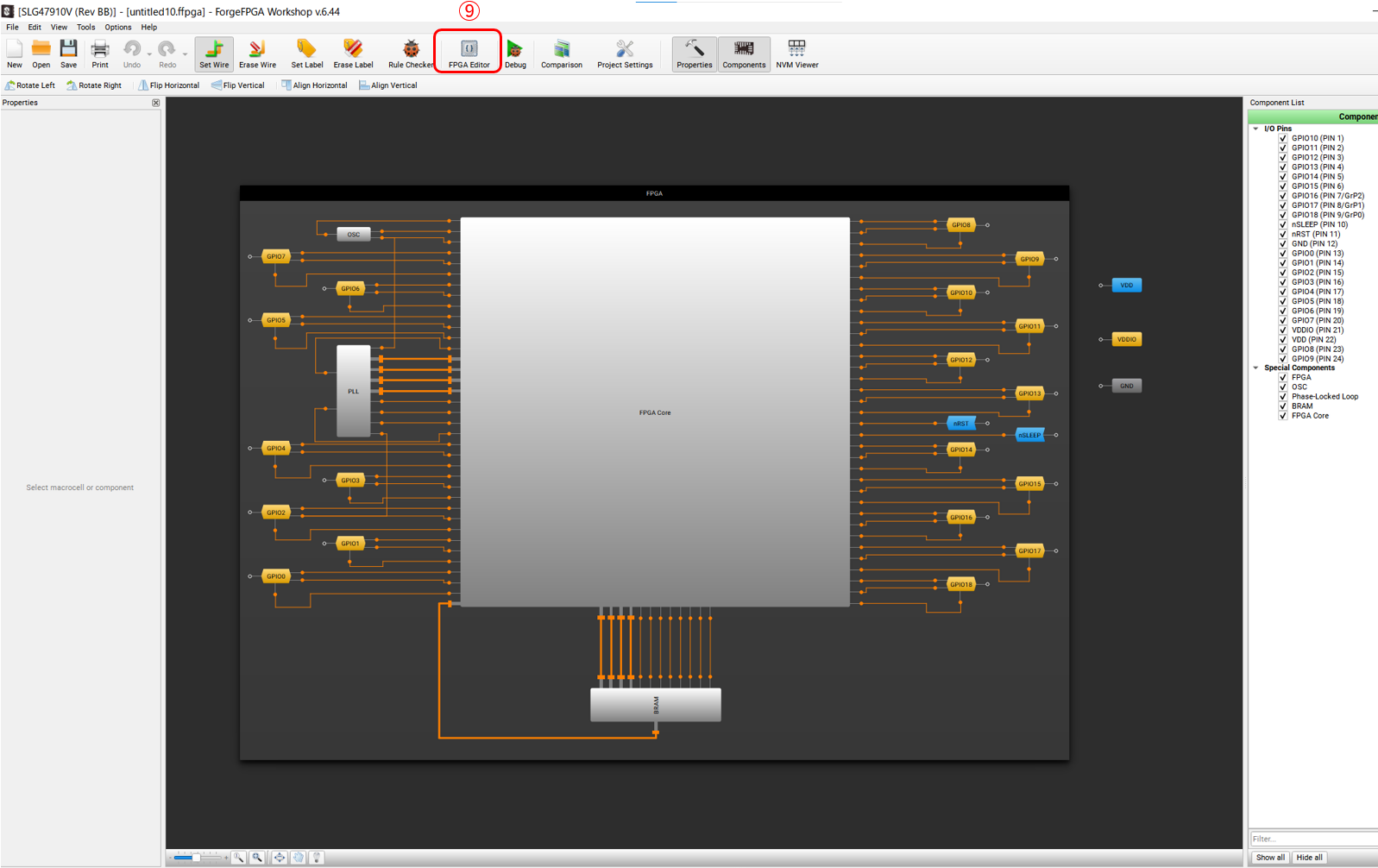

すると下記のような開発画面GUIが現れますので赤枠の⑨をクリックしてください。

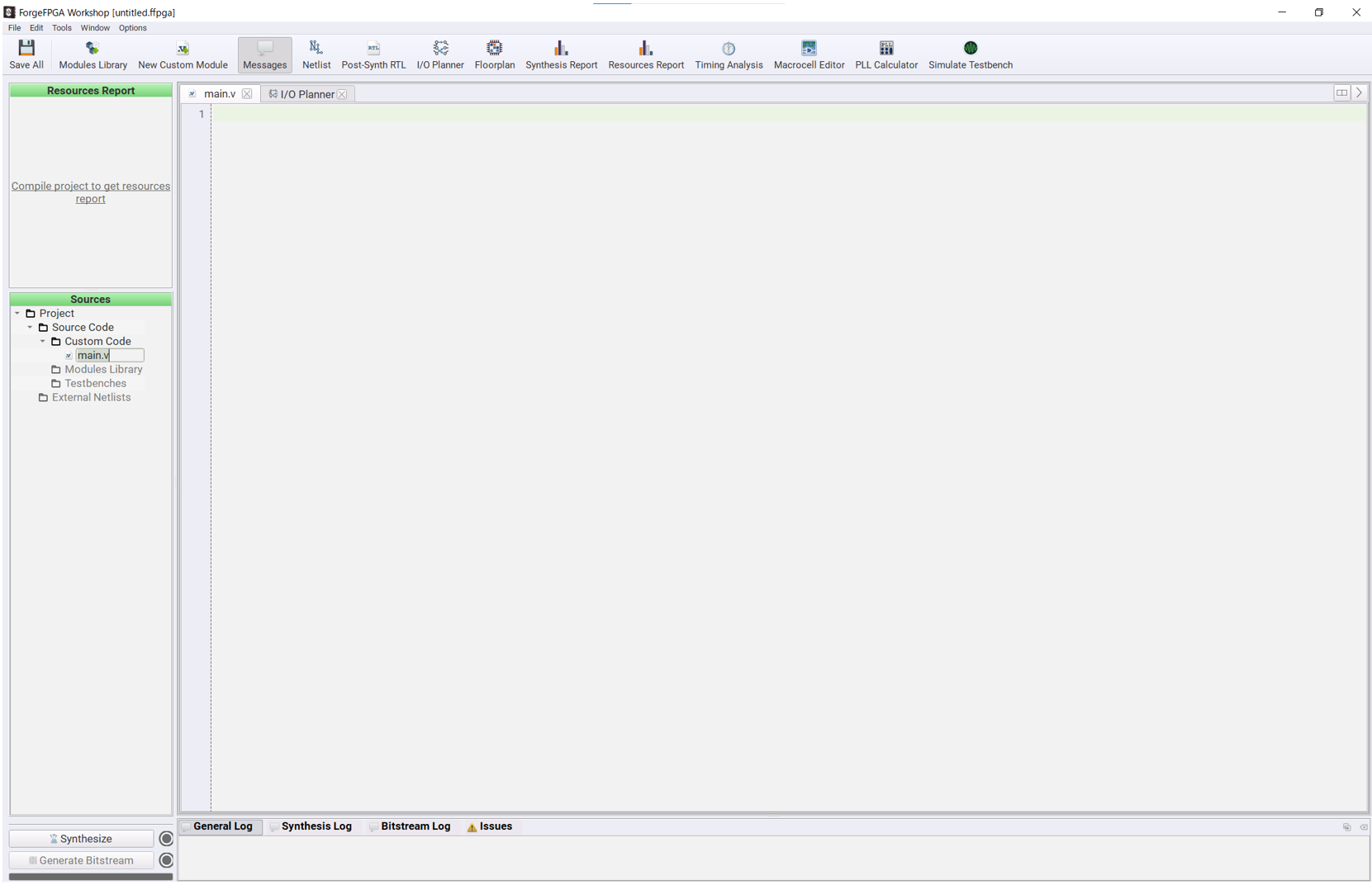

下のGUI画面に移行すれば開発環境の準備は完了です。

このGUIはForgeFPGAのprogram(Verilogコードになります。)を実際に書込みや、シミュレーションを動作させる画面になります。

ここまでが、ForgeFPGAの開発環境準備の説明となります。

ロータリエンコーダをシミュレーションしてみよう!

さて、次はロータリエンコーダをシミュレーションしてみましょう!

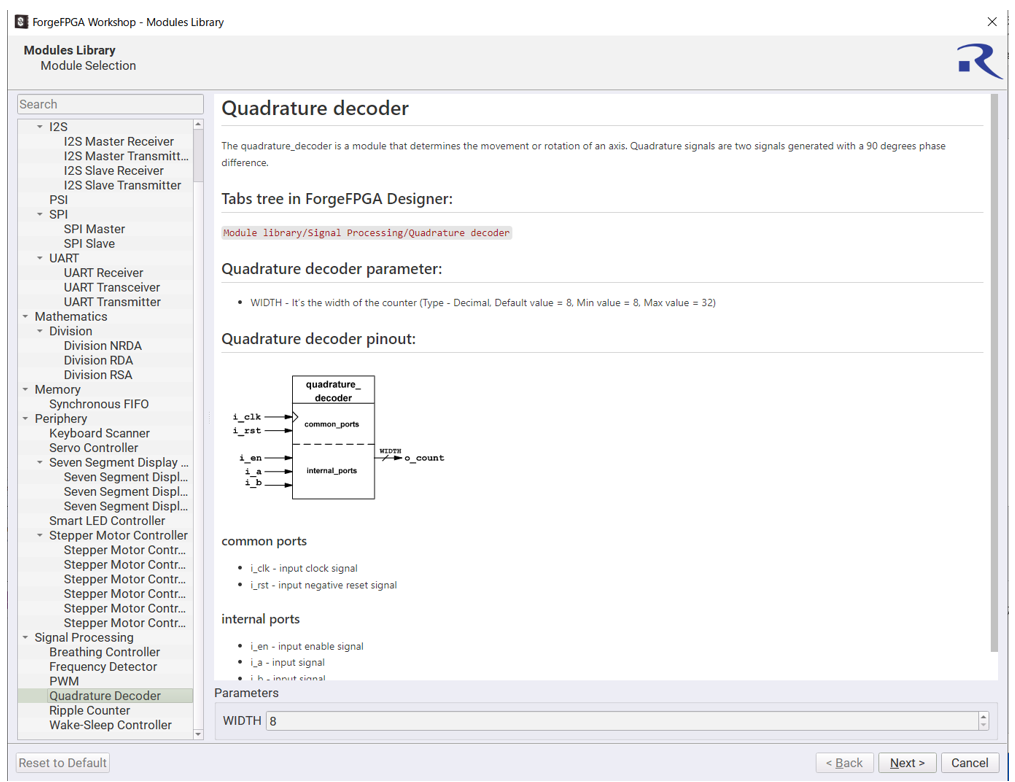

このロータリエンコーダのプログラムはルネサスのライブラリ(モジュールライブラリ)で提供されております。

(現状、全部で33個あります。今後もどんどん増える予定です。)

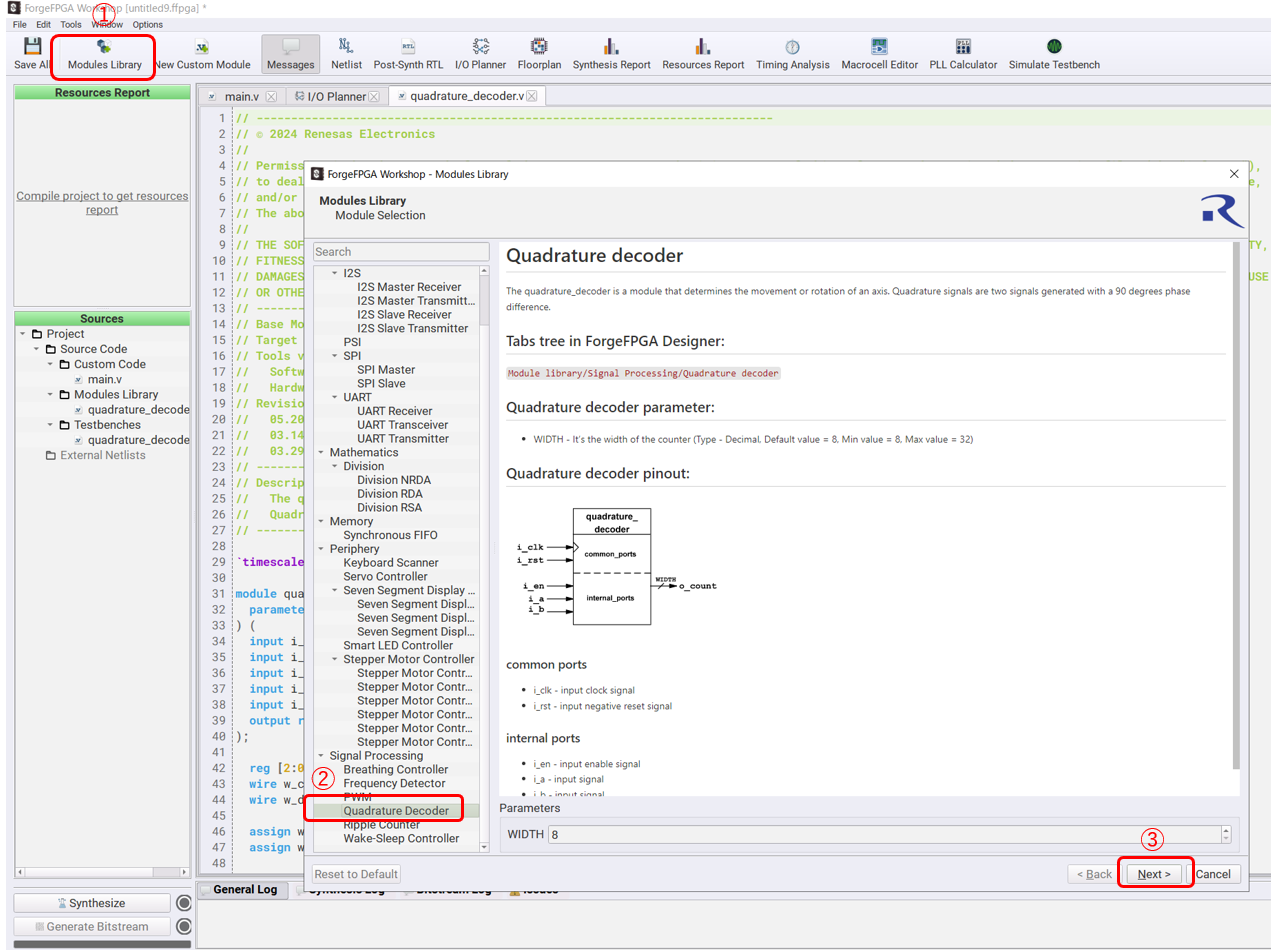

では、早速モジュールライブラリを使ってみましょう。下図の番号の順番にクリックを進めると、ライブラリから、ロータリエンコーダのサンプルコードを得ることができます。まずは左上の赤字①のようにモジュールライブラリをクリックし、次に中央の②のQuadrature Decoder(名前が少々異なりますが、こちらがロータリエンコーダになります)を選択します。最後に③のセレクトを押します。

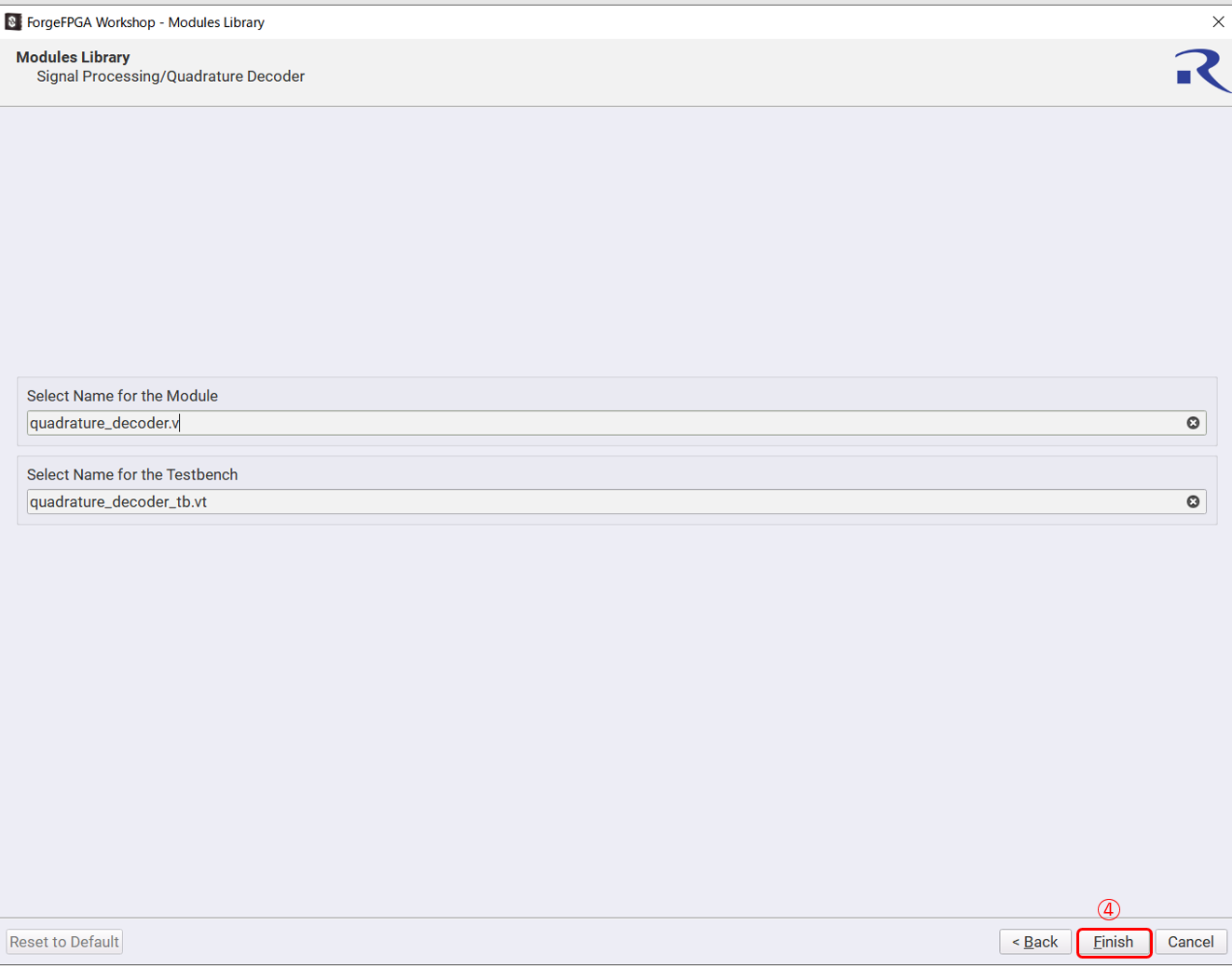

すると下図のような画面が出てきますので、④のセレクトを押します。

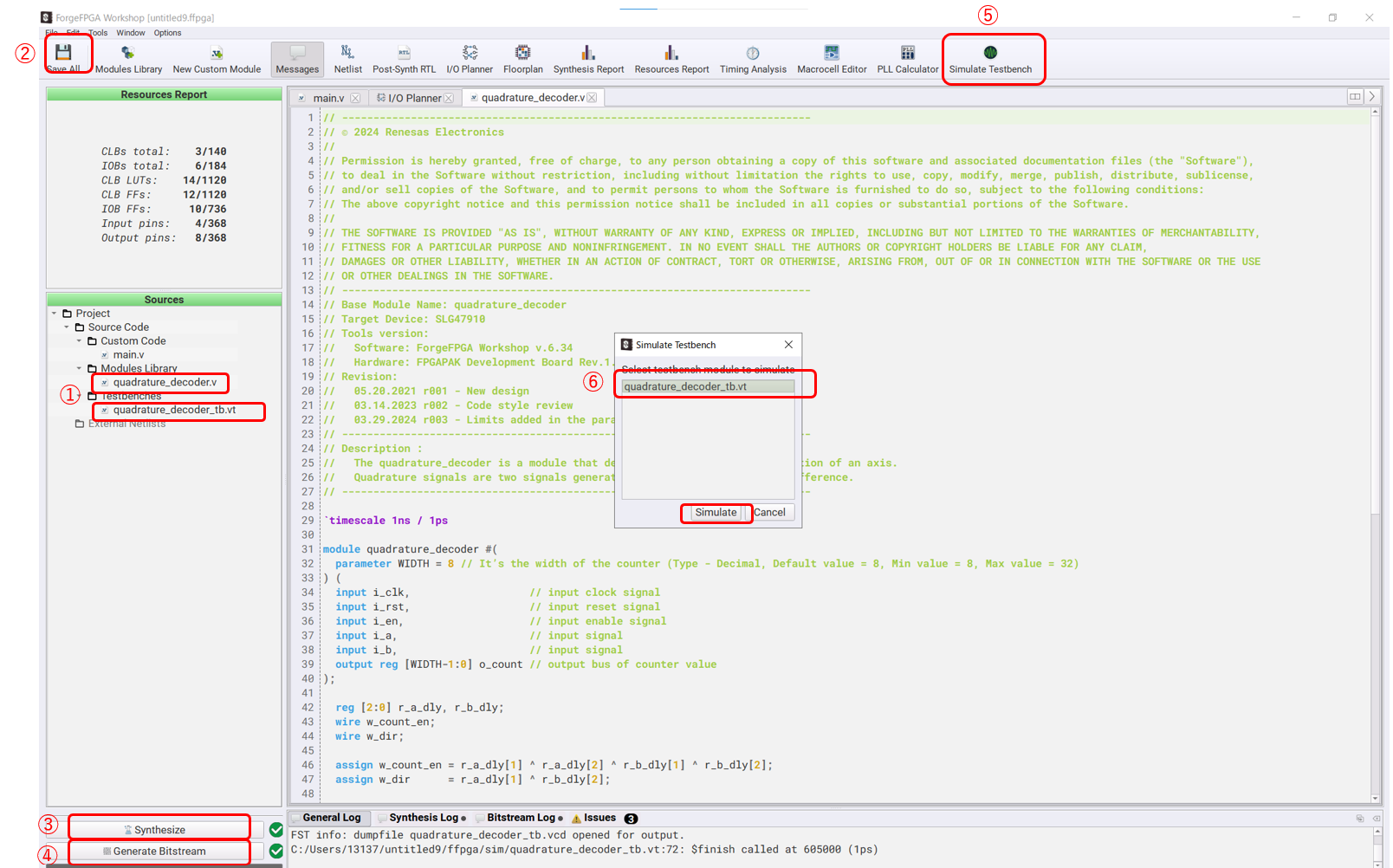

そうしますと、下図の中央左の赤枠①のように、デコーダとデコーダtbが各々ソース上に出来上がります。

ここで左上の②のセーブボタンを押し、左下の③でシンセサイズ、④ジェネレートビットストリームのボタンをクリックしてください。

無事にコンパイラが通れば、右上の⑤のシミュレートテストベンチをクリックし、最後に⑥のデコーダtbを選択し、シミュレートボタンを押してください。

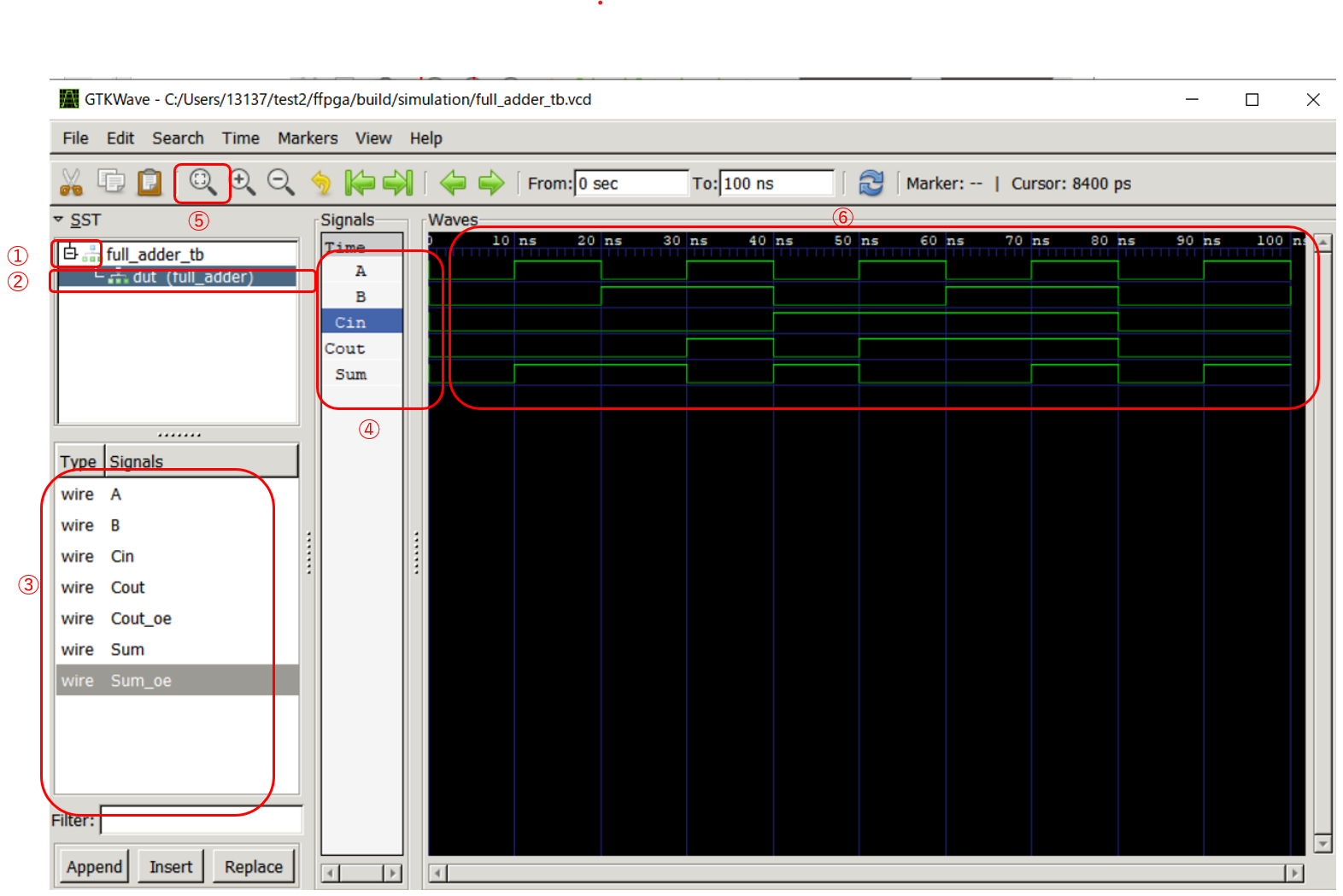

すると、下記のようなGTKWaveのシミュレーション画面が立ち上がります。ここで、下記の赤枠①②の順にクリックすると、③のステータスが現れます。ここから、必要なパラメータを取り出します。今回必要なものとして、赤枠④の通り、入力となるA相のa、B相のb、出力となるcountを選択します。続いて⑤の虫眼鏡ボタンをクリックすると、⑥のようにシミュレーション波形を得られます。

シミュレーション波形として、A相/B相の立ち下がる順番によって、8bitカウンタがインクリメントしたりデクリメントしたりと、

ロータリエンコーダ回路として所望の動作をすることを確認しました。これでロータリエンコーダ回路のシミュレーションは完成です。

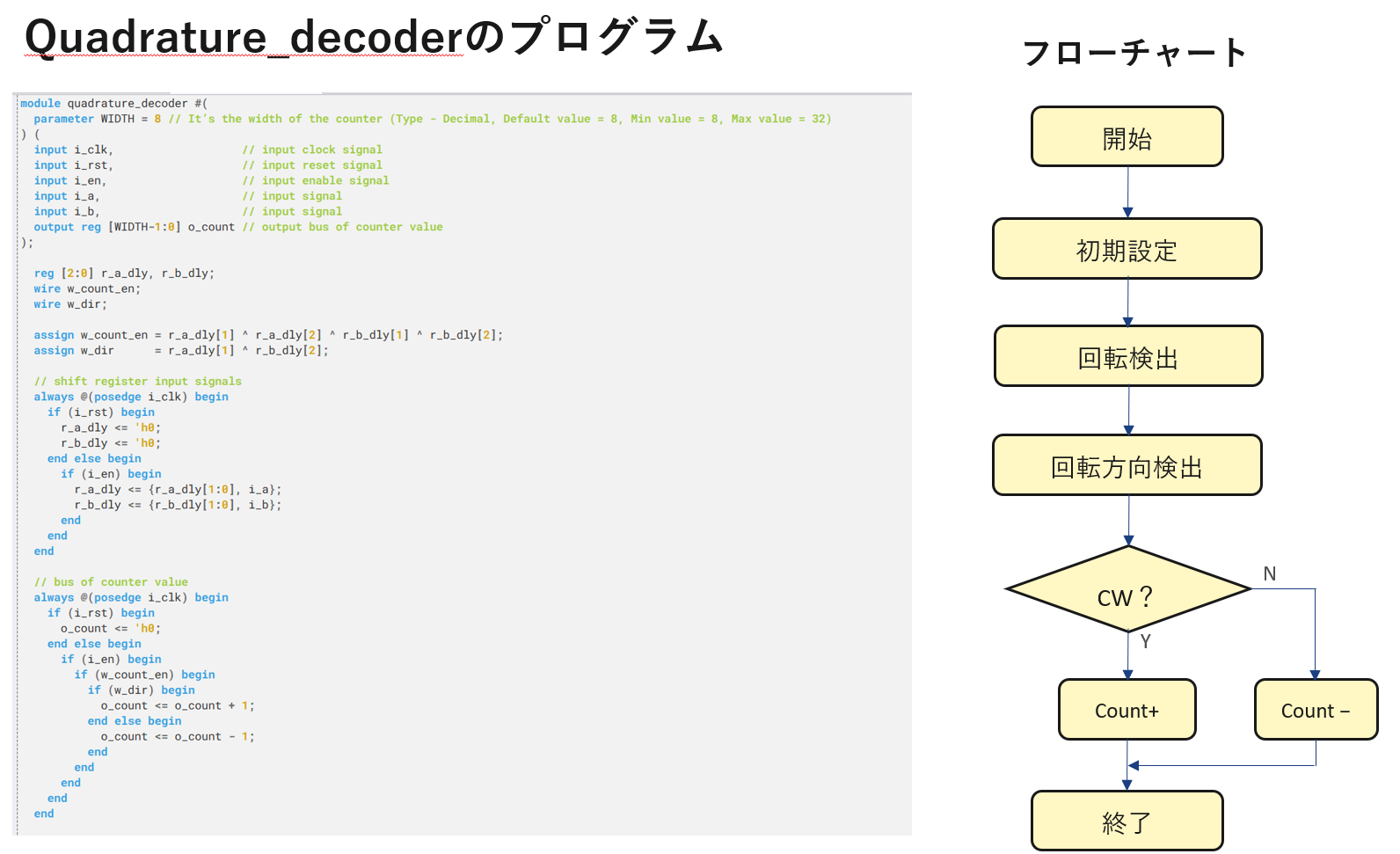

ここで、ロータリエンコーダ回路のシミュレーションで使用したquadrature_decoderのプログラムを下図に説明します。

右図のフローチャートの通り、A相、B相の回転方向を検出し、CWならカウントアップ,CCWならカウントダウンとなるような構成になっております。

実際に評価ボードを使ってロータリエンコーダを動かしてみよう!

さて、次はいよいよ、実際のAdvanced Hardware Kitを用いて、シミュレーション通りか確認してみましょう!

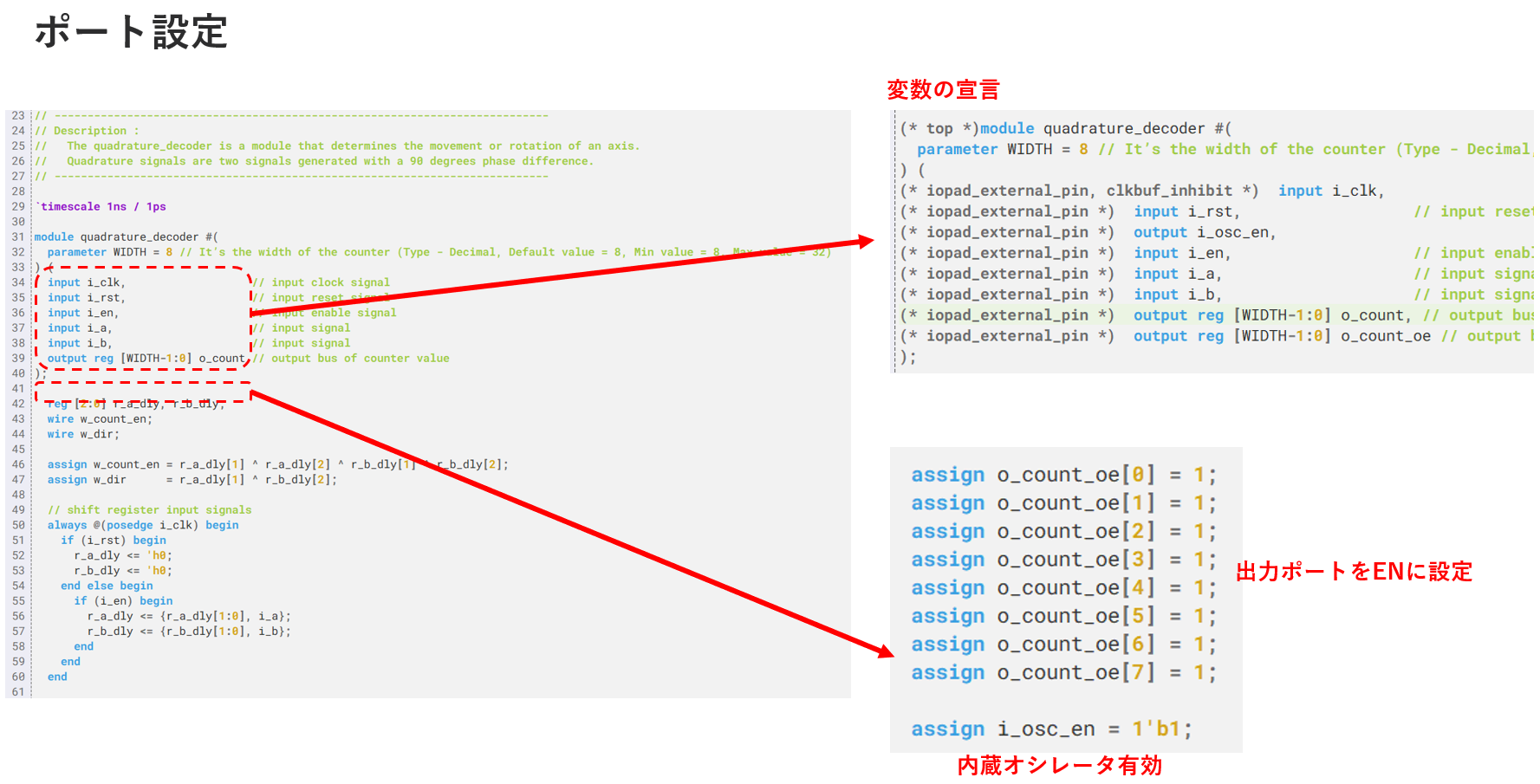

まずは、ポート設定です。下図は先ほど説明したプログラムです。こちらを右図のように変数宣言と、内蔵オシレータ有効設定、ポート方向の設定を決めるためにソースコードを追加します。

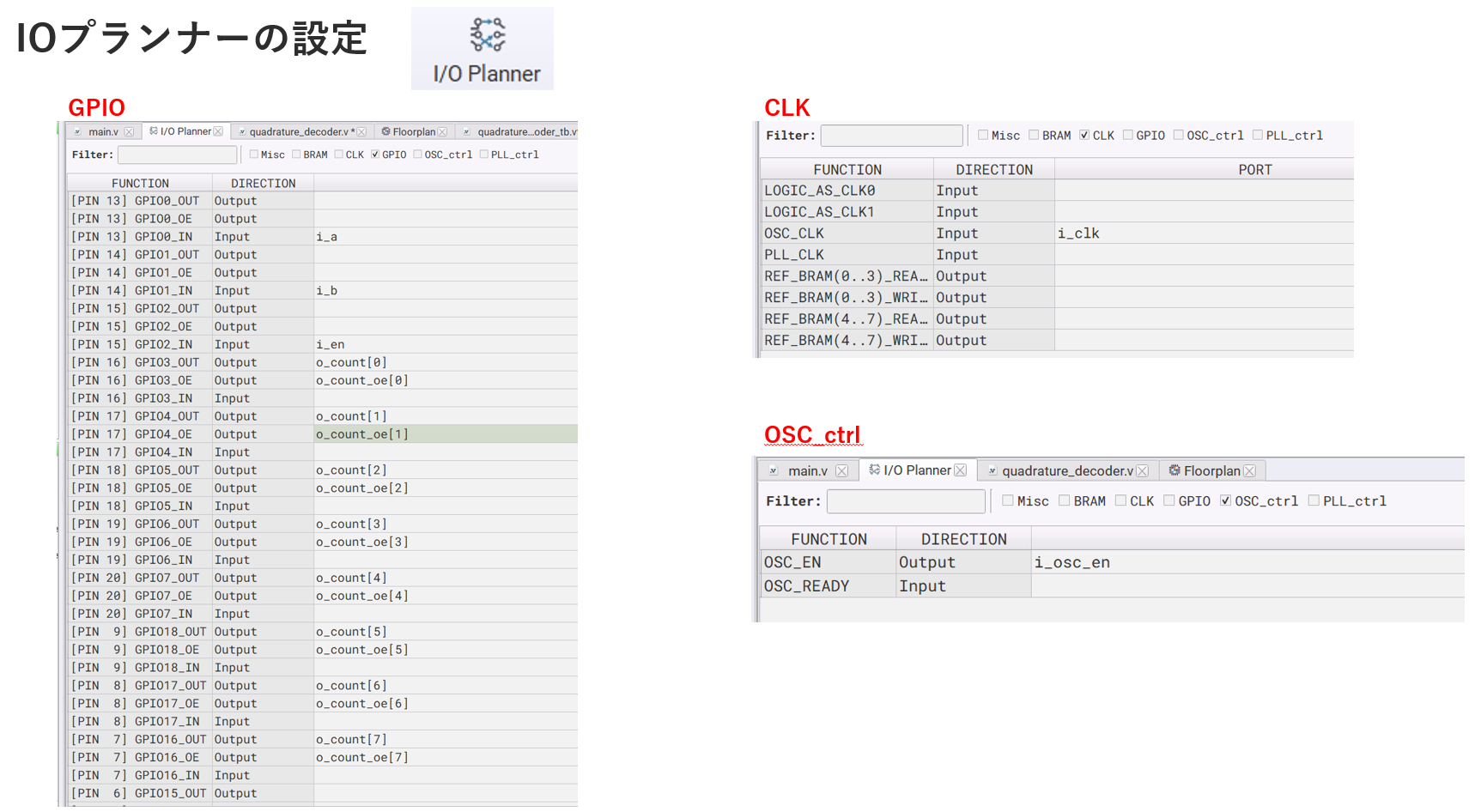

次に下記の通り、program画面中央上部のIOプランナータブを選択し、各ポートの入出力を設定します。下記の通り、設定してください。

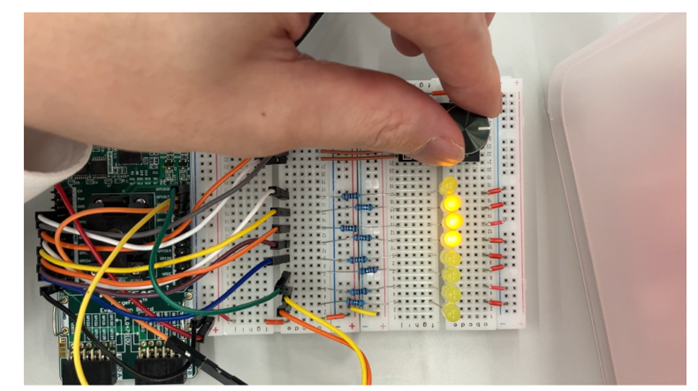

次に、IOプランナーの設定の通り評価ボードとブレットボードを配線します。(下記の図)

評価ボードのピン情報等は下記のURLからデータシートをご参考ください。

SLG7EVBFORGE – 1K LUT ForgeFPGA評価ボード | Renesas ルネサス

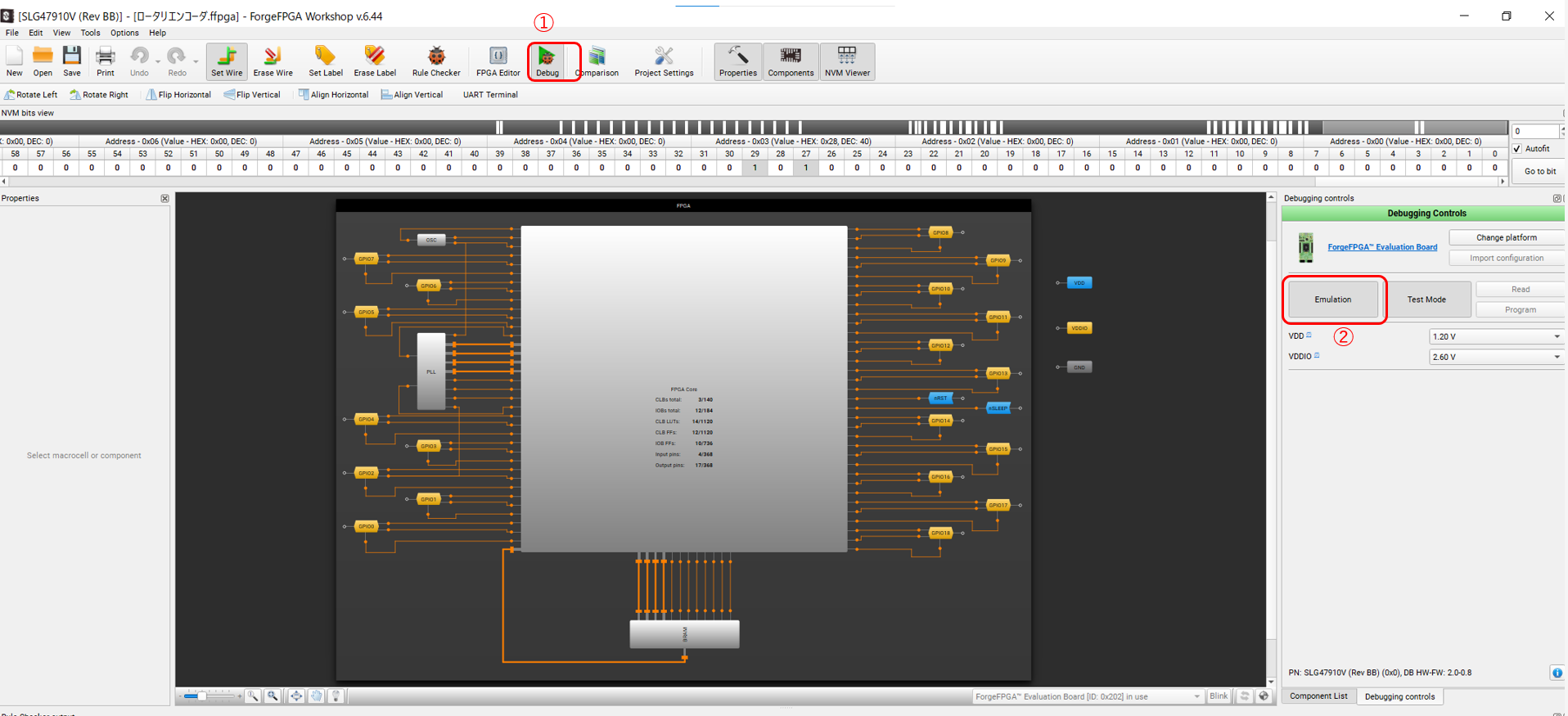

配線が完了しましたら、下記の通り中央上部の①デバッグ→②エミュレートの順にクリックします。

すると、下図の通りロータリエンコーダを左右に回すとインクリメント、デクリメントしそれに従いLEDが点灯消灯することを確認できます。これで無事にロータリエンコーダを動かすことができました。作業完了です。お疲れ様でした!

まとめますと、今回、ForgeFPGAを使用して以下のことを行いました。

・開発環境の立ち上げ

・ロータリエンコーダのシミュレーション

・EVKを使用したロータリエンコーダの動作確認

ライブラリを変更すればすぐにシミュレーションやEVK評価ができる環境が整っています。

ぜひForgeFPGAをお試しください。

お問い合わせはこちら

ルネサス製ForgeFPGAにご興味頂けた方は、メーカーページも是非ご覧ください!