- 公開日:2025年08月25日

- | 更新日:2025年09月24日

ルネサス回路シミュレーションツール iSim:PEを使ってみた(実用編)

- ライター:kjaz

- 電源

iSim:PEとは

iSim:PEはiSim Personal Editionの略で、ルネサス社が提供している回路シミュレーションツールです。SIMPLISとSIMetrixという2つのシミュレーションプラットフォームをベースにしており、パワーマネージメント部品にはSIMPLISを使用、オペアンプにはSIMetrixを使用、というように、2つのシミュレーションエンジンから選択することが出来ます。ソフトはルネサスのHPからフリーでダウンロードが可能です。https://www.renesas.com/ja/software-tool/isimpe-offline-simulation-tool

前回は導入編ということで、ツールの基本的な使い方、波形の出力方法について記載しました。https://emb.macnica.co.jp/articles/22838/

今回実用編として、降圧DCDCの位相補償回路の概要を説明すると共に、iSim:PEを使って実際に周波数特性を確認してみようと思います。

位相補償回路とは

まず位相補償回路について、簡単に解説します。

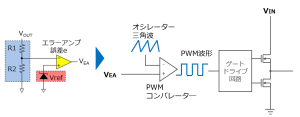

電源回路では出力電圧を一定に保つために負帰還制御を行っています。負帰還制御というのは、出力が上がったら下げる方向、下がったら上げる方向と、誤差をなくすような制御です。降圧DCDCの一般的な内部ブロック図は以下の通りです。

Voutと基準電源Vrefの誤差成分をエラーアンプで検出し、オシレータからの三角波をPWMコンパレータで比較し、PWM波形を生成します。このPWM波形によるDuty制御により、ゲートドライブ回路を通して、パワースイッチを駆動します。

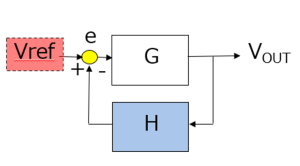

制御系全体をもっと簡略化して記載すると、以下のようになります。

電圧制御部Gやフィードバック部Hは周波数特性を持つため、位相遅れやゲインが変化することになります。図の構成からも分かるように、出力電圧の変動を打ち消すために、負帰還制御では180°の位相遅れが発生します。

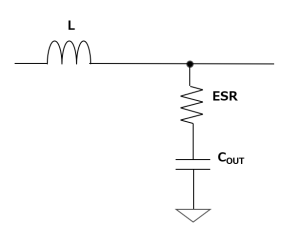

次に降圧DCDCの出力段に存在するLCフィルタにおける周波数特性についてです。

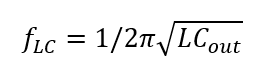

図に示す通り、ローパスフィルタを構成しており、コーナー周波数は以下式にて算出されます。

こちらもSimツールで簡易的に周波数特性を計算すると分かりますが、L成分による90°遅れ、C成分による90°遅れからトータル180°の位相遅れが発生します。

以上の内容から負帰還制御による180°の位相遅れ+LCフィルタによる180°の位相遅れにより、360°の位相遅れ、つまり正帰還となり、何もしなければ発振してしまうことになります。このため、IC内部、もしくは外部に専用の位相補償回路を持ち、これにより推奨動作条件下で系全体が安定的に動作するように設計されています。

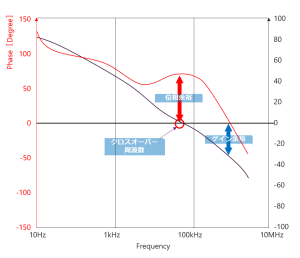

制御系の発振リスクを視覚的に確認する方法として、ボーデ線図があり、横軸に周波数、縦軸に位相とゲインを示します。位相が180°遅れた時、ゲインがマイナス何dBあるかを示すゲイン余裕、ゲインが0dBになる周波数での位相遅れが180°に対して何度余裕があるかを示す位相余裕、またその時の周波数をクロスオーバー周波数と規定し、系の安定性を示す指標としています。

一般的に電源回路の系が安定するためには位相余裕が45°、ゲイン余裕6dB以上が必要と言われており、これらに対してマージンが少なく、発振のリスクがある場合は、位相補償回路の定数を調整し、安定性を確保することになります。

位相補償回路の種類

それでは位相補償回路の種類を見ていきましょう。

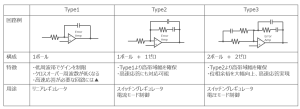

様々な構成があり、大別すると以下3つのタイプになります。それぞれの特徴を表にまとめます。

特徴の通り、Type1→2→3になるにつれて、周波数帯域が広くなっていきます。

電流モード制御の場合、内部に電流制御ループを持つため、L成分が1つのポールとしてキャンセルされます。そのためループ全体で次数が1つ下がり、Type2の1ポール1ゼロで十分安定制御が可能となる場合が多いです。一方電圧モード制御の場合、2つのポールが存在するため、ゲイン周波数を上げたい場合、Type2では位相余裕が足らず、不安定になります。そのためType3の2ポール2ゼロで大きな位相余裕を確保する必要が出てきます。

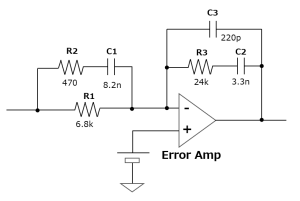

上記は一般論なので、電流モード制御でもType3を使って高性能化を求める場合もあれば、逆に電圧モードでも低帯域での使用なのでType2で十分な場合もあります。今回はType3回路でiSim:PEを試してみたいと思います。位相補償回路の定数を以下とします。

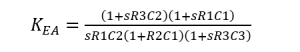

エラーアンプのゲインKEAは以下のように表されます。s=jωです。

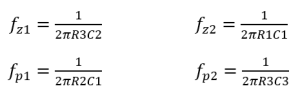

2つのポール、2つのゼロの周波数であるfz1、fz2、fp1、fp2は、各RとCの定数で以下のように算出されます。

上式を用いて計算すると、fz1=2.85kHz、 fz2=2.01kHz、 fp1=41.3kHz、fp2=30.1kHz となります。

iSim:PEを使って確認

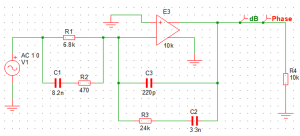

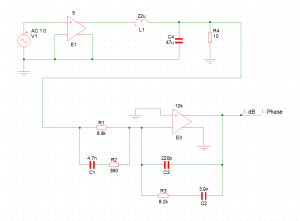

それではSim:PEで回路図を作成してみます。

シンプルに位相補償回路における周波数特性を確認したいので、エラーアンプ部にはVoltage Controlled Voltage Source(VCVS)を使用しました。[Part Selector]タブから、[Sources]→[Controlled Sources]→[Voltage Controlled Voltage Source]で読み出すことが出来ます。シミュレーションエンジンはSIMPLISではなく、SIMetrixを使用しました。ちなみにSIMPLISは過渡特性やスイッチング波形の解析が得意です。

その他回路図の入力方法は前回の導入編で説明しているので参考にして下さい。

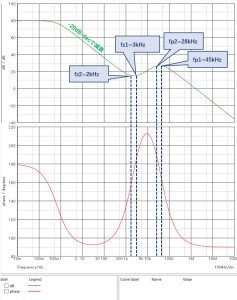

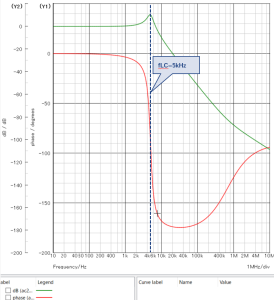

こちらがシミュレーションの実行結果です。

上側の緑線がゲイン、下側の赤線が位相となります。-20dB/decで減衰したゲイン特性がフラットになる周波数、上昇し始める周波数がそれぞれfz1、fz2、そして上昇後再びフラットになる周波数と下降し始める周波数がそれぞれfp1、fp2です。シミュレーション結果より、予め算出した結果(fz1=2.85kHz、 fz2=2.01kHz、 fp1=41.3kHz、fp2=30.1kHz)とほぼ近い値となっていることが確認出来ました。

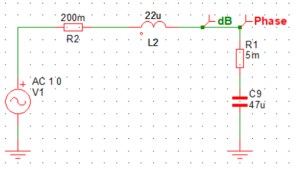

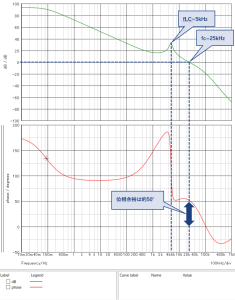

仮に出力部のLCフィルタの定数が下図だった場合の周波数特性もシミュレーションしてみました。

この例ですと、コーナー周波数fLCは、前述の通り1/2π√LCで試算されるため約5kHzとなっています。

L成分とC成分により、-40dB/decの傾きを持ってゲインは減衰し、位相は180°遅れていることが分かります。

実使用時におけるシチュエーションとしては、2つのゼロ、fz1とfz2を、LCフィルタのfLCに丁度当て込むことで、LCフィルタでの位相遅れをキャンセルすることが出来、同時に減衰したゲインを持ち上げることで、高周波数帯域まで安定動作が可能な制御系と作ることが出来ます。

お試しでゼロ点が5kHz付近になるように定数を調整し、LCフィルタを含めた全体の系でシミュレーションしてみました。

クロスオーバー周波数は約25kHz、位相余裕は約50°程度であり安定的に動作すると考えられます。但し、シミュレーション上で問題無い場合でも、定数のばらつき以外にインダクタの直流重畳特性やコンデンサのDCバイアス特性により、実際の測定で不安定になるケースも多々あるため、この辺りもしっかり加味した上で検討、検証する必要があります。

まとめ

今回は位相補償回路部にのみ絞ってiSim:PEによるシミュレーションを実行してみましたが、実際はスイッチング周波数からターゲットとなるクロスオーバー周波数fcを求め、更にfcからエラーアンプに要求されるGBWも考慮に入れる必要があります。また使用するコンデンサが電解コンデンサの場合、ゼロの配置にも大きく関わるためESRも含めた位相補償回路の定数を検討する必要が出てきます。上記パラメータも含めたより詳細なシミュレーションについてもiSim:PEで対応可能なので、是非一度をお使い頂ければと思います。

お問い合わせはこちら

ルネサス製品をお探しの方は、メーカーページもぜひご覧ください。