- 公開日:2025年12月10日

- | 更新日:2026年02月01日

GreenPAKの機能ブロック(マクロセル)をやさしく解説! – LUT、DFF、LATCH編-

- ライター:短絡亭フの字

- その他

本記事ではRenesas製品「GreenPAK」の「LUT、DFF、LATCH」ブロックの機能・使い方をわかりやすく解説します!

他の機能ブロックの解説記事はこちらから↓

| GreenPAKのBasicな機能紹介 | |||

| LUT,DFF,LATCH | FILTER,EDGE DET | Pipe Delay Ripple CNT |

CNT,DLY WS CTRL |

| A CMP | P DLY | TEMP Sensor | OSC |

| I2C | ASM | EEPROM | MF:Multi-Function |

| その他 | |||

| “Power GreenPAK” 特徴的な機能(マクロセル) | |||

| LDO | RTC、BG | P-FET | |

| “AnalogPAK” 特徴的な機能(マクロセル) | |||

| OPAMP | Digital Rheostat | Analog Switch | Chopper ACMP |

| Vref, HD Buffer | その他 | ||

| “HVPAK” 特徴的な機能(マクロセル) | |||

| HVOUT CTRL | PWM, PWM Chopper | Current Sense CMP、Diff AMP | |

LUT

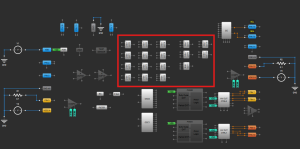

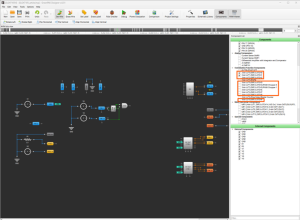

LUT(Look-Up Table)は、「入力の組み合わせに応じて、あらかじめ決めておいた出力を返す小さなメモリ」と考えるとイメージしやすいブロックです。GreenPAKには下図の赤枠で囲ったようなLUTブロックが複数搭載されています。

それぞれのLUTは、

・2入力LUT:2本の入力(IN0, IN1)に対して4通りの組み合わせ

・3入力LUT:3本の入力(IN0, IN1, IN2)に対して8通りの組み合わせ

・4入力LUT:4本の入力(IN0, IN1, IN2, IN3)に対して16通りの組み合わせ

について、「そのとき出力を 0 にするか 1 にするか」を真理値表として内部に保存しています。配線を変えなくても、この真理値表を書き換えるだけでAND / OR / XOR といったさまざまなロジックに切り替えられるのが特徴です。

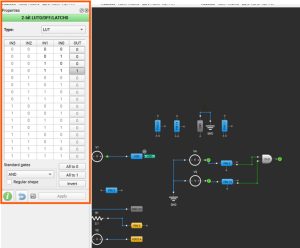

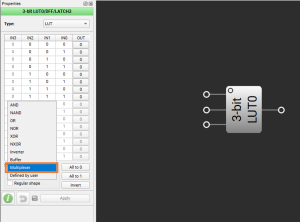

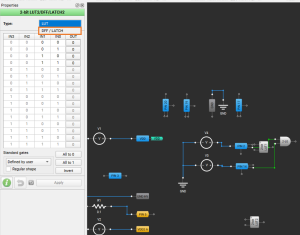

LUTブロックをクリックすると、左側に設定画面(Properties)が開きます。

下図のように、入力ビット(IN0, IN1 …)と出力ビット(OUT)が表形式で並んでいます。

出力側のOUT列のセルをクリックすると、「0」と「1」がトグルで切り替わります。すべての行についてOUTを設定することで、

「この入力パターンのときは0」「このパターンのときは1」と自由に出力のルールを決めることができます。

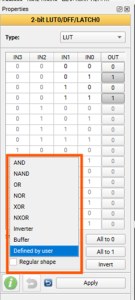

AND、NAND、ORなど、よく使う一般的なロジックについては、毎回OUT列を手作業で埋めなくても、画面下部のプルダウンメニューから簡単に選択できます。

・プルダウンの例:AND / NAND / OR / NOR / XOR / XNOR / Inverter / Buffer / Defined by user

いずれかを選ぶと、真理値表のOUT列が自動的に書き換わり、選んだロジックに対応したパターンに一括で設定されます。必要に応じて、ここからさらに個別の行だけOUTを変更して、「ほぼANDだけど一部だけ特別な条件を入れる」といったカスタムロジック にすることも可能です。

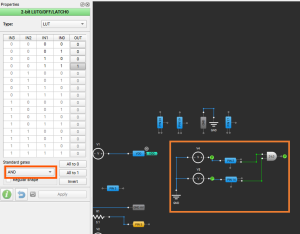

ここでは一例として、LUTを「ANDゲート」として動作させ、どのような出力波形になるかをシミュレーションで確認してみます。LUTブロックを選択し、画面左の「Standard gates」プルダウンから「AND」を選び、「Apply」をクリックします。

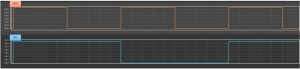

今回は、LUTのIN0(入力1)とIN1(入力2)に対して下図のような矩形波を入力します。

出力波形(OUT)もあわせて確認すると、IN0とIN1の両方がHighになっている区間だけOUTがHighになっていることがわかります。これは、先ほど AND を選択したときに設定された真理値表どおり、「IN0=1 かつ IN1=1 のときだけ OUT=1」という動作になっている、という意味です。

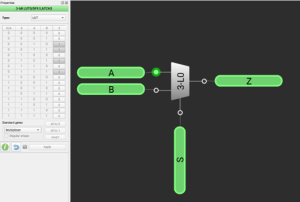

3入力LUTでは、ANDやNANDなどの基本ロジックに加えて、「Standard gates」から「Multiplexer」を選択することもできます。

「Multiplexer」を選んで「Apply」をクリックすると、ブロックのシンボルが 2:1 MUXの形に変わり、ピン名もA / B / S / Zといった名前に自動で書き換わります。

このときの真理値表は次のようになり、入力 S がセレクト信号として動作します。

・S = Low(0)のとき:入力Aの信号がそのままZに出力される

・S = High(1)のとき:入力Bの信号がZに出力される

つまり、3入力LUTを「Multiplexer」として選ぶことで、AとBのどちらを出力するかをSで切り替える2:1マルチプレクサを簡単に実現できます。

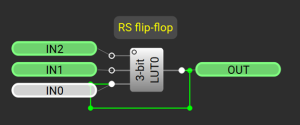

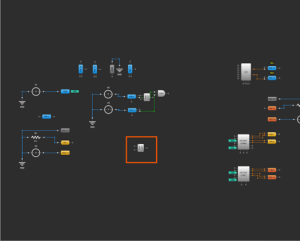

さらに、3-bit LUTのひとつの使い方として下図のように自分自身の出力をフィードバックすることで「簡易的なRS FF」として動作させることもできます。

・IN2 … S(Set)

・IN1 … R(Reset)

・IN0 … Q_FB(前段の出力Qをフィードバックした信号)

とみなした場合、LUTの真理値表は以下のように設定になります。

| IN2(S) | IN1(R) | IN0(Q_FB) | OUT(Q) |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

※「IN2(S)=1 , IN1(R)=1 , IN0(Q_FB)=0のときQ=0」、「IN2(S)=1 , IN1(R)=1 , IN0(Q_FB)=1のときQ=0」と設定しています。

このようにOUTをIN0に戻すことで、LUTは「現在の出力QとS/Rの入力から次の状態Q_nextを決めるRS FF」として動作します。

入力の割り当てと真理値表の書き方次第で、組み合わせ回路だけでなく簡単な順序回路も構成できることが、LUTマクロセルの大きな魅力です。

DFF

DFFは「クロックの立ち上がりの瞬間にD入力のデータを取り込み、その値を次のクロックの立ち上がりの瞬間まで出力として保持し続ける」動作をします。イメージとしては、時計が「カチッ」と鳴るタイミングでだけメモを取るようなもので、その瞬間に何が書いてあったかだけを覚え、それ以外の変化は基本的に無視されます。

DFFはLUTと同じブロックになっていることが多いです(下図のオレンジ枠参照)

今回は右側のComponentsから「2-bit LUT2/DFF/LATCH2」を選択してみましょう。

Go Configure上に「2-bit LUT2」のブロックが現れました。まずはこのブロックをDFFに変換する方法をご紹介します。

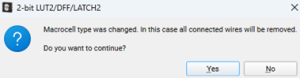

「2-bit LUT2」をダブルクリックすると左側にPropertiesが現れるので、Typeの項目を「LUT」から「DFF/LATCH」に変更し、最後に「Apply」をクリックしてください。

以下のようなメッセージが現れるので「Yes」をクリックするとブロックの形がDFF2に変わります(下図右側のブロック参照)。

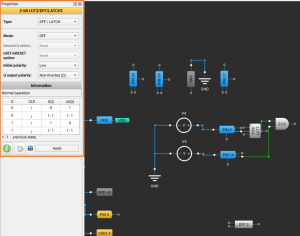

これでDFFのブロックに変更完了です。続いてDFFブロックをダブルクリックしてPropertiesを設定していきます。

各項目の説明

・Type

「LUT」または「DFF/LATCH」を選択します。

・Mode

「DFF」または「LATCH」を選択します。

・second Q select ※この項目がない場合もあります

「Q of first DFF」または「Q of second DFF」を選択します。対応しているブロックではDFFが二段直列に配置されており、1段目のDFFの出力を使うか二段目のDFFの出力を使うかを選択できます。

・nSET/nRESET option ※この項目がない場合もあります

「nRESET」または 「nSET」を選択します。

nRESETを選択した場合は以下の動作をします。

– nRESET が0のとき …リセット動作が有効になり、Qは0にクリアされます。

– nRESET が1のとき … リセット動作は行われず、通常動作になります。

nSETを選択した場合は以下の動作をします。

– nSET が0のとき … セット動作が有効になり、Qは1にセットされます。

– nSET が1のとき … セット動作は行われず、通常動作になります。

nRESET/nSETともに「Low を入れたときに有効となる信号」 です。そのため、これらの端子を使用しない場合はVDD(常時High)に接続しておくことを推奨します。

・Initial polarity

最初のCLKパルスが入力される前の出力状態を「High/Low」どちらにしておくかを選択します。

・Q output Polarity

出力Qをそのまま出力するか反転して出力するかを選択します

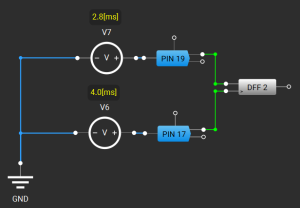

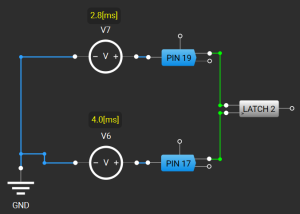

ここからは実際にDFF2の動作をシミュレーションで確認していきます。今回は下図のような接続でシミュレーションを行います。

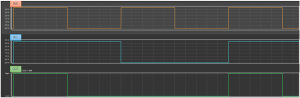

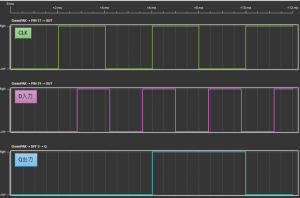

D端子には周期2.8msのHigh/Low信号を入力し、CLK端子には周期4.0msのHigh/Low信号を入力しています。この条件でのDFFの出力波形を確認していきます。

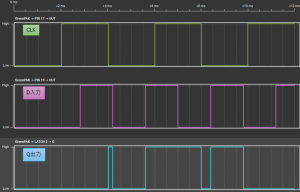

CLKが立ち上がった瞬間のD入力の値がQとして出力され、その値が次CLKの立ち上がりまで保持されていることが見て分かります。

LATCH

LATCHは「クロックが有効(LowまたはHigh)になっているあいだは、D入力をそのまま出力に通し続け、クロックが無効になった瞬間のDの値を保持し続ける」という動作を行います。イメージとしては、ドアと部屋を想像すると分かりやすいです。

・ドアが開いているあいだは、人(= Dの値)が自由に出入りでき、部屋の中(=Qの値)もそれに合わせて変わり続けます。

・ドアが閉まった瞬間、そのとき部屋の中にいた人で固定され、その後は部屋の中身は変わりません。

DFF が「カチッ」という瞬間だけメモを取るのに対して、LATCHは「ドアが開いているあいだはDを通し続け、閉まったところで値を保持する」動きだと考えてもらえればOKです。

LATCHもDFFと同様に、LUTと一体になったブロックとして用意されていることが多く、設定方法もDFFと同じなのでここでは詳細な設定説明は割愛します。

続いて、DFFと同じ入力条件のまま下図の接続で LATCH の動作をシミュレーションしていきます。

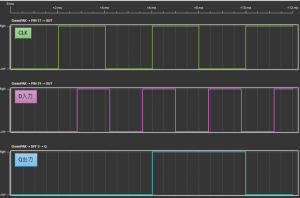

このときのLATCHの出力波形は下図のようになります。

CLK がLowのあいだはLATCHが「開いた状態」になっており、D入力の値がそのままQ出力に現れます。

CLK がLow→Highに変化した瞬間にLATCHが閉じて、その時点のD入力の値を記憶します。

いったん閉じると、次にCLKが再びLowになるまで、Dが変化してもQはその記憶した値のまま変化しません。

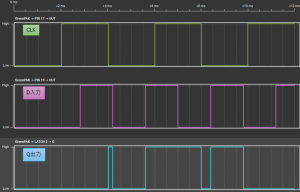

以下にDFFとLATCHの出力波形を並べてみます。(左側:DFF、右側:LATCH)

波形を見比べると違いは明確です。DFFは「クロックのエッジ(立ち上がり/立ち下がり)」の瞬間だけDを取り込み、それ以外の時間は出力Qが変化しません。つまり、Qはクロックのタイミングに同期して“カチッ”と更新されます。

一方LATCHは「クロックが有効の間」は入力Dに追従し、無効になるとその時点の値を保持します。

言い換えると、DFFは“瞬間だけメモする”、LATCHは“開いている間は透過するドア”です。

そのため、同期回路として安定に状態を保持したいならDFF、特定の期間だけ入力を通したいならLATCH、という使い分けになります。

まとめ

RenesasのGreenPAKは回路を自由に構成できるプログラマブルデバイスです。

「こういう動作を1チップでまとめたい」、「この回路をGreenPAKで置き換えられないか」などのアイデアがございましたら、弊社エンジニアが検討、ご提案いたしますので、どうぞお気軽にご相談ください。

また、ルネサス製品をお探しの方はメーカーページもぜひご覧ください

<Renesas Electronics Corporation – 半導体事業 – マクニカ (macnica.co.jp)>