- 公開日:2019年03月29日

- | 更新日:2022年11月30日

SDIってどうやって設計すればいいの??

- ライター:Kawai

- インターフェース

はじめに

前回では映像信号を送信する際になぜSDIを使用していてどんなメリットが有るのか、今後のSDIはどうなっていくのかをご紹介させていただきましたが、本稿ではSDIの規格とレイアウト設計などについてお伝えさせていただきます。

SDIの規格要求と評価項目

SDIはSMPTEによって規定されたビデオインターフェースの物理層規格です。表1にSDIの各規格に対する要求値を示します。

*SMPTEの規格書は有償でSMPTE.org(https://www.smpte.org)より入手が可能です。

| ST 259M SD-SDI |

ST 292M HD-SDI |

ST 424M 3G-SDI |

ST 2081 6G-SDI |

ST 2082 12G-SDI |

||

|---|---|---|---|---|---|---|

| Driver | データレート | 270 Mbps | 1.485 Gbps 1.485/1.001 Gbps |

2.97 Gbps 2.97/1.001 Gbps |

5.94 Gbps 5.95/1.001 Gbps |

11.88 Gbps 11.88/1.001 Gbps |

| 振幅 | 800 mV±10 % | 800 mV±10 % | 800 mV±10 % | 800 mV±10 % | 800 mV±10 % | |

| Over Shoot | 10 % of Amplitude | 10 % of Amplitude | 10 % of Amplitude | 10 % of Amplitude | 10 % of Amplitude | |

| Under Shoot | 10 % of Amplitude | 10 % of Amplitude | 10 % of Amplitude | 10 % of Amplitude | 10 % of Amplitude | |

| DC Offset | 0 ± 0.5 V | 0 ± 0.5 V | 0 ± 0.5 V | 0 ± 0.5 V | 0 ± 0.5 V | |

| tr/tf | 400 ps – 1500 ps | ≦ 270 ps | ≦ 135 ps | ≦ 80 ps | ≦ 45 ps | |

| tr/tf mismatch |

≦ 500 ps | ≦ 100 ps | ≦ 50 ps | ≦ 35 ps | ≦ 18 ps | |

| Timing Jitter |

≦ 0.2 UI 10 Hz – 27 MHz |

≦ 1.0 UI 10 Hz – 148.5 MHz |

≦ 2.0 UI 10 Hz – 297 MHz |

≦ 2.0 UI 10 Hz – 594 MHz |

≦ 2.0 UI 10 Hz – 1188 MHz |

|

| Alignment Jitter |

≦ 0.2 UI 1 kHz – 27 MHz |

≦ 0.2 UI 100 kHz – 148.5 MHz |

≦ 0.3 UI (≦ 0.2 UI Recommended) 100 kHz – 297 MHz |

≦ 0.3 UI (≦ 0.2 UI Recommended) 100 kHz – 594 MHz |

≦ 0.3 UI (≦ 0.2 UI Recommended) 100 kHz – 1188 MHz |

|

| Driver and Equalizer | Return Loss | |||||

| 5MHz – 270MHz | ≦ 15 dB | ≦ 15 dB | ≦ 15 dB | ≦ 15 dB | ≦ 15 dB | |

| 5MHz – 1.485GHz | – | ≦ 15 dB | ≦ 15 dB | ≦ 15 dB | ≦ 15 dB | |

| 1.485GHz – 3GHz | – | – | ≦ 10 dB | ≦ 10 dB | ≦ 10 dB | |

| 3GH – 6GHz | – | – | – | ≦ 7 dB | ≦ 7 dB | |

| 6GHz – 12GHz | – | – | – | – | ≦ 4 dB |

表1 SDIの規格要求一覧

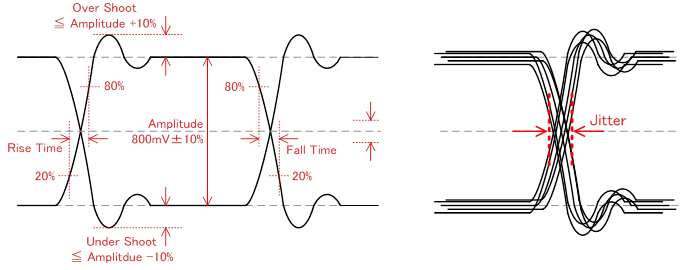

主に出力波形に対する振幅、Overshoot/Undershoot、tr/tfとそのミスマッチ、オフセット電圧についての要求値が細かく規定されています。ケーブルドライバ出力波形規格要求である図1を見て頂くとどの部分を指しているのかイメージし易いと思います。尚、ジッタに関してはTiming JitterとAlignment Jitterの2種類があります。Timing Jitter (TJ)は受信側のPLLが追従できる低い周波数領域のジッタ(2.0UI以下@10Hz~)、Alignment Jitter (AJ)は受信側のPLLが追従できない高い周波数領域のジッタ(0.3UI以下@100kHz~)から全ての周波数領域と定義されています。3G/6G/12G SDIにおいてAJの規格限界値は0.3UIですが、推奨値が0.2UI以下であることに注意が必要です。

図1 ケーブルドライバ出力波形規格要求

ドライバの出力波形評価をする際には1mケーブルを介して観測すると定められています。ケーブルの種類や型名の指定はなく、日本では3G-SDIまでであればL-5CFB(カナレ電気社製)、12G/6G-SDIではL-5.5CUHD(カナレ電気社製)が一般的に用いられます。海外ではBelden社製のケーブルが一般的です。波形評価には波形モニタと呼ばれる専用測定器や高速オシロスコープが用いられます。前回の単元でもありましたが、SDIは75オームの特性インピーダンスを採用しているので、オシロスコープを使用する場合では入力のインピーダンスが50Ωのため、75Ωの信号を受けるには75Ω/50Ωインピーダンス変換器が必要です。信号帯域は5次高調波まで観測できることが望ましいです。機材によって制限される部分もあり、特に12G-SDIにおいては、使用する測定機器によって波形やジッタ読み値に大きな差が生じることがあります。ある機器での評価では規格条件をパスしたものが、別の機器では規格違反と見えるケースもあり、注意が必要です。

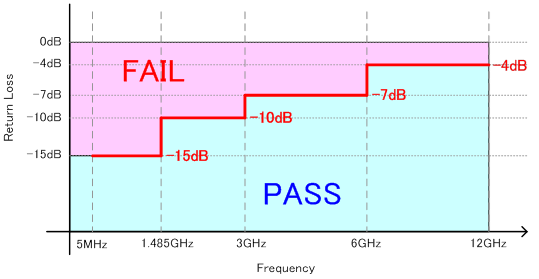

ドライバとイコライザの両方に要求される特性としてリターンロスがあります。図2にリターンロスの規格要求値を示します。リターンロスとは反射による損失を表す値で、どれだけ効率的に信号を送出または受信できるかを表す指標です。測定した結果が小さいほど(マイナス値)反射が少なく、信号を乱す要素が少ないことを表します。周波数帯域毎に規定された値があり、図2の赤い線以下であることが要求されます。リターンロスの測定にはネットワークアナライザと75Ω系での測定ができるよう、75Ω/50Ωインピーダンス変換器や75Ωの校正キットが必要です。

図2 リターンロス規格要求

これらの規格要求を満たすためにSDI専用のICを使用します。しかし、5GHzを越える世界ではプリント基板レイアウトの影響が支配的となります。適切なレイアウトをしないと規格要求を満足できず、何度も基板を改版することになってしまいます。

基板設計時に注意すべきポイントは?

SDIの要求規格を満足させるためにやらなければいけないことは何か?SDI基板設計の基本として、以下のポイントにご注意頂きます。

1. シリアライザに供給するクロックには、極力ジッタの小さいクロックを使用する

最新のSDI製品にはリクロッカ機能が内蔵されているため、これ1つでTJ/AJ全てのジッタを取り除くことができると誤解される方もいらっしゃいます。しかし、リクロッカのループ帯域より低いジッタ成分は取り除くことができません。もし開発中のシステムの出力ジッタが大きいようであれば、まず、シリアライザ出力やシリアライザに加えるクロックに、そのジッタ成分が存在しないか確認してください。シリアライザのクロックにはジッタの小さなクリーンなクロックを使用することが必要不可欠です。必要に応じて、クロックに含まれるジッタ除去のためにジッタクリーナーをご使用ください。

2. BNCコネクタからデバイス(SDI ドライバ/イコライザ)までの特性インピーダンスを75Ωに管理する

SDIの設計で最も苦労する要求値がリターンロスです。高速信号は特性インピーダンスが異なるポイント(異なるモノとモノの接続点)で反射が発生します。ケーブルとコネクタの接続点、BNCコネクタと基板の接続点、受動部品の実装部、ICの実装部が接続面であり、これらのポイントを含めた伝送路上での反射が最小となるように設計することが重要です。以下についてご注意ください。

- BNCコネクタ直下の基板レイアウトはコネクタメーカーの推奨に従う

- 基板構造や材質によって微調整が必要

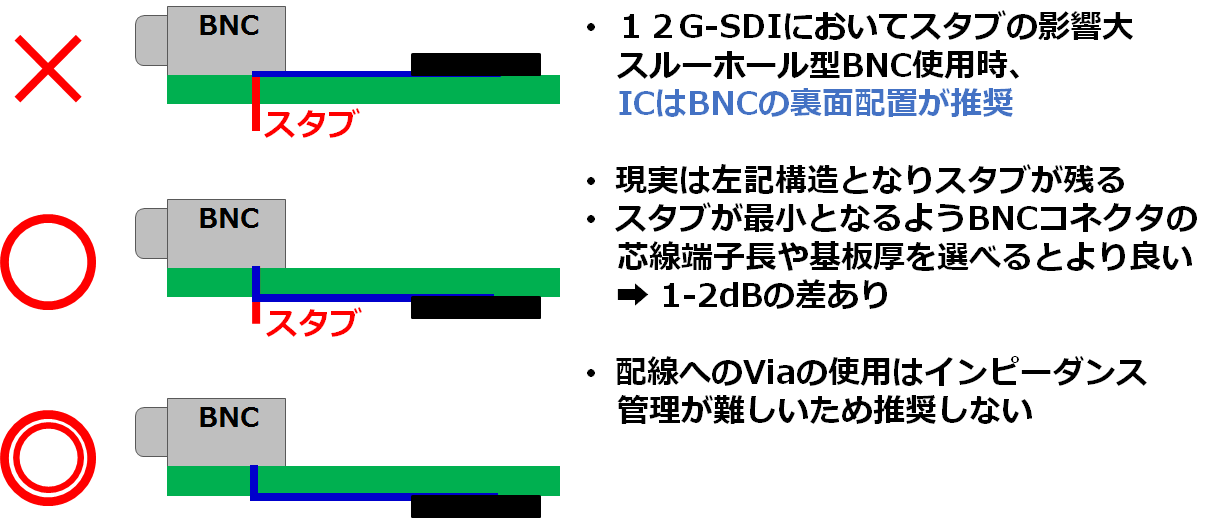

- スルーホールタイプBNCコネクタとデバイスは同じ基板面に実装しない

- BNCコネクタはスルーホールタイプを使用することが多く、同一面に実装した場合、コネクタの芯線がスタブとなり、リターンロス特性に悪影響を及ぼします。コネクタに対しICを裏面配置とすることでスタブを最小化することができ、リターンロス特性や出力波形歪への改善が見込めます。

図3 BNCコネクタの配置

- 層抜きの実施

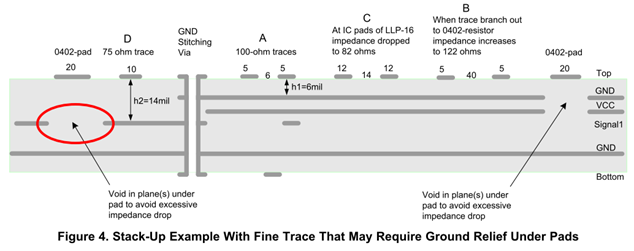

- 信号配線幅に比べ部品のランド幅が大きいと、寄生容量によりランドでのインピーダンスが低下します。基準層をより深く取ることで配線幅を広くでき、ランド幅と同じ太さにすることが出来ます。この手法が使用できない場合は、図4のようにランド直下の電源層・GND層を抜くことでインピーダンス低下を防ぎます。

図4 インピーダンス管理するための基準層の取り方 (出典:Texas Instruments Inc. AN-1972)

3. BNCコネクタからデバイス(SDI ドライバ/イコライザ)までの配線長を最小にする

配線が理想的な75Ωにインピーダンス管理されていれば反射は起きません。その場合、コネクタとデバイス間の配線がいくら長かろうと問題にはなりません。しかし、現実世界ではそうはいきません。配線長が長くなれば、それだけインピーダンス管理しなければならない部分が多くなります。配線の太さやGNDまでの距離等、基板毎の製造バラつきも生じるため、リターンロス特性の観点では短いに越したことはありません。デバイスの配置はBNCコネクタから1インチ(2.5cm)以内に配置することが理想です。

4. 電源ノイズを最小化する

電源ノイズにも注意が必要です。SDI出力端子は通常、IC内部または外部で75Ωを経由し、電源にプルアップし終端されています。従って、電源のノイズはダイレクトにSDIの信号品質に影響します。電源のゆらぎはジッタになりますので、電源ノイズは極力小さくして頂きます。もし可能であれば、PSRRの高いLDOを使用することをお勧めします。

5. 基板設計の最適化

ある程度検討を重ねたとしても、SDIの基板は初回の試作で完璧なものを作り上げることはなかなか難しいものです。不幸にも試作した基板がリターンロス規格値を満たせなかった場合、TDR(Time Domain Reflectometry)によるインピーダンス解析を行うことで性能が満たせなかった原因を特定することが可能です。

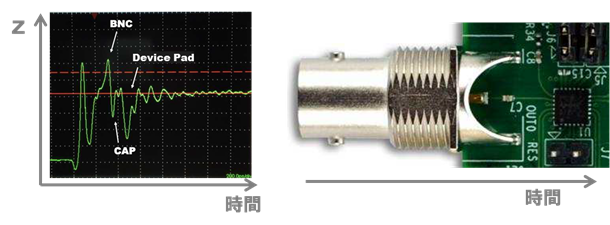

図5 TDR測定結果の例

図5 TDR測定結果の例

TDRは横軸を時間、縦軸をインピーダンス表示し、信号が進むにつれてどのようにインピーダンスが変化するかを波形として表示します(図5)。この結果から、基板のどのポイントでインピーダンスがずれてしまっているかを解析し、そのポイントへの修正を加えることが可能です。もし、時間・費用的に余裕があるのであれば基板を作成する前に電磁界シミュレーションを実施することをお勧めします。基板が完成する前に、出力波形、リターンロス特性、TDRのおおよその結果を知ることができ、より確実な設計が可能です。実際のところ、基板設計において、リターンロス規格値を満足することができず、基板改版を重ねるお客様多いです。テキサス・インスツルメンツ社の最新のSDI製品ファミリーはリターンロス性能が改善されており規格を満たし易くなっています。この点を重視して選定頂いているお客様も多くいらっしゃいます。

まとめ

本章では、前回のSDIの使用方法に渡ってお伝えしましたが、本章ではより濃い中身でより実践に近い形でどのような構成で製品を選定していかなくてはならないものなのかをご理解いただけたと思います。