- 公開日:2019年08月07日

- | 更新日:2024年03月28日

LVDSとは? 初心者向け徹底解説

- ライター:4ug

- インターフェース

LVDSインターフェースとはどのようなものなのでしょうか。本記事では、初心者向けにLVDSの基本的な3つの特徴をわかりやすく解説します。LVDSの基本的な原理は、LVDSに限ったものではなく、高速インターフェースの基本にもなっています。本記事を読めば、ほかの高速インターフェースの理解を深めることにもつながります。

LVDSとは

LVDSとは、Low Voltage Differential Signalingの略であり、低電圧差動信号のことを指します。

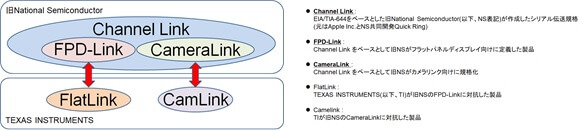

その始まりは、LVDSの前身となるQuick Ring から始まります。Quick Ring は、1992年にApple Computer, Inc(現在はApple Inc.)で、コンピュータ内の既存のローカルバスシステムで動作するマルチメディアシステムとして開発されていました。のちにその設計はNational Semiconductor(NS社。現在はTEXAS INSTRUMENTS 社、以下、TI社)に引き継がれ、並列コンピューティング用の相互接続として再設計されました。

その後、1994年にLVDS ドライバ IC/レシーバ IC「DS90C031/032」が製品化されました。さらに翌年の 1995 年には、LVDS の基本技術が「ANSI/TIA/EIA-644-A」として標準化されました。これがきっかけとなり、通信機器やネットワーク装置、ノートパソコン、液晶モニタなどで多く採用されるようになり、その後、FPD-LinkやFlatLinkといったインターフェースになりました。TI社がNS社を買収する以前の2011年までは、TI社も同様にNS社の対抗製品としてLVDS製品を開発しており、FlatLinkやCamLinkといったインターフェースがありました。現在では、TI社の製品としてすべてラインアップされています。

図. 1 LVDS製品の構図 (2011年以前)

では、なぜLVDSは多くの人にとって難解なのでしょうか。その理由は、私たちが日頃、目にしているインターフェースにLVDSがないからです。日頃、私たちが使用するインターフェースと言えば、インターネットを使用するときにはLANケーブル、DVDを見たいときにはHDMIケーブル、スマートフォンの充電またはデータの転送を行いたいときにはUSBケーブルを使います。このように機器と機器とを接続する目的のインターフェースを、外部インターフェースと言い、これらは私たちになじみのあるインターフェースです。

それに対して、機器の内部で使用される目的のインターフェースを内部インターフェースと言います。この内部インターフェースの一つにLVDSがあります。機器内で使用されているインターフェースであるため、私たちにとってなじみがなく、理解が難しくなっています。そこで、LVDSの特徴を、簡単に解説していきます。

LVDSの特徴(1) 大量のデータを伝送できる(低電圧)

まず、LVDSの1つめの特徴である、大量のデータを伝送できることについて解説します。

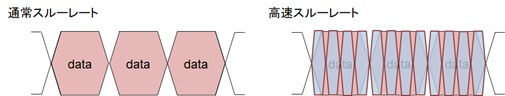

同じ時間軸で大量のデータを伝送しようと考えた場合に、スルーレート(*1)を速くすれば、その分、多くのデータを伝送できます。しかし、その方法は、技術的に限界があり、waferのプロセスに依存することもあります。 また、多くデータを伝送できるといっても限界があります。

*1:High(Low)の立ち上がり(立ち下り)時間

図. 2 高速スルーレートによるデータ伝送

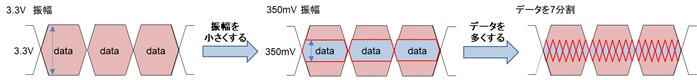

しかし、簡単な方法で大量のデータを伝送できる方法があります。その方法は、振幅を小さくすることです。

3.3Vの高い振幅ではなく、350mVと低い振幅に変えることで、速く、大量のデータを伝送することができます。図. 3のように3.3V振幅のデータ伝送があるとします。3.3Vの電圧振幅がなくとも、350mV程度の電圧振幅でもデータ伝送は可能です。さらにデータを7分割することにより、多くのデータを伝送できるようになります。また、小振幅にしたことで3.3V振幅と同じスルーレートで、より多くのデータを伝送できます。

図. 3 3.3V振幅から350mV振幅

このようにLVDSの特徴として、電圧の振幅レベルを小さくすることにより、より多くのデータを送ることができるという点が挙げられます。これがLVDSの名前にもなっている、Low Voltage(低電圧)という点です。

LVDSの特徴(2) データを安定的に伝送する(差動信号)

次に、LVDSの2つめの特徴である、データの安定的な伝送について解説します。

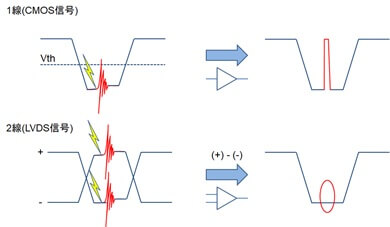

1線のCMOS信号の場合は、Vth(2*)を超えた電気ノイズが入ると意図しない信号(赤で示すパルス)が出力されます。このように外来からのノイズに対して、正しくない信号を伝送してしまいます。

2線のLVDS信号では、1線のCMOS信号同様に電気ノイズは入ります。しかし、同じ電圧レベルのノイズが同時に2線に入り、(+)信号と(-)信号の差分を出力するために、同電圧の変動は+/-で0になり、その結果、出力される信号に電気ノイズは出力されません。つまり電気ノイズの影響を受けないということになります。

2*:Vthとは、それ以上の電圧の場合にHigh信号として認識するボーダーラインのことを言います。スレッショルド電圧と言います。

図. 4 信号線へのノイズの影響

図. 4 信号線へのノイズの影響

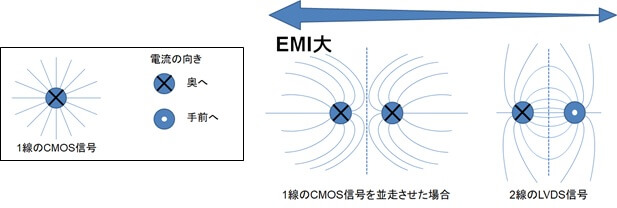

また、外来からのノイズの影響を受けないだけでなく、自身から発生するノイズも小さくしています。

1線のCMOS信号は、電気力線が導体から自由に放散していきます。しかし、LVDSのように電流方向が異なる2線は、同心円状の磁力線は打ち消す方向に働き、電気力線は結合するように働きます。その2線の距離が近ければ近いほど結合性は強くなります。

図. 5 信号が発生するノイズの影響

図. 5 信号が発生するノイズの影響

このように2線(差動)で伝送することで、内外からの電気ノイズの影響を小さくできます。

これがLVDSの名前にもなっている、Differential Signaling (差動信号)という点です。

LVDSの特徴(3) 低消費電力でデータを伝送する

LVDSの3つ目の特徴は、データの伝送を省電力で行えるという点です。

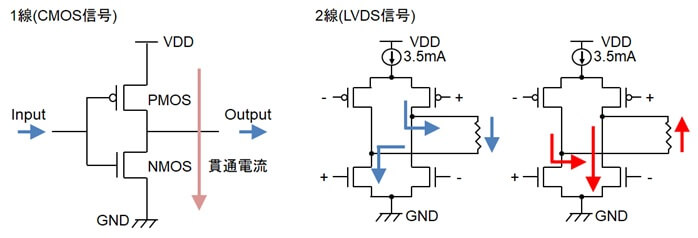

図. 6で示すように、CMOSドライブの場合はスイッチング動作(HighとLow信号を繰り返す動作)をしない状態では、電流がほとんど流れません。しかし、スイッチング動作を行うとき、PMOSとNMOSが同時にONする瞬間が発生します。同時にONした場合、電源からGNDへ貫通電流が発生し、消費電流が多くなります。LVDSドライバでは、定電流回路を内蔵しているために消費される電流値3.5mAと一定に保つことができます。100Ωへ3.5mA流すため、そこへかかる電圧は350mVの低電圧となります。

図. 6 CMOS信号出力とLVDS信号出力の簡易回路図

図. 6 CMOS信号出力とLVDS信号出力の簡易回路図

このように電流を小さくかつ一定に保つことで、消費される電力を小さくできます。通常の1線(CMOS信号)と比べて、低消費電力になります。

まとめ

LVDSの3つの特徴について、解説しましたが、理解は深まったでしょうか。

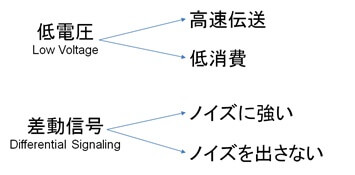

低電圧(Low Voltage)にしたことで高速伝送が可能になり、低消費電力になります。さらに、2線伝送(Differential Signaling)により、ノイズに強くなります。これだけ覚えておけばLVDSを理解したと言っていいでしょう。

図. 7 LVDSの特徴

図. 7 LVDSの特徴

また、補足ではありますが、CMOS信号と比べ、LVDSは長距離伝送が可能となります。

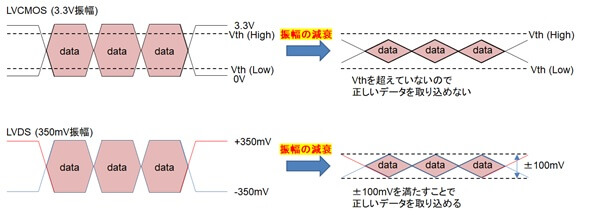

3.3V振幅のLVCMOS信号では、伝送に使用される配線容量や抵抗などにより電圧振幅が減衰します。このように減衰した場合、Vthを満たせずに正しく伝送ができないことがあります。

図. 8 LVCMOSとLVDSの配線容量と抵抗による振幅の減衰比較

図. 8 LVCMOSとLVDSの配線容量と抵抗による振幅の減衰比較

LVDSは、+/-の電圧差でHigh/Lowレベルを判断しているため、振幅が減衰したとしても電圧差が生じていれば、正しいデータを伝送できます。LVDSでは最低±100mV振幅まで減衰してもVthを満たせるため、長距離配線が可能となります。

以上の4つの特徴は、LVDSのみの特性ではなく、多くのインターフェースの特徴とも言えます。スマートフォンやタブレット、ノートパソコンなどで使用されるインターフェースは、LVDSではなく、MIPIやeDPといった内部インターフェースが多く使用されており、MIPIやeDPも同様の特徴を持っています。

TI社にもLVDSやMIPI 、DPといったインターフェース製品があります。こうした製品にご興味があれば、詳細についてぜひご参照ください。

>TI社のLVDS、MIPI、DPなどのインターフェースについて詳しくはこちら

http://www.tij.co.jp/ja-jp/interface/overview.html

Texas Instruments社の製品をお探しの方は、メーカーページもぜひご覧ください。

Texas Instruments社

メーカーページはこちら

参考

TEXAS INSTRUMENTS / LVDS

http://www.tij.co.jp/lsds/ti_ja/analog/glossary/lvds.page

LVDSオーナーズ・マニュアル (日本語版)

http://www.tij.co.jp/jp/lit/ug/jaja442/jaja442.pdf