- 公開日:2020年02月28日

- | 更新日:2025年05月19日

LVDSの設計時に気をつけたい、5つのポイント

- ライター:4ug

- インターフェース

【LVDSとは? 初心者向け徹底解説】では、高速デジタル・インターフェースであるLVDS(小振幅差動信号)の基本的な特徴を解説しましたが、そのLVDSを使用したシステムを設計する際の注意すべきポイントは5つあります。これらの留意点は、CMLやPECLといった他の高速インターフェースにも適用できます。 それではそれぞれのポイントについてわかりやすく説明していきます。

Intra-pair skew: 差動配線は、等長配線が重要

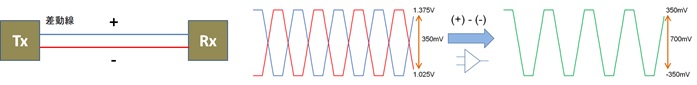

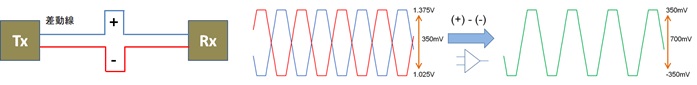

LVDSは、1組の差動信号で情報を伝送し、 この1組の差動信号ペアをレーンと呼びます。差動信号のレーンの片方が短い、または、長かった場合に伝送時間に差が生じてしまいます。これをレーン内、イントラペアスキュー(Intra-pair skew)と言い、このイントラペアスキューが大きいと正しい情報伝達ができなくなります。

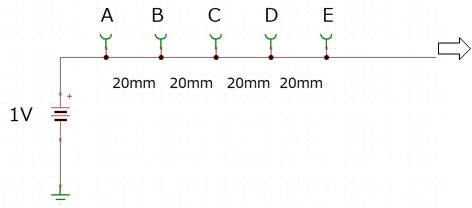

どのような状態なのかを次の図.1~図.3に図示します。それぞれは、トランスミッタ (Tx)とレシーバ (Rx)間を差動配線で接続した様子を示します。 図.1はTxとRxを同じ長さの配線で接続した例です。 この場合、受信した信号波形は、図の右の様になります。 +とーの配線長が等しい(Intra-Pair Skew=0)ければ、送信した信号と同じ信号を受信できます。

図. 1 差動線が等長の場合

これに対し、図. 2は、差動信号のー側に比べ、+側の配線が少し長い時の様子を示します。この場合、+の信号が到達する時間が遅れ、同図右のような波形になります。受信した信号は、送信された信号とは異なる波形になります。 差動信号の正極と負極信号に伝搬時間に差があると、差動間の電圧差がなくなるため、論理が不定になります。 この結果、正確に信号を伝送することができません。

図. 2 差動配線が等長でない場合

この対策として、図. 3の様に、ー側の配線長を伸ばし、+側と同じ長さにすることでRx側へ同じ遅延時間を与えます。それにより、差動間のデータ遅延差の無い伝送を実現出来ます。

図. 3 差動配線が等長になる様に補正した配線

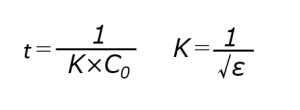

この対策として、図. 3の様に、ー側の配線長を伸ばし、+側と同じ長さにすることでRx側へ同じ遅延時間を与えます。それにより、差動間のデータ遅延差の無い伝送を実現出来ます。信頼性の高い伝送システムを実現するためには、極力、差動信号間の伝搬遅延の差を小さくすることが、重要です。プリント版トレースを伝わる信号の伝搬時間は下記の式で示されます。

t:伝搬遅延時間

C0:真空中の光速

K:波長短縮率

ε:比誘電率

例としてガラスエポキシ基板上、1mのトレースの伝搬遅延時間は、比誘電率 ε= 4.73とすると次のようになります。

- 波長短縮率 K = 0.460

- 伝搬遅延時間 t = 7.25 [ps/mm]

しかし、上記式のように遅延時間がないように等長配線の設計をしたとしても遅延が生じることはあります。その原因は、図. 3のように差動線の配線が一部で離れている場合に経路途中の比誘電率のバラツキで遅延量に差が生じてしまうからです

これを防ぐには、差動信号を図. 4の差動配線結合を考慮して設計することが重要です。これにより、経路途中の比誘電率のばらつきは、両者に等しく作用し、等長配線が等遅延配線にすることができます

。

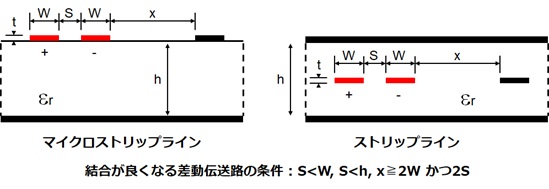

図. 4 差動配線結合

図.4で示した差動伝送路を実現する条件は、以下のとおりです。

- S < W: 差動配線間の距離Sは配線の幅Wより狭くする

- S < h: 差動配線間の距離Sはマイクロストリップラインでは対GNDまでの距離hより狭くする。

ストリップラインではGND間の距離hより狭くする - x > 2S かつ 2W: 隣接信号との干渉を避けるため、他の信号線との距離は配線幅W、

かつ差動配線間距離Sの2倍以上離す。

また、上記の差動伝送路は、差動配線の結合がよくなり、EMI(*1)を低減する効果もあります。図. 4のように設計することで信号ラインから発生する不要輻射(LVDSとは?初心者向け徹底解説内の図.5を参照)を抑制し、高いノイズ耐性といった差動信号がもつ優位点を最大限に活かせることができます。

*1: 電磁妨害ノイズ (Electro Magnetic Interference)

Inter-pair Clock skew(スキュー):差動配線同士も等長配線が重要

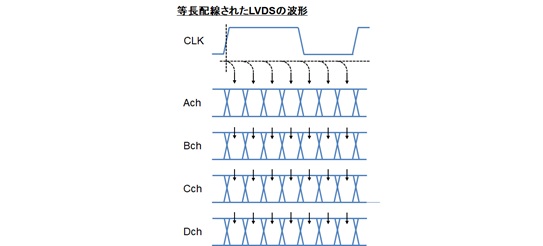

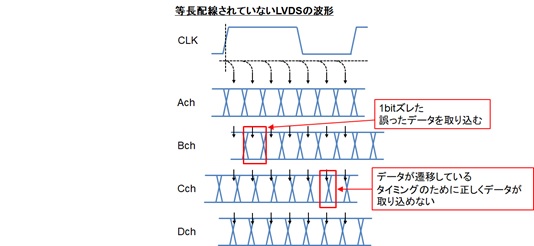

LVDSを用いるシステムでは、クロックと複数のデータを複数のレーンを通して接続することが広く行われており、このようなシステムでは、クロックと、各データの到達時間に差があると正しいデータを受け渡すことができません。このようなIntra-pair Skewに対し、レーン間の到達時間差を、レーン間のInter-pair Clock Skew(インターペアクロックスキュー)と呼びます。 図. 5~図. 6にInter-pair Clock Skewが原因で起きる事象を示します。

この例では、4本のLVDSレーンを使いデータを送信し、それらを、クロックレーンで送られる同期信号を用いてサンプルします。図. 5では、それぞれのレーンに長さの違いがなく、すべて同じタイミングで受信端に到達します。 この場合、すべてのデータは正しいタイミングでサンプルされます。しかし、図. 6の様に、データレーン毎に到着時間がずれると、正しくデータを取り込むことはできません。つまり、信頼性の高い伝送システムを実現するにはレーン同士の配線長を等しくすることが重要です。

図. 5 等長配線されている場合のデータの取り込み

図. 6 等長配線されていない場合のデータの取り込み

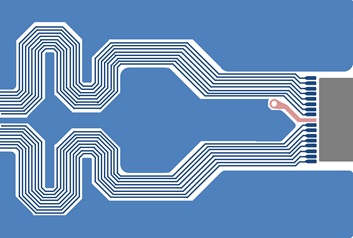

Skew管理は、LVDSだけでなく、LVCMOSロジックを用いたシステム設計でも重要です。映像システムのようにCLKとデータが同期して動くシステムでは、信号の伝搬遅延のばらつきがシステムの信頼性に大きく影響します。また、等張配線していない場合、画像が乱れたり、正しく映らなかったりすることが起こります。 等張配線を実現するために伝送経路を迂回させる手法を使うこともあります。

図. 7 等長配線のレイアウト例

特性インピーダンスを合わせて、不正反射を防止する

「特性インピーダンスを合わせる」「インピーダンスマッチング」という言葉を耳にすることはありませんか?インピーダンスとは何かについて、説明します。図. 8は20㎜離れたプリント板上の5点に1VのDC電源を接続して、各点の電圧を測定する例です。トレースの抵抗を無視すればA点からE点、すべての点で1Vの電圧が観測されます。

図. 8 直流信号と伝番遅延

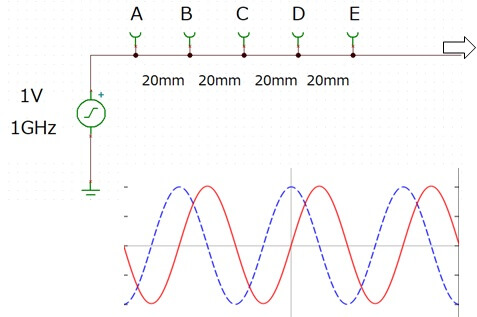

図. 9ではどうでしょうか。 この例では、図. 8のDC電源の代わりに1GHz、1Vの正弦波発生器がつながれています。 A点の観測波形を青とすると、B点では赤の波形が観測されます。 つまり、A点と同じ振幅、周波数の正弦波ですが、位相が遅れた波形になっています。 B点とC点の関係も、青と赤い波形の関係になり、C点とD点、D点とE点も同様の関係になります。信号が波として配線を伝わっています。要するに、信号周波数に対し、伝わる伝送路の遅延が無視できなくなると、信号は波としての性質を持つことになります。

伝送路上を伝わる信号の挙動を知るには、伝送路を分布定数回路として取り扱う必要があります。

図. 9 信号周波数と伝番遅延

分布定数回路において、伝送路は、その単位長さあたりの容量とインダクタンス値で決まり、特性インピーダンスを持つモデルとして取り扱われます。特性インピーダンスは下の式で示されます。これら要素は、導体の幾何学的寸法、取り囲む絶縁媒体の比誘電率、比透磁率によって決まります。これらの条件が変わると伝送路の特性インピーダンスが変わります。

![]()

Z0 : 伝送路の特性インピーダンス

L : 伝送路の単位長さあたりのインダクタンス値

C : 伝送路の単位長さあたりの容量値

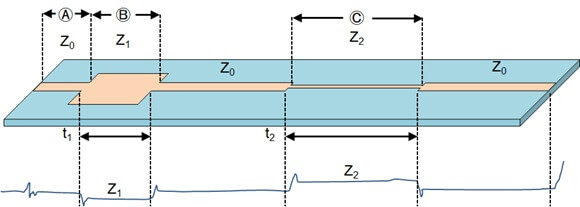

プリント版トレース幅が特性インピーダンスに及ぼす影響を図. 10に示します。

Ⓐの部分:コネクタにつながるトレースは目標のZ0に合うようにトレース幅を設計しました。

Ⓑの部分:その先の、パターンを太くします。 この部分では、単位長さあたりの容量が増え、逆に単位長のインダクタンス値は低下します。この部分で特性インピーダンスが低下します。

Ⓒの部分:トレース幅を標準より細くした部分では、特性インピーダンスが上がります。これは、細いトレース幅により、容量が低下し、インダクタンス値が増加したことによる結果です。

図. 10 トレース幅と特性インピーダンス

異なる特性インピーダンスを持つ伝送路の境界では信号が反射します。 図. 10ではパターン幅が変わる箇所が該当します。反射波は伝送路を伝わる信号に重なり、信号波形を歪ませ、 その波形歪みは通信エラーの要因になります。 このため、信頼性の高い信号伝送を実現するには、できる限り伝送路の反射をなくす事が重要です。

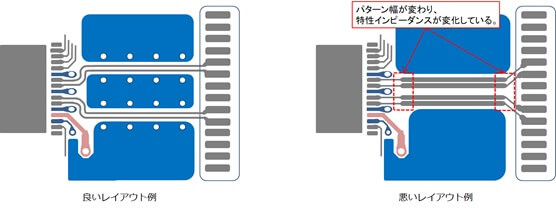

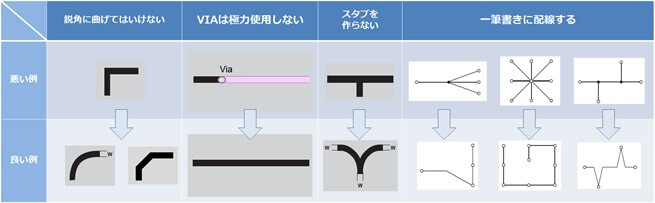

実際に高速差動信号の良いレイアウト例と悪いレイアウト例を図. 11に示します。良い例では、パターン幅は変えずにICからコネクタまで配線されています。しかし、悪い例では直線に配線されていますが、途中でパターン幅が変わっています。そのようにレイアウトした場合に特性インピーダンスは一定に保たれずに反射などにより波形品質が損なわれます。また、パターン幅以外に注意してほしいレイアウトの設計手法として、図.12の表にまとめました。

図. 11 差動伝送路のレイアウト例

図12. 高速伝送路の設計手法

電源ノイズをなくすため、コンデンサをつける

高速で動作するLVDS ICの電源ピンには、適切なバイパスコンデンサの使用が不可欠で、そのIC内部では急激な負荷電流の変動が起こります。電流変動は、電源供給ラインに存在するインダクタンスにより電圧に替わり、ノイズとなって周囲の回路に影響を与えます。TI社のアプリケーションノート 「SIMPLE SWITCHER®PCBレイアウト・ガイドライン」によれば、幅0.5㎜、長さ20㎜のトレースのインダクタンスは、おおよそ20nHと見積もれ、また、500MHzに対するインピーダンスは10Ωとなります。なお、100mAの電流変化は、1Vのノイズとなります。

(参照:http://www.tij.co.jp/jp/lit/an/jaja277/jaja277.pdf)

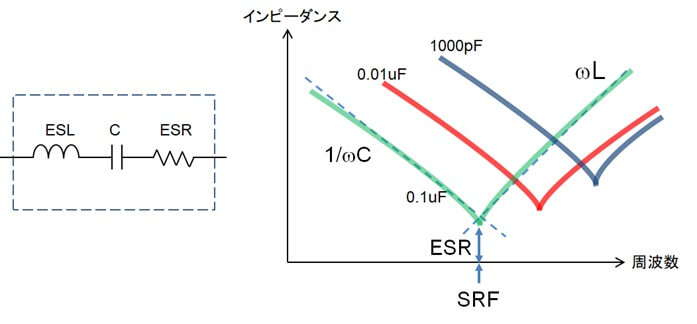

理想のコンデンサでは周波数に反比例してインピーダンスが低下し、大きな容量のコンデンサほどインピーダンスは低くなります。 しかし、実際のコンデンサにはESL (等価シリーズインダクタンス)があります。 大きな容量のコンデンサほど、大きなESLを持ちます。 このため、大きな容量のコンデンサは高い周波数のノイズを効率よく吸収できません。一方、小さい容量のコンデンサは、ESLが小さいため、高い周波数のノイズに対して有効です。

図. 13 コンデンサの回路図及び周波数応答

対策したい周波数帯に効果のあるバイパスコンデンサを選定することが重要です。また、設置する位置も重要です。低周波用の大容量コンデンサは、ICの遠くに置いても問題ありませんが、高周波用の低容量コンデンサは、ICの近くに置く必要があります。

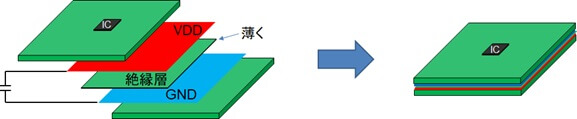

また、コンデンサは使用する絶縁材料により高周波に対する応答特性が変わります。中でもセラミックコンデンサは周波数特性が良く、高周波用途では広く使われ、面実装タイプはリード線がない分、ESLが小さく、自己共振周波数(SRF *2)の高い製品を選ぶことができます。また、プリント版レイアウトもバイパスコンデンサの効果に影響します。そのため、電源、GNDは専用の層を用い、全面を電源層、GND層にし、両層はできるだけ薄い絶縁層で向かい合わせに配置します。これにより、高い周波数特性を持ったコンデンサを実現します(図. 13) (*3)。

図. 14 電源とGNDのプリント版層

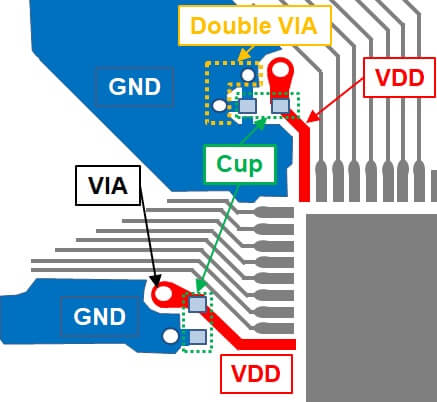

小さな容量のコンデンサは、ICの各電源ピン直近に配置します。 電源ピンとバイパスコンデンサは、可能な限り表面層で、できるだけ短く太いトレースで接続します。 コンデンサの両極は直近でVIAを通して電源、GNDプレ-ンに接続します(図. 14)。 可能であればDouble VIAを使用します。

図. 15電源ノイズ対策コンデンサの推奨配置

*2: ある周波数帯域で共振し、理想コンデンサ特性からインダクタとして機能します。その周波数帯域を自己周波数と言います。

*3: 電源層・GND層を利用したプリント板内部に容量を形成する方法。

伝送距離が長い場合の注意点

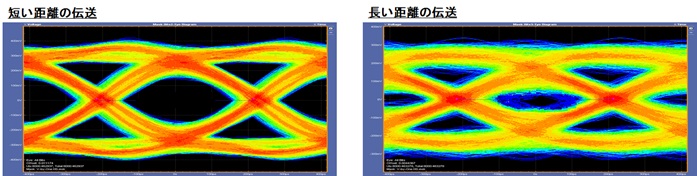

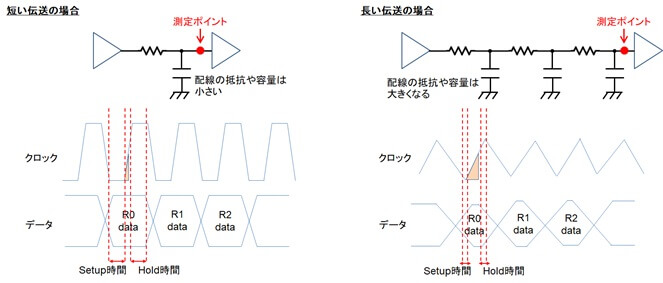

LVDSを用いて数百MHzの信号を数メートルにわたる長い距離伝送する場合、プリント版配線やケーブルの誘電損失や、表皮効果により、信号が減衰します。信号の減衰量は周波数に依存し、高い周波数ほど大きく減衰し、信号の遷移時間が長くなります。 この結果、信号波形は鈍ります。

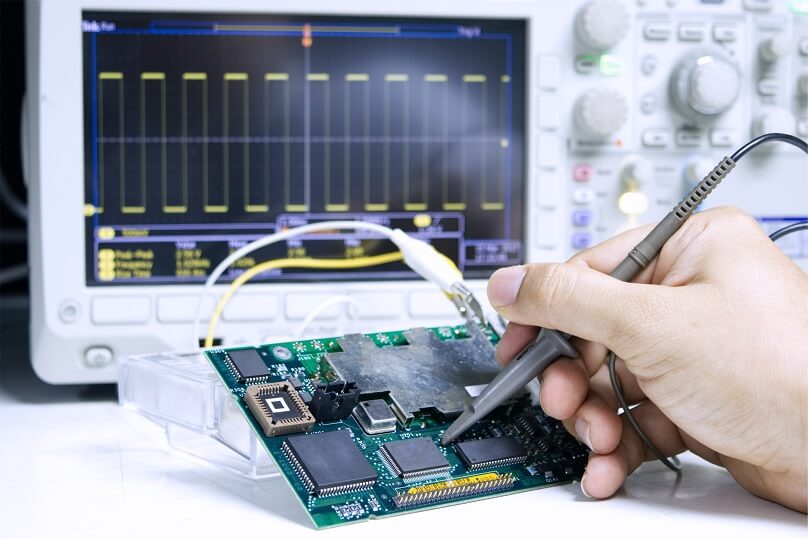

それによりSetup/Hold時間が保たれず、正しいデータの受信ができなくなります。 下記波形は、異なる長さの伝送路を通過した後の信号波形です。 伝送距離が長くなると波形はより大きく減衰し、正しいデータ伝送は困難になります。 長距離伝送を行う際は、事前に、高速のオシロスコープによる波形確認を推奨します。

図. 16 伝送距離による振幅の減衰イメージ

最大到達距離は伝送レートに依存します。 伝送レートが上がる程、信号損失はより大きくなります。これに加え、データレートが上がることに伴い、Setup/Hold時間は小さくなり、タイミング・マージンがなくなります。 その結果、正しい伝送ができなくなります。 伝送レートが低ければ、信号損失は小さく、また、Setup/Hold時間にも余裕があるので、長距離伝送が可能です。伝送レートと最大到達距離はトレードオフの関係にあります。また、最大到達距離は、プリント版配線や使用するケーブルの損失特性にも依存します。

図. 17 ケーブルロスによるSetup/Hold時間

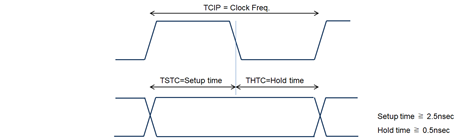

あるデバイスを例に、セットアップホールド時間を検証してみましょう。 あるデバイスのsetup/hold時間を図. 18に示します。

図. 18 Setup/Hold時間の規定例

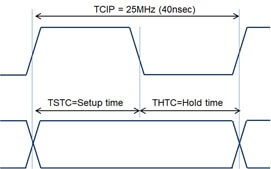

この例では、Setup時間は2.5nsec以上、Hold時間は0.5nsec以上が必要です。 Clockの周波数(TCIP)が25MHzでは(図. 18)、TCIP=40nsecに対して、setup/hold時間は十分な余裕があります。 たとえ、多少波形が鈍ったとしても、正しくデータを取り込むことが出来ます。

図. 19 TCIP=25MHzの場合のSetup/Hold時間のマージン

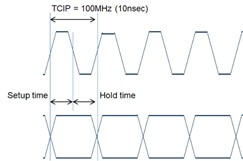

Clockの周波数(TCIP)が100MHz (図. 20)でも、信号損失が無ければ、setup/hold時間には余裕があり問題がありません。 しかし、先ほど述べたように、伝送距離が長くなる、また伝送するケーブルの品質が悪く伝送損失が大きいと、信号が鈍り、十分なsetup/hold時間を確保できません。

図. 20 TCIP=100MHzの場合のSetup/Hold時間のマージン

高速データ伝送が必要なシステムを設計する際は、信号損失を考慮し、伝送された信号品質を事前に確認頂くことを推奨します。 その結果をもとに、適切なケーブルの選定や、伝送距離の制限、転送レートの制限について判断頂き、システム設計を進めます。

まとめ

今回、LVDSを使用したシステムの設計時に注意すべき点について紹介しました。 LVDS以外でも、高速デジタルインタフェースで活用できる内容になります。その為、少しでもLVDS設計について理解が深まり、ご活用頂ければ幸いです。

またLVDSの入門編として下記の記事もありますので、どうぞご参考いただければと思います。

Texas Instruments社の製品をお探しの方は、メーカーページもぜひご覧ください。

Texas Instruments社

メーカーページはこちら

参考資料:

- LVDSオーナーズマニュアル (日本語版最新) http://www.tij.co.jp/jp/lit/ug/jaja442/jaja442.pdf