-

検索結果

-

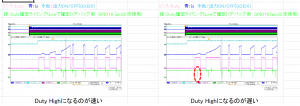

トピック: TBCLK開始タイミングが毎回変わる件

いつも大変お世話になっております。

現在TMS320F28027を使用し、HRPWMでPWM制御をしておりますが、

以下のような問題がございます。①GOIO0がLow→HighでXINT1_ISR割り込みを掛け、その先頭で

SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC=1;

としてPWMクロックを開始しているのですが、Duty Highのタイミングが毎回異なってしまいます。②また、Duty HighのタイミングがGOIO0がLow→Highから大きくズレる場合、Dutyの70%でPWMの計算を開始している仕様にも関わらず、

それよりも早いタイミングでDuty計算が確定してしまいます。(添付の赤丸部分)大変恐れ入りますが、原因につきまして何卒ご教示をお願い致します。

トピック: Part-to-Part Skew

TI社の以下2種類のICについて、Part-to-Part Skewの値についてご教示いただけませんでしょうか。

(部品ごとの遅延時間のばらつきを知りたい。)

データシートを確認したのですが、値が見当たりませんでした。SN74LVC541APWR

SN74LVC574APWRトピック: LMK03328の仕様確認7

お世話になります。データシート(snas668d)の内容に関して ご教示ください。

◆P12 8.13 LVCMOS Output Characteristics (STATUS[1:0]) に記載がない仕様に関して

P12 8.12 1.8-V LVCMOS Output Characteristics (OUT[7:0]) にある tSKEW (same divie value)に該当する仕様で、次の2種の情報を頂けますでしょうか。(1)STATUS0(1pin)と STATUS1(2pin) 間、(2)OUT[7:0]と STATUS0(1pin) 間トピック: LMK03328の仕様確認6

お世話になります。データシート(snas668d)の内容に関して 1点ご教示ください。

◆P26 Figure 31 の記載

トピックタイトル(LMK03328の仕様確認5)の続きとなります。お手数をおかけします。

この接続系の Signal Generatorを水晶発振器(LVCMOS出力) に変更、水晶発振器からLMK03328(SECREF_P/N)までの配線インピーダンスを50ohmとして P37 Figure 45の R29.4,R29.5を有効(50ohm終端を有効)とすれば、P26 Figure 31 にある様な外部抵抗(125 ohm と375 ohm) は不要となる認識で正しかったでしょうか。LVCMOS出力(3.3V max)が 1.65Vとなり、P11 8.9 Clock Input Characteristics (PRIREF_P/PRIREF_N, SECREF_P/SECREF_N)にある SECREF_P/N仕様 (VIH =2.6V以下)を満たせると考え 質問となります。

フォーラム検索:page

フォーラム検索:page