-

検索結果

-

トピック: MSP-EXP430F5529LPについて

TDC7201-ZAX-EVM…..評価ボード

MSP-EXP430F5529LP….CPUボード上記を評価用に使用を検討しています。

PC<—->MSP-EXP430F5529LP 間のインタフェース仕様は公開は可能でしょうか?

よろしくお願い申し上げます。

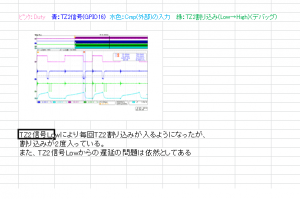

トピック: TZ2割り込みが入らない件に関するご相談

いつも大変お世話になっております。

現在、TMS320F28027にてテクニカルリファレンスマニュアルを拝読しながら、TZ2端子にHigh→Lowをトリガとして、EPWM3AのA出力をパルスバイパルスでLowとする処理を考えています。

しかし、以下のコードで割り込み及びEPWM3AのA出力がLowになりません。

お手数ですが、原因についてご教示願います。

なお、デバックはTBCLKを動かしながら実施しております。init(){

GpioCtrlRegs.GPAMUX2.bit.GPIO16=0;

GpioCtrlRegs.GPADIR.bit.GPIO16=0;

EALLOW;

//TZ割り込み設定 ch3

Pwm3Regs.DCTRIPSEL.bit.DCALCOMPSEL=0b0001;

EPwm3Regs.TZDCSEL.bit.DCAEVT2=0b011;

EPwm3Regs.TZCTL.bit.DCAEVT2=0b10; // EVT2発生時にEPwm3AをLowレベルとする。

EPwm3Regs.TZEINT.bit.CBC=1; // EVT2発生時にTZEINT割り込みをイネーブルにする。

EPwm3Regs.TZEINT.bit.DCAEVT2=1;

EPwm3Regs.TZSEL.bit.DCAEVT2=1; // EVT2のパルスバイパルストリップをEPwm3_TZINのイベントソース

EPwm3Regs.DCFCTL.bit.PULSESEL=0b01; // 周期の最初でマスク開始

EPwm3Regs.DCACTL.bit.EVT2SRCSEL=0; // とりあえずフィルターは使用しない

EPwm3Regs.TZFLG.bit.DCAEVT2=0;PieCtrlRegs.PIEIER2.bit.INTx3=1; // PIEペリフェラルレベルのイネーブル設定 EPwm3_TZINTはINT2.3

EPwm3Regs.TZSEL.bit.OSHT4=1; // TZ4発生時に1ショットでトリップ

EPwm3Regs.TZSEL.bit.OSHT5=1; // TZ5発生時に1ショットでトリップ

EPwm3Regs.TZSEL.bit.OSHT6=1; // TZ6発生時に1ショットでトリップ

IER|=M_INT2;

EDIS;

}// INT2.3

interrupt void EPWM3_TZINT_ISR(void) // EPWM-3

{

EPwm3Regs.TZCLR.bit.DCAEVT2=1; // DCAEVT2の状態をクリア(TRM P253)

PieCtrlRegs.PIEACK.all|=PIEACK_GROUP2; // PIEグループ2のPIE→CPUへの通知を許可}

-

このトピックは

amatsu1が6 年、 7 ヶ月前に変更しました。

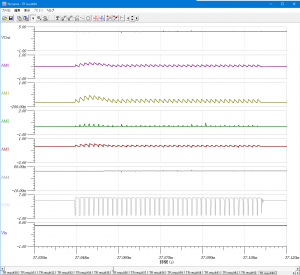

トピック: CAN通信について

Concerto マイコンのCAN通信についての問い合わせです。

CANデータフレームを送信した場合、監視のため自身の送信データを受信します。

このデータフレーム送信と受信との遅延時間の許容範囲はいくらになりますか。以上、よろしくお願いします。

トピック: Resource Explorerについて

サンプルコードを確認するためにResource Explorerを開こうとしましたが、下記のエラーメッセージが表示され開けませんでした。

「There was an error connecting to Resource Explorer. Check your internet connection or try again later.」下記のブラウザで試しても開けなかったのですが、何か条件はあるのでしょうか?

・IE11

・Google Chrome バージョン: 74.0.3729.108(Official Build) (64 ビット) -

このトピックは

フォーラム検索:page

フォーラム検索:page