-

検索結果

-

トピック: LM3424について

お世話になっております。

早速ですが、LM3424についてご質問がございます。LM3424の中にあるError ampのゲイン 及び Error amp周りの抵抗・コンデンサの回路(乗数込み)をご教示願います。

以上、宜しくお願い致します。

トピック: 電源IC

TI製の電源IC UCC28950PWRについて、

動作時にSSEN端子(5pin)とGNDに発生する電圧はいくらでしょうか。

クランプ電圧範囲内で出力されるのでしょうか。

クランプということは電圧があがらないような処理をされているのでしょうか。

もし、クランプ電圧以上の電圧が発生した場合はどうなるのでしょうか。また、この端子でプルアップの閾値電圧が記載されているのですが、

これはどのような機能に使うのでしょうか。もし、データシートに記載があれば、

何ページがご教示ください。トピック: LM3914Vの端子ほか

毎度お世話になります。

早速ですが、LM3914Vについて、ご教示いただきたいことがあります。

①7ピンと9ピンにNCピンがありますが、このピンは内部回路

には接続されていないでしょうか。

隣のピンとショートしても問題はありませんでしょうか。②添付ファイルのような回路で動かしてみたのですが、どのLEDを

光らせた時も、LED1が常に、わずかに光っています。

これの原因について、何が考えられますでしょうか。③抵抗値の調整によっては、LED1から順番に光るのではなく、

例えば、LED2→1→2,3,… といった動作をします。

これは正常な動作なのでしょうか。

正常でないのなら、 何が原因として考えられますでしょうか。以上どうぞ、よろしくお願いいたします。

トピック: BOOT回路

SPRUI77B–August 2016–Revised June 2018の14ページでBOOTのDIPSW回路が乗っています。

TRSTの2.2kΩのプルダウン抵抗の値の理由はありますか。仮に1.6kΩや3.3kΩとなったときに問題ありますでしょうか。

また、GPIO72とGPIO82はプルアップでローアクティブの方が回路が単純化できると思いますが

この回路を採用する特別な理由はありますでしょうか。LT6554評価ボードDC794AのPCBデータを開くことができるソフト名を教えてください。

バージョンも関連しましたら、バージョンも教えてください。トピック: デバッグ時、異常なアドレスの命令が実行される件

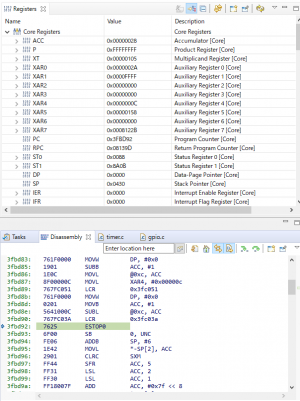

現在、弊社開発環境にてCCSv8, XDS110, TMS320F280049Cを使って開発を行っています。

現象が発生する要因ははっきりしていないのですが、

デバッグ実行時、main関数の最初で停止している状態からResumeボタンを押してプログラムを実行させると、

0x3fb02bといった異常なアドレスの命令が実行されている時があります。おかしな命令をこちらが記述しているということも考えたのですが、

この現象が発生する場合と発生しない場合があり、それらがこの現象と関係がなさそうな変数の初期値や

周辺回路のレジスタなどの値を変更する、GPIOの出力を行う、などで解消したり発生したりしています。このような現象が発生している原因について心当たり等ございませんでしょうか。

よろしくお願いいたします。トピック: コンデンサの必要容量について

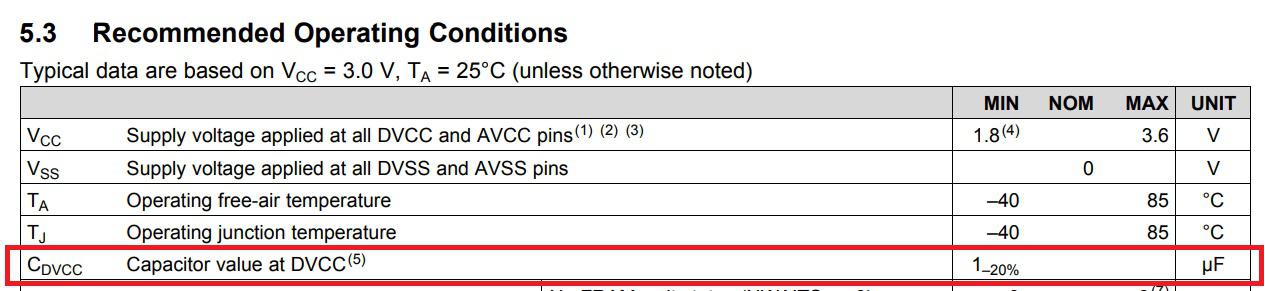

コンデンサの必要容量について2点質問がございます。

1.電源-GND間の必要容量について

DVCC-DVSS間、AVCC-AVSS間のコンデンサ容量を最低限とする場合、どの程度まで下げて良いでしょうか?

※アナログ機能は使用しないものとします

(データシートP120 Figure7-1の1μFの部分)2.VREF-AVSS間の必要容量について

ADCなどのアナログ機能を使用しない場合、VREFとGND間にコンデンサを付加しなくてもよろしいでしょうか?

(データシートP124 Figure7-5の部分)トピック: 2ポート接続時の速度について

毎度お世話になります。

2ポートのUSB HUBとしてTUSB4020を検討しております。

2ポートを同時使用した場合、2ポート共にHighSpeedの速度はサポートしていますでしょうか。

速度制限や条件等あれば教えて頂けないでしょうか。

どうぞ、よろしくお願いいたします。

フォーラム検索:page

フォーラム検索:page