-

検索結果

-

トピック: ±VS端子がOFF時について

毎度お世話になります。

INA828についてご教示いただきたいことがあります。

http://www.tij.co.jp/jp/lit/ds/symlink/ina828.pdf電源端子±VSに電圧が印加されていない時に、

±IN端子、またはREF端子に電圧(定格内の電圧)が印加されていた時、

何か問題が発生しますでしょうか。最大定格はそれぞれ

Signal input pins Voltage ±40V

REF PIN ±18Vありますので、正常動作するものと思われますが、

他社ではREF端子の内部ダイオードによって

電源端子に向かって電流が流れる問題がありました。

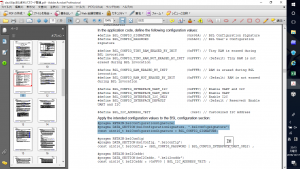

こういった問題が考えられないか、ご確認をお願いします。トピック: BSL Password

BSLパスワードの設定方法について、添付資料の色付け箇所を参考にすれば良いでしょうか?

記述について、どこに記述するのが適当かも知りたいです。

もし添付資料以外にパスワード設定について参考になる資料があれば教えてください。トピック: 電源立ち上げシーケンスについて

TMS320F28377D-EPの電源電圧の立ち上げシーケンスについてですが、

データシートの4.7.1項に記載頂いている電源立ち上げのシーケンスが分からない為ご教示頂けないでしょうか。

VDDIO用の3.3V電源を立ち上げ、その後VDD用の1.2V電源を立ち上げればよいでしょうか。

VDDAとの電源シーケンスはあるでしょうか。また電源立ち上げ時のDSPリセット状態についてですが、

3.3項のPins With Internal Pullup and Pulldownの表3-2にはGPIO;Pullup disabledとありますが、

DSPリセット状態では、ハイインピーダンスかプルダウンされるということでしょうか。

DSPリセット時の各ピンの状態についてご教示頂けないでしょうか。お手数をおかけしますがよろしくお願い致します。

以上です。

トピック: LMZM33603RLR リフロー回数について

LMZM33603RLRについてMSL、Peak Tempについてはデータシートにて確認致しましたが

リフロー回数は何回でしょうか。以上、宜しく御確認の程お願い致します。

hi3807

トピック: SCI BOOT USB変換

SCI BOOTにてプログラムの書き込みを行うときに

SCIーUSB変換をしてUSBインターフェイスとして扱いたいのですが

書き込みソフトウェア(controlSUITE?)は上記に対応していますでしょうか。C2000マイコンのデータシートにおいて

VREFHIAの特記機構として以下の様に

VREFHIA-VREFLOA間にコンデンサを挿入する

と記載されているかと思います。

Place at least a 1-μF capacitor on this pin for the 12-bit mode, or at least a 22-μF capacitor

for the 16-bit mode.挿入するコンデンサとしては電解コンデンサでも宜しいでしょうか?

特に使用するコンデンサの種類については制限・指定はございませんでしょうか?トピック: TUSB8041の仕様について

TUSB8041IRGCRの仕様について質問いたします

1.

端子で“Can be left unconnected” の文言のないPINはオープンでの使用はできないでしょうか?

下記のピンについて内部プルアップ/プルダウンのままで問題ない場合もオープンではなく

外部でプルアップ/プルダウンする必要がありますでしょうか?

Pin32,33,35,36 PWRCTL*/BATEN*

Pin42 GANGED/SMBA2/HS_UP

Pin45 AUTOENZ/HS_SUSPEND

Pin41 PWRCTL_POL2.Pin49 TEST端子について

「9.2.1.2.7 Clock, Reset, and Misc」で外部プルダウンを設定していますが、

オープンでは問題ありますでしょうか?(内部プルダウンではだめでしょうか)3.

立ち上げシーケンスについて

「7.6 Timing Requirements, Power-Up」「9.2.1.2.7 Clock, Reset, and Misc」を確認しましたが

良く分かりませんでした。

・GRSTzにコンデンサを接続した場合、コンデンサはどのように動作するのでしょうか?

・VDD33とVDD11の順序はその後のシーケンス条件に違いが発生するだけで、どちらでも

問題ないという認識で良いでしょうか。もしそうだとした場合、VDD33→VDD11の順で電源が印可されたときと、

VDD11→VDD33で印可されたときのシーケンス条件の違いはなんでしょうか?以上、よろしくお願いします

フォーラム検索:page

フォーラム検索:page