-

投稿者検索結果

-

2018年12月10日 5:16 PM #4496

返信先: TUSB8044について

KJ様 Kevin様

ご回答ありがとうございます。

了解いたしました。

お問い合わせいただきありがとうございました。2018年12月10日 4:36 PM #4495返信先: TUSB8044について

NODOGURO様

ご検討されているクロック発振器のご使用は問題ございません。

XIはクロックソースに接続し、XOはフローティングのままにしてください。VH VLの最小値最大値の規定はありません。

発振器などの外部クロック使用する場合の唯一の要求仕様は、

・基準クロック±100PPM またはそれ以上の周波数安定性を持つ

・絶対Peak-to-peakジッタが50ps未満

または USB3.0 ジッタ伝達関数を適用した後、Peak-to-peakジッタが25ps未満

です。また、D+,D-はプルダウン不要です。

以上、宜しくお願い致します。

KJ2018年12月10日 2:38 PM #4493返信先: LM7171AIMの最小出力電圧について

MJ様

お問い合わせいただきありがとうございます。

±15V両電源で使用したときの出力電圧は、データシートP.5 6.5 ±15V DC Electrical CharacteristicsのVo Output Swingの規定に従います。

例えばRL=1kΩの場合、typ値で-13V~+13Vまで出力可能です。もう一点、オフセット電圧への影響が考えられ、データシートP.5 6.5 Vos Input Offset Voltageで規定され、typで1mVとなります。絶対値で表されますので±1mVです。

0Vを入力したときのオフセット電圧は、回路のゲイン倍されて出力されます。例えば、ボルテージフォロアの回路を構成して0Vを入力したときに1mVの入力オフセット電圧が存在したとすると、

出力のオフセットは+1mVまたは-1mVとして出力されます。最小値は-1mVになります。

ゲインが10の場合は+10mVまたは10mVになります。最小値は-10mVです。ご不明点がございましたら、ご連絡いただけますでしょうか。

以上、よろしくお願いいたします。

FI43101

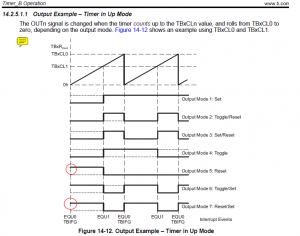

2018年12月10日 2:07 PM #4486トピック: TimerB Output Mode 極性について

フォーラム内 MSP430TimerBを用いたOutputModeについて質問させて頂きます。

OutputModeの5Resetもしくは7ResetSetを用いてシーケンスを

作ったのですが、最初のHighレベルのOutが出ません。

この最初のHighレベルはどのレジスタによって設定されているのでしょうか。

試しに他のMode4Toggleに変更してみると図の4の様に最初はLowレベルから始まって

トグル出力が出てきておりますので、OutputModeには切り替わっている様です。

よろしくお願い致します。Attachments:

2018年12月10日 2:06 PM #4485返信先: FB回路へのノイズ重畳

totora様

ご返信ありがとうございます。

引き続きご確認いただければと思います。

本来の負荷接続前(最初に示した条件下)でかつ故障の前は出力電圧約2.2V、出力電流計算値-0.1A程度になります。

故障後は出力電圧0.8Vです。

こちらについては、想定されている電圧が0.8Vにもかかわらず、2.2Vが出力されてて故障後に0.8Vとなるということなのでしょうか?

totora様にて故障とご判断されている事象が判断出来ておりませんので、改めて確認をさせてください。1.どのような事象から故障とご判断されておりますか?

2.負荷電流は0.1A程度を想定されておりますか?今回、ブレッドボードにてご評価されているとのことですが、本製品のような電源回路の設計においては配線抵抗/容量など大きく影響受けますので、可能な限り配線は短くコンデンサはICを直近においてご評価いただくことをおすすめします。

確かに4/5で問題が置きておりますので、何かしら設定方法に問題があるかと思います。

上記の確認事項を再度ご教示いただけませんか?以上、よろしくおねがいします。

forest2018年12月10日 2:00 PM #4483FI43101様

>0.033uFに対して、差異がないように複数個使いしていただく等でご対応いただけませんでしょうか。

現状と今後のセラコン供給状況を考慮すると複数個使用することで使用数が増えるのは避けたいです。

よって、GRM155B31H223KA12Dの使用を前提として

添付ファイルの通り検証を行いました。

0.033uF駆動時との差異は見られないため、今回の条件であれば使用可能でしょうか>値が低すぎると、より頻繁な再充電パルスが必要になり、実効最大デューティサイクルが低下する可能性があります。

TPA3220DDWRでは最大デューティサイクルを制限することで再充電量を確保しているということでしょうか

最大デューティサイクルを制限 = 最大のスピーカ出力電圧を制限 という認識で正しいでしょうか

これが発生すると電圧波形がクリップされることになるかと思います。

音声波形を確認しても今回の使用用途での最大電圧は実験を行った3つのコンデンサすべて

同一(12Vp-p)であったため、本用途にてこの問題は発生していないと判断してよろしいでしょうか以上、ご確認お願いします。

Attachments:

2018年12月10日 10:10 AM #4481返信先: LMH1983のPLL3使用に際して

大変申し訳ございません。

先程の回答ですが訂正が入る可能性がございます。

先程の回答は保留とさせてください。

再度回答をいたします。混乱させてしまい大変申し訳ございませんがもう少しお待ちいただけますようお願いいたします。

Best regards,

Kevin2018年12月10日 9:26 AM #4480返信先: LMH1983のPLL3使用に際して

お時間いただきありがとうございました。

以下に回答いたします。>ただ、一点だけ追加でご教授いただきたいのですが2フレーム相当の時間経過後に

>Never Alignへ変更との事ですがその間HVFに対してなんらかの同期信号を入力し続ける必要はございますでしょうか?

>※GENLOCKモードか完全自走モードであるか等動作モードによって同期信号の有無や追加で設定等が変わる場合は

> そちらに関してもご教授いただきたいです。

(回答)

HVFの入力クロックは不要です。

これを実施する理由は内部のPLL3 State MachineをRESETするところにあるためです。

本来、電源起動時にRESETされるべき内容ですが、

これがうまくRESETされないケースがあり、その対策として本ステップを必要とします。

起動時に正常にRESETがされないと、PLL3のクロック出力のDUTYが崩れ、波形が乱れてしまいます。>おそらく今回ご回答いただいた500msはどの同期系に対しても有効な値になっているのではと思いますが、

>本来の設定値として同期信号の有無にかかわらず500ms程度待ってから設定を変更すれば良いのか、

>同期信号を入力しつつその同期信号に応じたフレーム時間換算で2フレーム以上待ってから設定を変更する必要があるのか

>ご教授いただきたく存じます。

>※2フレームはどこを基準に2フレームとなっているのか知りたいです。

(回答)

入力クロックは不要で、500ms待って設定変更でOKです。Best regards,

Kevin2018年12月10日 9:10 AM #4477はい、

ADCxy = ADCxINTy (x=[A, B, C], y=[1, 2, 3, 4])

との認識で問題ございません。

表記が統一されておらず、ご不便をおかけいたしますが、読み替えていただければと思います。

2018年12月10日 9:07 AM #4476kkk様

メーカーへ確認させていただきました。

MSPflasherはMSP Debug stackを使用してベリファイが実行されます。

このプロセスはPSAアルゴリズムによって、チェックサム計算を行っているようです。PSAについては、JTAGインタフェースのユーザーズ・ガイドにて記載されておりますので、合わせてご確認ください。

MSP430 Programming With the JTAG Interface (Rev. AD)

2.3.7 Verifying the Target Memory

2.6 JTAG Features Across Device Families 注(5)以上、よろしくお願いいたします。

Cruijff2018年12月7日 5:43 PM #4474確認不足でした。

ADCxyがADCxINTyという認識でよろしいでしょうか。

(x=[A, B, C], y=[1, 2, 3, 4])2018年12月7日 5:39 PM #4473ADCINT1は、PIE Channel Mappingの中で、INT1に割り当てられております。

ご確認のほど、よろしくお願いいたします。

2018年12月7日 5:35 PM #4472Figure 13-1.の方、確認致しました。

PIEチャネルマップにADCの割り込みがADCごとに4つ、合計12つあると思いますが、

4つの変換終了割り込みと1つのADCイベント割り込みの計5つあるのですが、ADCINT1が割り当てられていないのでしょうか?よろしくお願いいたします。

2018年12月7日 5:25 PM #4471TMS320F28004xのADC割り込みにつきましては、ADCモジュール毎に、

- 4つの変換終了(End-of-Conversion)割り込み: ADCxINTy

- 1つのADCイベント割り込み: ADCx_EVT

があります。

ADCxINTyは、16個のSOCの中から4つを選択して割り込みとして、選択したSOCの変換終了時に発生する割り込みになります。

ADCx_EVTは、変換結果を後処理ブロック(Post Processing Block)で処理された結果からゼロクロス検出、上限・下限比較により発生する割り込みになります。この割り込みは、Figure 13-9におけるADCEVTINTになります。

全体像は、Figure 13-1. ADC Module Block Diagramが参考になるかと思います。

ご確認のほど、よろしくお願いいたします。

2018年12月7日 5:08 PM #4470返信先: LMH1983のPLL3使用に際して

ご対応の程ありがとうございます。

本件現在メーカに確認を行っておりますが、大変申し訳無いことに時間を要しております。

大変恐縮ですがお時間頂けますようお願いいたします。Best regards,

Kevin -

投稿者検索結果

-

検索結果

-

TimerBを用いたOutputModeについて質問させて頂きます。

OutputModeの5Resetもしくは7ResetSetを用いてシーケンスを

作ったのですが、最初のHighレベルのOutが出ません。

この最初のHighレベルはどのレジスタによって設定されているのでしょうか。

試しに他のMode4Toggleに変更してみると図の4の様に最初はLowレベルから始まって

トグル出力が出てきておりますので、OutputModeには切り替わっている様です。

よろしくお願い致します。

フォーラム検索:page

フォーラム検索:page