-

検索結果

-

トピック: 外部クロックについて

毎度お世話になります。

ADS8519について教えていただきたい内容があります。

http://www.ti.com/lit/ds/symlink/ads8519.pdf

データシートP4の「電気的特性」-「デジタル出力」の「外部クロック」項目に、External clock (can run continually but not recommended for optimum performance)

(連続使用可能だが、最高特性のためには推奨しない)と記載があります。具体的にどのようなことを述べているのでしょうか。

外部クロックにてデータを取り出す場合、常時クロックを入力すると、

A/Dの性能を最高に引き出すことができないと行くことでしょうか。

もしその場合、A/Dのどの性能に影響しますでしょうか。以上どうぞ、よろしくお願いいたします。

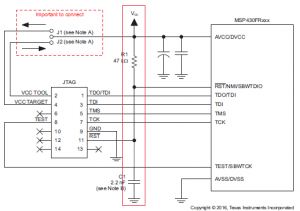

トピック: USB Bootについて

USB Bootについて質問させて頂きます。

データシートにおいてUSB Bootに関する備考として

以下のように記載されておりますが、

The USB Bootloader will switch the clock source to the external crystal oscillator (X1 and X2 pins).

A 20-MHz crystal should be present on the board if this boot mode is selected.

USBによるBootは外部クロックとして水晶発振器でないと

使用できないでしょうか?

現在、3.3VオシレーターをX1に接続している回路で設計しておりますが、

3.3VオシレーターでUSB Bootを使用する方法はございませんでしょうか?トピック: 内蔵LPFをカットする方法

毎度お世話になります。

ADS8685とADS8695に関する問い合わせがありますので、

ご確認頂けないでしょうか。ADS8695データシート

http://www.tij.co.jp/jp/lit/ds/symlink/ads8695.pdfADS8685データシート

http://www.ti.com/lit/ds/symlink/ads8681.pdf【問い合わせ内容】

上記ICには、約10kHzのLPFが内蔵されておりますが、それをカットすることは可能でしょうか。

データシートの端子情報と、7.2 Functional Block Diagramを見る限り、カット(無効)にすることは

出来ないかと思いますが、いかがでしょうか。もし可能であれば、方法を教えていただきたくお願いいたします。

以上どうぞ、よろしくお願いいたします。

お世話になります。

DS90UB964-Q1が対応している同軸ケーブルのインピーダンスは50Ω

ですが75Ωは使用不可能でしょうか。

可能であればどのような回路(終端など)にすれば良いかご教示下さい。以上、よろしくお願いいたします。

トピック: TCA6507のVILについて

今度は TCA6507のVIL( Low-level input voltage)について質問させてください。

○回答希望日:11/15(木)

●TCA6507データシートでは、VILは、1.65 V ≤ VCC ≤ 1.95 Vにおいては、0.3Vmaxと

なっていますが、I2Cの規格では、0.3VDD(1.8Vで使用しているので、0.54V)となっています。I2C規格と不整合があるようですが、間違いだったりしないでしょうか?

マスタのVOLmaxと不整合が生じており、困っております。※I2Cの仕様は、NXP社 UM10204 I2C バス仕様およびユーザーマニュアルの

表 9. SDA およびSCL I/O ステージの特性を参照しています。

https://www.nxp.com/docs/ja/user-guide/UM10204.pdf

フォーラム検索:page

フォーラム検索:page