-

検索結果

-

トピック: MSP430のノイズ耐性

現在、TI製マイコンを搭載した製品にてノイズ耐性が弱いことがわかり、対策を行うため調査中です。

対象のマイコン:MSP430FR6989IPZ (TI製)

現状で、JTAG用端子のTESTピンに静電気を印加すると消費電流が増加する不具合となります。

JTAGモードがONになるということでしょうか。

この現象はMSP430シリーズすべてで発生する現象でしょうか。

あるいは同じシリーズでも静電気ノイズ耐性が強いものがあるのでしょうか。

また、消費電流が増加した状態では電池寿命には影響しますが、その他の機能には

影響はないと考えていますがいかがでしょうか。

他の製品にもMSP430シリーズのマイコンを使用しており、確認したいです。

急で申し訳ありませんが、今週中(11/19)にご回答を頂きたいです。(早い方がいいです)トピック: ベクタアドレスの記述について

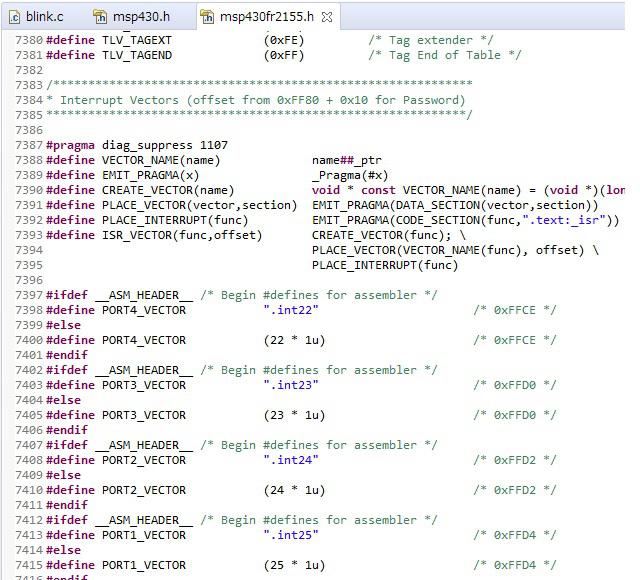

添付ファイルの様に、割り込みソースとベクタアドレス(C言語上記述)が一覧となった表はありませんでしょうか?

ユーザーズマニュアルなど探してみましたが、Word Addressとなっていました。

よろしくお願い致します。トピック: バス制御端子について

バス制御端子について質問させて頂きます。

バス制御端子の内、RNW(read not write)とOE(output enable)は

意識的にどの様に使い分けを行えば宜しいでしょうか?また、WEを含めバス制御端子は同時に動作可能でしょうか?

他のデバイスにてロジックを組んで16bitバスのUB,LB信号を

生成しようと考えております。トピック: SN74AHC1G08について

SN74AHC1G08について

データシート1ページ目にて以下の記載があるのですが

Schmitt-Trigger Action at All Inputs Makes the Circuit Tolerant for Slower Input Rise and Fall TimeVIH、VILで規定しておりヒステリシス電圧の記載もなさそうなのですが

シュミットトリガとして使用できるのでしょうか(ヒステリシス電圧ありましたら教えていただけないでしょうか)以上、よろしくお願い致します。

フォーラム検索:page

フォーラム検索:page