-

検索結果

-

トピック: SN6505Bの出力コンデンサ

ご担当者 様

お世話になっております。

主題の件ですがSN6505Bのデータシートに、ソフトスタート機能により出力コンデンサが大きい場合の突入電流を抑制するとありますが、出力コンデンサ容量の上限値の規定はありますでしょうか?

ご回答お願い致します。

トピック: INA819の入力バイアス電流について

ご担当者 様

お世話になっております。

主題の件ですが、INA819データシートのFigure 10. Input Bias Current vs TemperatureとFigure 11. Input Offset Current vs Temperatureについて縦軸が【nA】になっておりますがデータシートの別の記載から【pA】の間違いということでよろしいでしょうか?

以上よろしくお願い致します。

トピック: ADS1260のノーマルモードノイズ除去について

ご担当者 様

お世話になっております。

主題の件ですが、ADS1260を【50SPS_Sinc1】【60SPS_Sinc1】のデータレートとフィルタで使用して50Hzと60Hzのノーマルモードノイズを除去したいのですが、内蔵クロックを使用した場合、内蔵クロックの精度はデータシートより±2%のため除去できる周波数も最大±2%ずれることになるのでしょうか?

(50Hzの場合、49Hz~51Hz、60Hzの場合58.8Hz~61.2Hz)

また、仮により高い精度で50Hz、60Hzを除去する場合、精度と温度ドリフトの特性が良い外部クロックを使用するということになるのでしょうか?

以上、ご回答よろしくお願い致します。

トピック: ADS1260アナログ入力端子過大入力電圧保護

ご担当者 様

お世話になっております。

主題の件ですが、アナログ入力端子の過大入力電圧保護について下記の考え方で良いかご教授ください。

データシートの【7.1 Absolute Maximum Ratingsの注記文】【9.3.1.1 ESD Diodes】【10.1.2 Input Overload 】の解釈として仮に入力の最大定格を超える電圧が印可される場合も抵抗等で電流を±10mA以下に制限すれば保護が可能ということでよろしいでしょうか?

具体的にはセンサ断線時にアナログ入力端子に-1V程度が印可される可能性があるため入力端子の直前に1kΩ(-1mAに制限)を実装予定です。尚【11.2 Analog Power-Supply Clamp】に記載されているアナログ電源のクランプも同時に行います。

以上、ご回答よろしくお願い致します。

トピック: SN74AHC273のリセット信号について

現在、 TI社製のSN74AHC273 を実装したボードの評価を行っております。

そこで、リセット の波形確認を行いました。

波形を確認すると、立ち上がり/立ち下がりに段がある波形となっております。立ち上がり時に、17ns間 0.837V~0.97V の段がある

→VIL 0.9V以下を跨っている

立ち下がり時に、18ns間 1.95V~2.13Vの段がある

→VIH 2.1V以上を跨っている

【質問】

VIL, VIHを跨る場合、懸念することがあればご教授していただきたいです。トピック: TPS6590379のクロックについて

(1) TPS6590379について16.384 MHzの水晶振動子を前提で回路の記載がありますが、

16.384 MHz水晶発振器の出力をOSC16MINに入力した場合、シーケンサは動作しますでしょうか?(2) GATE_RESET_OUT OTPビットとOSC16M_CFG OTPビットの説明は

どの資料に記載がありますでしょうか?トピック: HD74LV1G**との比較

【 ご質問内容 】

HD74LV1G**からの代替検討中です。

<依頼内容>

相違点を確認したく、比較表の提供をお願い致します。留意点などの見解も頂けると幸いです。

また、可能であれば、「ヒステリシス電圧」、「電源オフリーク電流」、「等価内部容量」についてもお願い致します。以下が、対象部品となります。

1)HD74LV1G04ACME-E

2)HD74LV1G08ACME

3)HD74LV1G125ACME-E

4)HD74LV1G126ACME

5)HD74LV1G14ACME-E

6)HD74LV1G32ACME以上 よろしくお願い致します。

トピック: SN74LVC245A

TI社製 SN74LVC245Aについて、ご教授ください。

現在、SN74LVC245A を使用して、5V -> 3.3V レベル変換をしております。

以下が回路構成となります。

入力信号 5V -> SN74LVC245A (VCC=3.3V) -> 出力信号3.3V

出力信号の波形を確認すると、約5Vのオーバーシュートがありました。

この原因は、ドライブ能力が強いからという認識で合っていますでしょうか?

(5V -> 3.3V変換の構成によるものでは無い)

以上、お手数ですがご回答の程、よろしくお願いいたします。

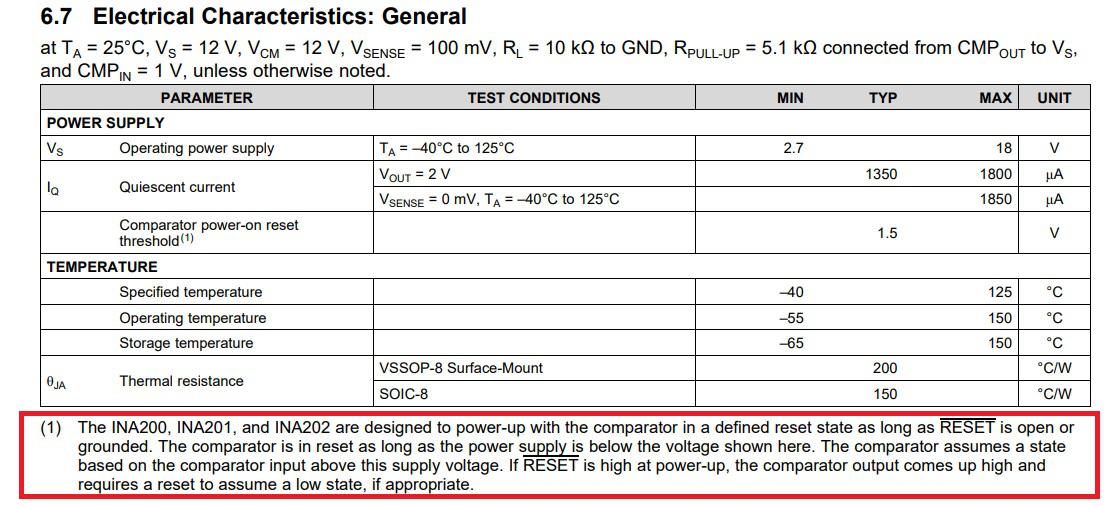

トピック: INA200について

いつもお世話になっております。

INA200の評価ボードの評価を行っております。

希望する動きは確認できたのですが、電源投入時に必ずCMP OUTがHIになります。

Vin+とVin-を短絡した状態でもCMP OUTはHIになります。

電源投入後、RESET SWをONするとCMP OUTはLOWとなります。

本ICは電源投入後に必ずRESETしなければならないのでしょうか?

フォーラム検索:page

フォーラム検索:page