-

検索結果

-

トピック: TPS3828-33DBVのSIMモデルについて

TI社製 TPS3828-33DBVについてです。

シミュレーションを実施したく、SIMモデル(IBIS, PSPICE, S-Para)をご提供いただけないでしょうか?

トピック: DP83867IRRGZの電源構成について

TI社製 EHT PHY DP83867IRRGZ の電源構成について、

教えてください。

2電源構成と、3電源構成がありますが、

2電源構成で使用した際、機能的制約、スペック的制約がありましたら、

教えてください。

トピック: DP83867のLoopback機能について

TI社製 Eth PHY DP83867のLoopback機能について、教えてください。

①PC等からPHYにパケットを送信する構成でも、Loopback機能を使用することができますでしょうか?

②Loopback機能を使用した際、送信したパケットがそのまま返ってくるのでしょうか

(パケットの中身を編集しない)

以上、ご回答のほどよろしくお願いいたします。

トピック: 未使用品の処理について

お世話になります。

未使用ピンの適切な処理方法について、こちらのTech Noteを拝読しました。

https://www.ti.com/lit/an/sboa204a/sboa204a.pdf現行品は適切な処理方法とは異なっており、下記のような処理を行っています。

1)非反転・反転入力をGNDに接続し、出力ピンをFloatingさせる

2)非反転・反転入力・出力ピンをGNDに接続する

この場合、どのような影響が考えられるかご教示頂きたいです。

下記のように考えているのですが正しいでしょうか。

・双方の入力ピンをGNDに落としていても僅かに電位差が生じれば、電位差に応じて出力ピンから出力しようとする

・出力ピンが浮いていればその分の電圧が出力され、出力ピンがGND接続ならば無用な電流が消費される

・結果としてこれら電圧・電流変動が使用中のピンにcross talkして、望ましくない影響を及ぼすトピック: LM5157への周辺接続部品選定について

お世話になっております。

LM5157につきまして、弊社で搭載検討が初めてのため、

メーカーのデータシートやApplication Report (SNVA824–August 2018)なども一通り一読させていただきましたが、弊社の想定仕様としての計算方法をご確認させていただきたく。

■お問い合わせの内容2点

弊社の想定仕様:入力電圧 12V,出力電圧 24V,出力不可電流 100mA以下

① 一般的な昇圧アプリケーションとして、インダクタの詳細計算過程や、計算から推奨されるインダクタ値をご教示ください。

② ダイオードの参考型番例をご教示ください。

お手数で御座いますが、ご回答宜しくお願い致します。

-

このトピックは2 年、 3 ヶ月前に

GT さんが編集しました。理由: お名前/会社名が本文内に記載があったため、削除しました。

GT さんが編集しました。理由: お名前/会社名が本文内に記載があったため、削除しました。

トピック: MCUのAD変換ポートへの印加電圧について

TMS320F28375DのAD変換ポートについて質問がございます。

1) データシートのNoteにV_DDA+0.3V以下にすることを求められておりますが、この電圧を超過した場合は保護ダイオードに電流が流れ、場合によっては破損し得るという理解で良いでしょうか。

2) どの程度の電流であれば耐えられるのかは8.1 Absolute Maximum RatingsのInput clamp currentを考慮すれば良いでしょうか。つまり、20 mA以下であれば問題ないのでしょうか。

以上よろしくお願いいたします。

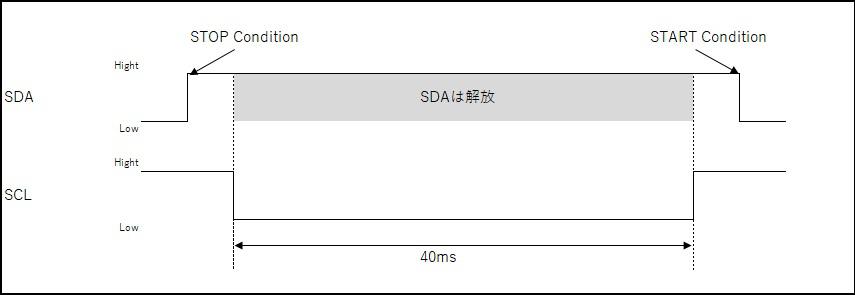

トピック: I2C Read/Write Bit設定について

現在I2Cセンサを使用するソフトウェアの開発を行っています。

I2Cを取り扱うのが初めてのため、基本的な質問で恐縮ですがRead/Write Bitについてお教えください。

MSP430側をマスターとし、スレーブアドレス:0x28のセンサと通信を行います。

通信の流れとして、スレーブアドレス0x28をUCB0I2CSAに渡すのが一番最初のステップになると思っています。

この時、Read/Write Bitの設定はどのように行ったら良いのでしょうか。

最初はスレーブアドレスを1Bitシフトし7Bit~1Bitでアドレス設定,0BitにRead/Writeを設定すれば良いのかと思い、UCB0I2CSAに8Bit渡すつもりでした。

しかしユーザーガイドの38.4.9 UCBxI2CSA Registerにて9~7Bitは無視されるとの記載があり混乱しています。

認識間違い等ございましたらご教授頂けますと幸いです。

下記にI2Cレジスタの初期設定等を示します。

今回割り込みを使用しない形での実装で進めています。

void initGPIO()

{

// Disable Interrupts before altering Port Mapping registers

__disable_interrupt();

// Enable Write-access to modify port mapping registers

PMAPPWD = 0x02D52;//I2C Pins

P2SEL |= BIT1 | BIT2;

P2MAP1 = PM_UCB0SCL;

P2MAP2 = PM_UCB0SDA;

// Disable Write-Access to modify port mapping registers

PMAPPWD = 0;

}void initI2C()

{

UCB0CTL1 |= UCSWRST; // Enable SW reset

UCB0CTL0 = UCMST + UCMODE_3 + UCSYNC; // I2C Master, synchronous mode

UCB0CTL1 = UCSSEL_2 + UCSWRST; // Use SMCLK(20MHz), keep SW reset

UCB0BR0 = 200; // fSCL = SMCLK/200 = ~100kHz

UCB0BR1 = 0;

UCB0I2CSA = 0x28; // Slave Address is 0x28

UCB0CTL1 &= ~UCSWRST; // Clear SW reset, resume operation

} -

このトピックは2 年、 3 ヶ月前に

フォーラム検索:page

フォーラム検索:page