-

投稿者検索結果

-

2020年12月24日 9:34 AM #14360

> どのCHにどんな異常が発生しているのか詳細をご教授頂けないでしょうか。

OUT0-7に0Vを出力するため、アドレス0x14-1Bに0x8000を設定したところ、

OUT1,3,5,7に-10Vや-5Vが出力します。>また異常が発生したCHのレジスタデータをフィードバックして頂けないでしょうか。

DACのレジスタをreadして確認してほしいとの意味でしょうか?

もしそうでしたら、設計した基板ではSDO接続していないため確認できません。>考えられる原因としてClock等にノイズが入っておりシリアルデータが正確に反映されていない可能性がございます。

レジスタのアクセス間隔を長くすると、OUT1,3,5,7の出力も期待した0Vになる為、

ノイズは関係ないと思っております。

初期設定時のレジスタアドレスの順番やWait時間に問題がないかについて、回答をお待ちしております。-

この返信は4 年、 11 ヶ月前に

maida さんが編集しました。

2020年12月23日 7:10 PM #14348K2様

承知しました。

そうしましたらお手数ですが下記リンクの”2.6.4 Saving Device Configurations”と”2.8.2 Logging Data to a File ”

に従ってレジスタとログを保存いただき、送付いただけますでしょうか?

https://www.mouser.co.uk/datasheet/2/405/snau163c-461330.pdf

そちらをベースに確認させていただければと存じます。

以上、お手数ですがよろしくお願いいたします。

QT

2020年12月23日 4:41 PM #14343QT様

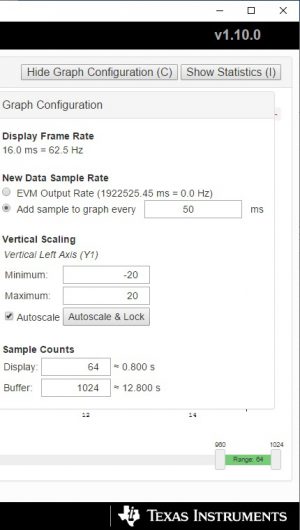

設定の件ですが、EVM Output Rateで使う場合と、100ms程度で使う場合があります。

デフォルトは50msが選択されます。

50msを選んでも表示は数秒に1回程度ですし、画面に連動し、logも2~3秒間隔でしか取得できていません。Attachments:

2020年12月22日 4:47 PM #14333kenoknさん

ご対応ありがとうございます。

プロジェクトをインポートした後に、プロジェクトを右クリック->Properties->Generalより、Compiler versionでTI v4.2.1を改めて選択してからApply and Closeを押していますでしょうか?

基本的に、コンパイラのバージョンとビルドオプションが同じである場合、CCSのバージョンが異なっていても、ビルド出力は同じであるはずと考えます。

たまに、インポートしたプロジェクトに対しコンパイラや設定が正しく反映されていない場合があります。インポートした後に、再度全く同じ設定になっているか確認し、念の為Applyを押していただければと思います。

もしくは、お手数ですが、CCv9.3.0にて新規にプロジェクトを作成していただき、同じソースコード、同じ設定でビルドした際の出力結果をご確認いただけますでしょうか?

上記の方法でも差分が発生してしまう場合、可能であれば具体的にどの部分に差異が生じているかご教示いただけますでしょうか?

以上、よろしくお願い致します。

2020年12月22日 3:50 PM #14331maida様

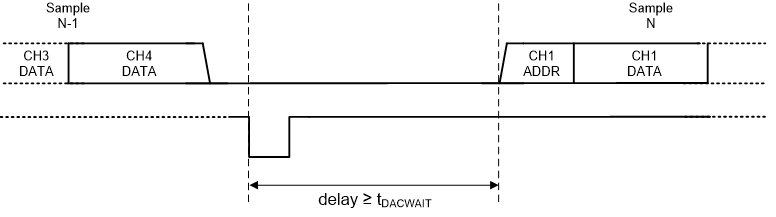

■LDACの立ち下りエッジから再度アドレス0x14(or 0x15)に16bitのデータを設定を行う(CSの立ち上がりエッジ)までの待機時間だと認識しておりますが、Synchronous mode時に、この時間を2.4us以上に設定して頂くことでデータシートの規定内での動作となります。

また5(LDACの立ち下がりエッジ)から再度5(LDACの立ち下がりエッジ)の間隔を2.4us以上に設定して頂く事でもデータシートの規定内になると存じます。

■タイムチャートのSample N-1はStreaming modeでの動作となるため、CH3とCH4の間にCS Highの時間はございません。

■申し訳ございません。

初期設定時の待機時間について、まだ明確な事が分かっていない為、分かり次第ご連絡できればと存じます。

年末のため回答にお時間がかかってしまう可能性がございます。ご了承ください。

以上、宜しくお願いいたします。

Nishie

2020年12月22日 9:52 AM #14330ご回答ありがとうございました。

Synchronous modeの場合、Tdacwaitは、LDACの立下りエッジから後続のLDACの立下りエッジまでの待機時間とのとこで承知しました。

現状、LDACpinを20ns Lowから再度アドレス0x14(or 0x15)に16bitのデータを設定を行うまでの間に待機時間は、25us程度を想定しています。確認になりますが、頂いたタイムチャートのCH3 DATAレジスタにアクセスしてから、CH3 DATAレジスタにアクセスするまでに必要なCSのwait時間は、データシートに記載されておりますtcshighの25ns以上で宜しいでしょうか?

また、#14023項の質問の繰り返しになりますが、電源起動後DAC81408に初期設定として以下の様にレジスタ設定を行っていますが、レジスタ間のアクセスのwait時間を80nsとしたところうまくいきません。

1.アドレス0x03に0x0A04 // device power-down mode解除

2.アドレス0x0Bに0xAAAA // OUT7-4 ±10V設定

3.アドレス0x0Cに0xAAAA // OUT3-0 ±10V設定

4.アドレス0x06に0x0FF0 // LDAC trigger (synchronous mode)

5.アドレス0x14に0x8000 // OUT0 0V

6.アドレス0x15に0x8000 // OUT1 0V

7.アドレス0x16に0x8000 // OUT2 0V

8.アドレス0x17に0x8000 // OUT3 0V

9.アドレス0x18に0x8000 // OUT4 0V

10.アドレス0x19に0x8000 // OUT5 0V

11.アドレス0x1Aに0x8000 // OUT6 0V

12.アドレス0x1Bに0x8000 // OUT7 0V

13.アドレス0x0Eに0x0010 // register LDAC

14.アドレス0x09に0xF00F // power-down mode解除

レジスタアクセスの間で、CS High時間を80usよりも長く設定する必要があるところがございませんでしょうか?

5から12までのDATAレジスタ同士のアクセスの間隔に25ns以上のCSのwait時間が必要とすると、DATAレジスタ同士以外の1から2,2から3,3から4,4から5,12から13,13から14のレジスタのアクセス間隔で、CS High時間を80usよりも長く設定する必要があるところがございませんでしょうか?2020年12月21日 8:37 PM #14326maida様

お待たせして申し訳ございません。

TdacwaitはSynchronous modeの場合、LDACの立下りエッジから後続のLDACの立下りエッジまでの待機時間となります。

下の図の2番目の波形がLDACになります。

また、レジスタ設定において

5.LDACpinを20ns Low

から再度

1.アドレス0x14(or 0x15)に16bitのデータを設定

を行うまでの間に待機時間はどのくらい設けておりますでしょうか。

10.3.1.2.1 DAC Register Synchronous and Asynchronous Updatesの最後の行に記載されている「In both update modes a minimum wait time of 1 µs is required between DAC output updates.」につきまして、1us は 2.4usの誤記となります。

以上、宜しくお願いいたします。

Nishie

2020年12月21日 10:36 AM #14316kenoknさん

お待たせいたしました。

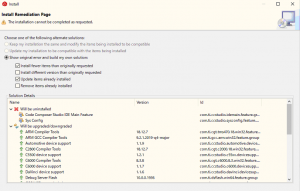

メーカーの方へ今回のエラーメッセージ(Available_Software_err.png)について確認させていただいたところ、複数の更新プログラムのインストールが試行されたことを示しているようですが、根本的な原因を特定できないとのことです。

ですので、お手数ですが以下の2つの方法のどちらかをお試しいただけますでしょうか?- 現在のCCSv9.3.0を一度アンインストールし、再度CCSv9.3.0のインストールと、MSP430コンパイラv4.2.のインストールを行う。

- 別のバージョンのCCSをインストールし、MSP430コンパイラv4.2.1をインストールする。その後、別バージョンのCCSへインストールしたMSP430コンパイラを、CCSv9.3.0から参照、もしくはコピーする。

1の場合、アンインストール時にWorkspaceを削除する必要はございません。再起動時にエラーが出た場合は、以下のパスよりアプリケーションの起動をお試しいただければと思います。

<CCS INSTALL DIR>\ccs\eclipse\eclipse.exe2の場合、弊社ではCCSv8.3.1へ、MSP430コンパイラv4.2.1をインストールし、CCSv9.3.0で使用可能なことを確認致しました。以下に手順を記載致します。

- CCSv8.3.1をインストール後、Install New SoftwareよりMSP430コンパイラv4.2.1をインストール。

- インストール完了後、以下のパスに”msp430_4.2.1″が存在していることを確認出来ます。

<CCS INSTALL DIR>\tools\compiler - CCSv9.3.0のメニューバー->Window->Preferences->Code Compiler Studio->Build->Compilersより、Tool discovery path:へ上記のパスを追加(Add)します。※下図を参照ください。

- もしくは、”msp430_4.2.1″自体をCCSv9.3.0の以下のパスへコピーする。

<CCS INSTALL DIR>\ccs\tools\compiler - 上記の手順を実施後、一度CCSv9.3.0を再起動することで、Projectを右クリック->Properties->Generalより、Compiler versionでTI v4.2.1が選択可能になるかと思います。

以上、お手数ですがよろしくお願いたします。

2020年12月21日 9:13 AM #14312返信先: BQ24770の動作についての質問

ご回答ありがとうございます。

質問1について

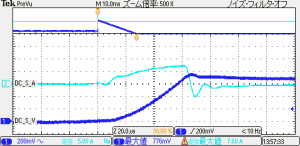

スルーレート波形を添付致します。

ch1が出力電圧となります。

WDT時はスルーレート11.66V/Sに対し、電圧変動時は0.33V/msとなっております。

(WDT時のメジャーが入っておりませんので目測となります)質問2について

提示頂いた波形測定は時間を要しますので少々お待ちください。

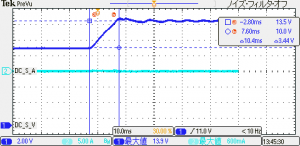

参考としまして、跳ね上がり時のスイッチング波形を添付致します。

ch1は出力電圧となります。出力コンデンサ追加は可能ですが、こちらも少々お時間が必要となります。

周辺回路情報ですが、

出力コンデンサ:高分子コンデンサ33uF 2個、セラコン22uF 1個

入力コンデンサ:セラコン22uF 2個、セラコン0.1uF 1個

コイル:8.2uHその他必要な定数はございますでしょうか。

よろしくお願いいたします。

2020年12月18日 7:06 PM #14311トピック: 入力電圧 最大定格について

フォーラム内 スイッチ、ロジック入力電圧の最大定格について

データシートに上限値は7Vと記載がありますが、

下限値が記載されていないため、

教えて頂けないでしょうか?2020年12月18日 4:32 PM #14308トピック: TIのエラーの対処法について

フォーラム内 Code Composer StudioTIのCode Composer StudioでAM6548のR5Fのプログラミングを行っていたところ、以下のようなエラーが発生しました。

このエラーの原因と対処法を教えてください。Attachments:

2020年12月18日 4:29 PM #14306トピック: BQ24770の動作についての質問

フォーラム内 電源ICお世話になっております。

BQ24770のチャージャーICの動作に関しまして質問がありますので

ご対応の程、宜しくお願いいたします。質問1、Watch Dog Timer動作について

Watch Dog Timerが働いた際、セル数に合わせたMax Charge Volgateに変更されますが、

WDTによる変更の場合、外部からの変更に比べて電圧変動のスルーレートがかなり早く、

問題が発生しています。

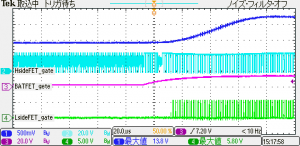

WDT時のスルーレートを調整する方法は御座いますでしょうか。質問2、BATFETをONした際の動作

低負荷状態時でBATFETをONし、その接続先も低負荷の場合、低負荷モードによりLsideFETの動作

を停止する個体があります。(動作周波数を600kHzに設定した場合)

停止する事に問題はありませんがこの状態でBATFETをOFFした際、出力のシステム電圧がMax Charge Volgate

以上の電圧に跳ね上がる問題が確認されています。

この問題について回避方法はございますでしょうか。お手数をお掛けしますが、ご回答よろしくお願いいたします。

2020年12月18日 9:52 AM #14255umamitiさん

ご返信ありがとうございます。

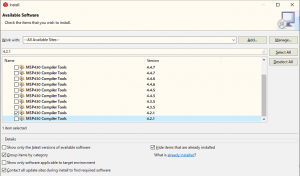

> インストール時に、MSP430コンパイラ以外の内容をあわせて選択していませんでしょうか?

いいえ。以下のようにMSP430コンパイラのみを選択しています。(添付: Available_Software_check.png)

その後、[Next]ボタンでインストールを開始しようとするとエラーが発生してしまいます。(添付:Available_Software_err.png)よろしくお願いいたします。

2020年12月18日 9:29 AM #14251kenoknさん

ご確認いただきありがとうございます。

インストール時に、MSP430コンパイラ以外の内容をあわせて選択していませんでしょうか?

エラー内容の詳細は不明ですが、CCS v9.3におけるsysconfigの更新エラーについて、何か依存関係が抜けているようです。再度、インストール時の選択画面で、MSP430コンパイラのみにチェックを入れているかご確認いただければと思います。

以上、よろしくお願い致します。

2020年12月17日 9:33 PM #14246hisanori 様

ご投稿頂きありがとうございます。

Linker command fileからご確認頂けます。

プロジェクトの作り方によるところもございますが、特に変更をしていない場合はTOOLS以下のcc26xx_app.cmdなどがそれに当たり、FLASH_LAST_PAGEにCCFGの設定を格納するように設定されています。

デフォルトの状態でCCFGは.outファイルに含まれているようになっており、出力されたmapファイル (例えばFlashROM内のsimple_xxx.map) にて、FLASH_LAST_PAGEにCCFGが格納されているのがご確認頂けます。

ubo

-

この返信は4 年、 11 ヶ月前に

-

投稿者検索結果

-

検索結果

-

トピック: 入力電圧 最大定格について

入力電圧の最大定格について

データシートに上限値は7Vと記載がありますが、

下限値が記載されていないため、

教えて頂けないでしょうか?トピック: TIのエラーの対処法について

TIのCode Composer StudioでAM6548のR5Fのプログラミングを行っていたところ、以下のようなエラーが発生しました。

このエラーの原因と対処法を教えてください。トピック: BQ24770の動作についての質問

お世話になっております。

BQ24770のチャージャーICの動作に関しまして質問がありますので

ご対応の程、宜しくお願いいたします。質問1、Watch Dog Timer動作について

Watch Dog Timerが働いた際、セル数に合わせたMax Charge Volgateに変更されますが、

WDTによる変更の場合、外部からの変更に比べて電圧変動のスルーレートがかなり早く、

問題が発生しています。

WDT時のスルーレートを調整する方法は御座いますでしょうか。質問2、BATFETをONした際の動作

低負荷状態時でBATFETをONし、その接続先も低負荷の場合、低負荷モードによりLsideFETの動作

を停止する個体があります。(動作周波数を600kHzに設定した場合)

停止する事に問題はありませんがこの状態でBATFETをOFFした際、出力のシステム電圧がMax Charge Volgate

以上の電圧に跳ね上がる問題が確認されています。

この問題について回避方法はございますでしょうか。お手数をお掛けしますが、ご回答よろしくお願いいたします。

フォーラム検索:page

フォーラム検索:page