-

検索結果

-

コンパイラ(TI v4.2.1)のインストール方法について、ご存知の方がおられましたら教えてください。

Code Composer Studio(CCS)は「 Version: 9.3.0.00012 」を使用しております。

CCSのHelpタブより、”Install New Software”をクリックし、Work withを –All Available Sites–にして”4.2.1″で検索したのですが、見つかりませんでした。(”4.2″で検索すると TI v.4.2.7 は見つかるのですが…)

どうぞよろしくお願いいたします。トピック: オペアンプの過電圧保護

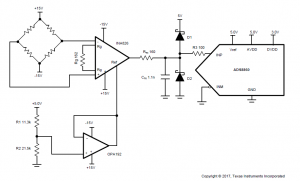

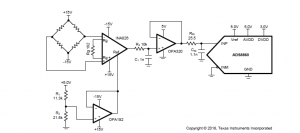

現在 計測アンプINA826のアプリケーションノート「SBAA277A」と類似した回路を設計しております。

(添付資料の回路※最初に投降した回路の画像は誤りです。)

断線時のオペアンプの過電圧保護としてこの資料にならいOPA320への電流の制限を行う予定です。断線の場合、すぐに改善するわけではないので保護としては長時間保護が必要となりますが、この保護方法は瞬間的ではなく

長期的な保護が可能と考えてよいでしょうか?またこの保護方法はOPA192でも同様に可能でしょうか?(OPA192で過電圧保護が可能であればオペアンプをOPA192に統一できるため)

OPA192のデータシートを確認したところ可能のように見えるのですがOPA320とOPA192のデータシートにて過電圧保護の項目

の記載内容がことなるためご回答をお願いします。よろしくお願い致します。

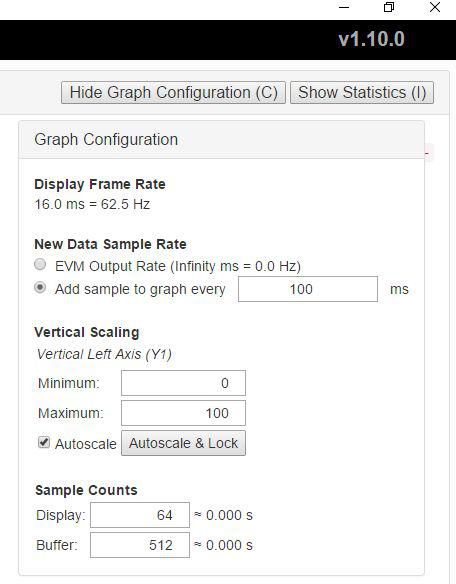

FDC1004の評価基板の動作確認にSensing Solutions EVM GUI Toolを使用していますが、急に

データの表示、更新が非常に遅くなりました。

2,3か月前に使用したときはICのConfig設定を100S/sと設定すると10msec毎にデータ取得できましたが

今は2~3秒に1回の更新スピードです。

基板を変えても、PCを変えても症状は変わりませんでした。(tool V1.9.4)

TIのサイトに新しバージョンのtoolがあったので、インストールしてみましたが、それでも更新

スピードに変化はありませんでした。

toolを使用して評価を進めたいのですが、うまくデータが取れなくて困っています。

対処法についてご教示のほどよろしくお願いいたします。

フォーラム検索:page

フォーラム検索:page