-

検索結果

-

トピック: 差動アンプの使い方について

いつもお世話になっております。

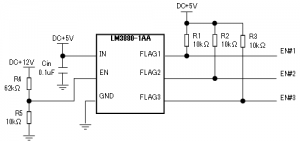

差動アンプを使って添付回路図のようにしたいと考えております。

A案は初段にINA826を入れて出力を分岐してそのまま出力する方と

さらにアンプする方に分ける、一般的回路は実現可能だと思います。

今回はB案のように初段にINA826を2個並列接続して分岐したいと

考えております。B案の実現は可能でしょうか?

単純に可能だとよいのですが、可能ですけどパターン化の際、〇〇の

引き回しに注意する等、アドバイスを頂けると助かります。

よろしくお願いいたします。*ちなみになぜB案を検討しているかと申しますと10倍を抵抗値を

変えて他の倍率にも変更可能にしたいと考えております。

B案ですと10倍側INA826の抵抗値を変更すればよいのですが、

A案ですと2段目のアンプゲインも変更必要な為、簡単に変更できないか?

と検討しました。sonodera

トピック: F28335 GPIOについて

お世話になっております。

F28335のGPIOで出力設定を行おうとしているポートがあります。DSP電源の3.3Vの起動してからGPIOの出力設定(初期設定)が終わるまでの間、

上記、出力設定予定のポートはHIGH,LOWどちらになりますでしょうか?電源起動直後からGPIO出力設定を行うまでのHIGH,LOWの設定を変えることは可能でしょうか?

お世話になります。

データシートのTable 4-1. Signal Descriptionsに、

ADCINA0,A1,B1には50 kOhmの内部プルダウン抵抗が存在するとの記載があります。

精度に影響するため、こちらの最大・最小値をご教示頂けないでしょうか。以上よろしくお願いいたします。

トピック: watchdog起動後のリセット要因取得

ウオッチドッグのタイムアップ後に、リセット信号を発生させて再起動していますが、再起動を検知するためマニュアルSPRUHM9-Oct. 2014よれば、WDCRのWDFLAGが使えると思いましたが、デバッガのWdRegsの構造体には定義されていません。どのレジスタを参照すれば、判断できるでしょうか、

よろしくお願いします。トピック: 水晶振動子について

水晶振動子について質問です。

データシート(JAJSEZ6H)のP68 表5-15に記載されているCL1,CL2というのは外部負荷容量のことでしょうか?

水晶振動子のCLとは違う?

下記リンク 4-1 に記載されているC1、C2という認識でよろしいでしょうか?

https://www.macnica.co.jp/business/semiconductor/articles/basic/127525/評価基板のLAUNCHXL-F28379Dでは下記部品を使用されておりますが、データシートのMax24pFを超える外部負荷容量が

接続されております。問題ないのでしょうか?

水晶振動子:ATS100B-E (±30ppm、CL:18pF、Co:7pF、ESR:60ohm)

外部負荷容量:36pF(C3、C4)また、外部負荷容量12pF~24pFとのことですが、上記リンクの式 CL=(C1xC2)/(C1+C2)+4に当てはめると、

選定される水晶振動子のCLは10pF~16pFの物という理解でよろしいでしょうか?以上よろしくお願いいたします。

フォーラム検索:page

フォーラム検索:page