-

投稿者検索結果

-

2020年8月21日 6:07 PM #13083

返信先: 差動増幅回路の安定性について

ET 様

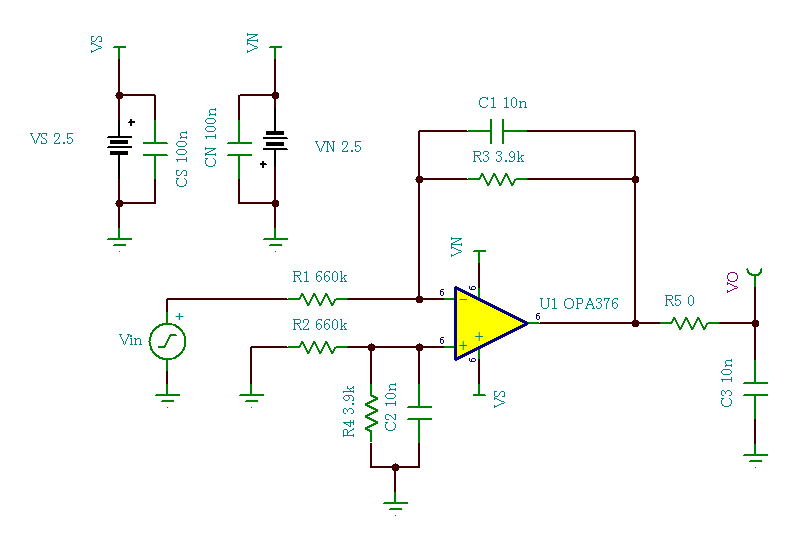

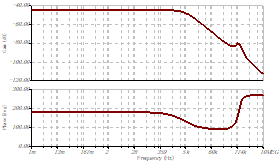

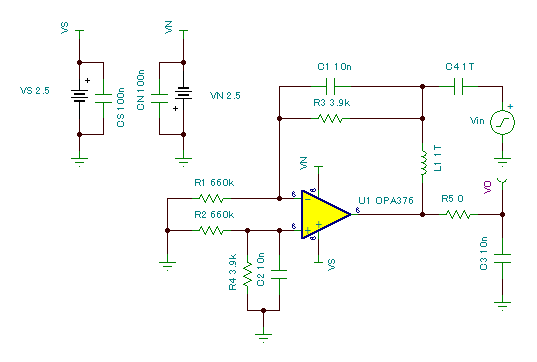

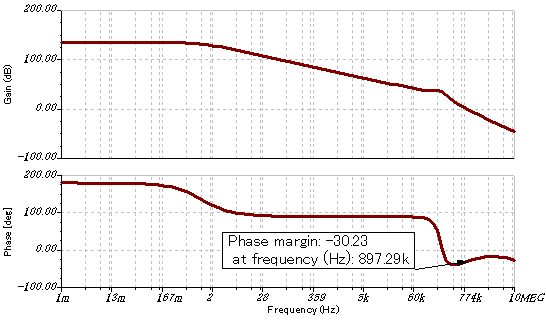

Closed LoopのGain特性は以下の通りで、回路図と合わせてご確認下さい。

出力負荷が10nFですので、「位相余裕がない」条件です。

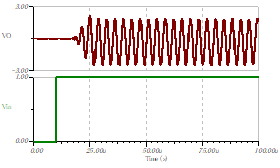

次にTransient解析のStep応答についての例ですが、発振しています。

「実機で何をどのように確認するのか?」についてですが、もちろんFRAなどを使用して

ループゲインを確認することは可能ですが、Simulationで行ったStep応答でも

Loopの安定性を簡易的に確認することが出来ます。

Simulationと実機との差についてコリレーションを取り、その差を埋めることが重要です。FRAで測定する場合はSimulationで用いた手法とは異なりますので、詳細に関しましては

測定器メーカにお問い合わせ頂けますと幸いです。

Kato

2020年8月21日 4:18 PM #13080返信先: 差動増幅回路の安定性について

ご回答ありがとうございます。大変勉強になります。

最後の質問と申し上げておりましたが、

すみません、もう少々追加させていただきます。・また、実際にご使用になるClosed LoopでGain Peakの有無をご確認下さい。

Closed LoopのGain Peakの有無が何を意味するのかご教示頂けないでしょうか。・実機にてご確認頂くことを推奨させて頂きます。

通常、実機で確認する場合もシミュレーション回路のように

LとCを接続し、FRAで測定するのでしょうか。

もしそうであれば1TF,1THは現実的でないと思いますが、

どの程度の定数を用いるのでしょうか。2020年8月21日 3:39 PM #13079返信先: 差動増幅回路の安定性について

ET 様

OpAmpを用いて負帰還回路を構成する場合、ご用途にもよりますが、Gain Marginは7dB~10dB、

Phase Marginは45°~60°以上を一つの目安としています。

低周波領域であれば、帯域との兼ね合いもありますが、個人的にはPVT変動を考慮し、

特にPhase Marginは60°以上を確保するようにします。

また、実際にご使用になるClosed LoopでGain Peakの有無をご確認下さい。

いずれに致しましてもSimulationはあくまでSimulationですので、実機にてご確認頂くことを

推奨させて頂きます。

その方が得られるものが多いと思います。初歩的な内容になりますが、ご案内させて頂きましたOpAmpのWebinarにご参加頂けますと幸いです。

Kato

2020年8月21日 11:40 AM #13075返信先: ACFコンバータのCclump計算方法

wtidesigner様

追加でお問い合わせ頂き、ありがとうございます。

頂いたお問い合わせの件ですが、TI社に確認致しましたので、以下の内容で回答させて頂きます。

上記①の計算式に記載しておりますV_BULKminについてですが、

現在確認して頂いているExcel Design tooの場合、VBulk_min_tgtの値ではなく、

以下の式のようにExcel Design tool上のVin_Browninの値をもとに計算された値を用いております。

※上記の式は Vin_typeがACの場合の式となっております。Vin_typeがDCの場合は以下の式となります。

例えば、Vin_typeがACで、Lk=2.5uH, fsw=160kHz, Nps=5.25, Voutnom=20V, Vin_Brownin=80Vにて計算を行った場合、以下の値となります。

V_BULKmin=93.8896V

Cclamp_rec=0.353μF(DCバイアスの影響を考慮しない場合(Drea_clamp=0%))

Cclamp_rec=0.588μF(DCバイアスの影響を考慮した場合(Drea_clamp=-40%))

以上、よろしくお願い致します。

Ottey

2020年8月21日 8:27 AM #13073返信先: 差動増幅回路の安定性について

ET 様

こちらの位相線図は180°から始まっておりますが、

これは”Vout” / “Vin” =–Aβ になるからだと考えれば良いでしょうか。→ ご理解の通りです。

実数ではなく、振幅と位相の成分を持つ複素数とお考え下さい。

また、位相は180°からスタートしておりますが、位相遅れ0°に相当します。また、このボード線図の場合、下記認識で正しいでしょうか。

・位相余裕はゲインクロスオーバー周波数における位相の絶対値

・位相が0°となる周波数においてゲインが>0dBのとき発振する→ 上記のループゲイン特性に対するPhase MarginとGain Marginの考え方についてはご認識の通りです。

今週の8/19にオペアンプに関する第1回目のWebinarを開催致しましたが、第2回目を9/2に予定しております。

次回は「AC特性の基礎」で、既にご存知の内容かと思いますが、ご参考までにご案内させて頂きました。初心者のためのオペアンプセミナー

https://www.macnica.co.jp/business/semiconductor/events/texas_instruments/134775/Kato

2020年8月20日 6:25 PM #13072返信先: 差動増幅回路の安定性について

ご回答くださりありがとうございます。

こちらの位相線図は180°から始まっておりますが、

これは”Vout” / “Vin” =–Aβ になるからだと考えれば良いでしょうか。

また、このボード線図の場合、下記認識で正しいでしょうか。

・位相余裕はゲインクロスオーバー周波数における位相の絶対値

・位相が0°となる周波数においてゲインが>0dBのとき発振する

※実際には余裕が必要だと思いますが。2020年8月20日 2:50 PM #13071返信先: VBACKUPにバッテリーを接続する

gen0005様

お問合せありがとうございます。

お問合せにつきまして回答させていただきます。

内部レジスタのBBCH_REGレジスタ(データシートP80 TABLE6-49)において最下位1bit(BBCHEN)がバックアップ電源への充電を制御する設定となります。こちらが”0”となっていれば充電制御はDisableとなり充電はされない状態となります。

また、データシートP55 6.6 Backup Battery Managementの内容も合わせて参照いただけますと幸いです。

2020年8月20日 7:42 AM #13063返信先: 差動増幅回路の安定性について

ET 様

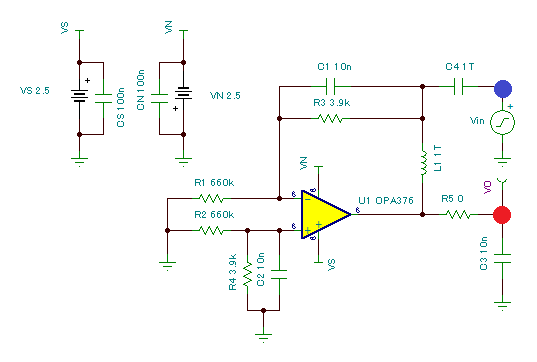

TINA-TIの場合には信号源と出力Pinにより自動的にGain特性を取得することが出来ます。

入出力電圧ノードの指定が必要ということでしたら、「”Vout” / “Vin” = “赤のノード” / “青のノード”」になります。

Kato

2020年8月19日 7:41 PM #13062返信先: 差動増幅回路の安定性について

ご回答くださりありがとうございます。

>→ ループゲインAβになります。

こちらで同様のシミュレーションを行いたいため、

具体的にどの部位の電圧比か教えて頂けないでしょうか。あるいはTINAの場合、特に電圧比を取らずとも

ループゲインが選択肢としてあるのでしょうか。2020年8月19日 3:57 PM #13061返信先: ACFコンバータのCclump計算方法

ご回答ありがとうございます。

急な設計依頼があり、ご連絡が遅れました。上記⓵の計算式ですとExcel Design toolの各値は

Lk=2.5uH, fsw=160kHz, VBULKmin=70V, Nps=5.25, Voutnom=20V ですからCclamp=0.253uFと計算されます。

DCバイアスの取り扱いを含めても 0.253/(1-0.4)=0.422uF で 0.588uFになりません。

ご連絡の式で合ってますか?

2020年8月19日 9:16 AM #13054返信先: 差動増幅回路の安定性について

ET 様

・貼付いただいたボード線図はどの電圧比を示しているのでしょうか。

→ ループゲインAβになります。

・ご教示頂いたシミュレーション回路で安定性を見れる理屈についてご教授頂けないでしょうか。

→ 若干手法は異なりますが、検証の目的はご教示頂きました資料に記載されている内容と同様です。

ループのDCに影響を与えないように容量結合(C4)で信号を入力し、Inductor(L1)で

周波数成分をカットし、ループゲインを検証した一例になります。Kato

2020年8月18日 6:38 PM #13053返信先: 差動増幅回路の安定性について

ご回答くださりありがとうございます。

追加質問させていただきます。

・貼付いただいたボード線図はどの電圧比を示しているのでしょうか。

・ご教示頂いたシミュレーション回路で安定性を見れる理屈についてご教授頂けないでしょうか。

https://kobaweb.ei.st.gunma-u.ac.jp/lecture/2016-6-21gendai.pdf P16のような資料、

あるいはご説明を頂ければ大変助かります。2020年8月18日 5:50 PM #13052返信先: 差動増幅回路の安定性について

ET 様

TINA-TIを用いてPhase Marginを確認致しましたが、残念ながら、既に位相が180°以上遅れております。

現状の回路構成ですと、出力負荷C3=0.01uFを例えば10pFに変更して頂けますと、Phase Marginが確保できるようです。

また、OPA2376の推奨動作電圧範囲は2.2V(±1.1V)~5.5V(±2.75V)になりますので、ご注意下さい。

Kato

2020年8月18日 4:33 PM #13051返信先: libmath.aについて

kenokn様

コンパイラはCCSのアップデート機能より入手いただけます。

CCSのHelpタブより、”Install New Software”をクリックください。

Work withを –All Available Sites–にし、”4.1.9″で検索をすると、

該当のコンパイラが表示されますので、こちらよりインストールください。またインストーラーについてTI社に確認しましたが、

申し訳ございませんが、MSPMATHLIBの過去のインストーラーは提供していないようでした。

よろしくお願いいたします。

2020年8月18日 3:34 PM #13050返信先: libmath.aについて

Eri様

ご回答有難うございます。MSPMATHLIBの件、承知いたしました。

もう一点、今回の質問の派生となりまして申し訳ございませんが、教えてください。>ビルドが出来ているという情報から、

> 原因はライブラリではなく、コンパイラによって起こされていると考えられますので、

>ご開発当時と同様のコンパイラ・設定をご使用されているかご確認いただけると幸いです。

特定のコンパイラをダウンロードすることは可能でしょうか。

具体的に言うと、TI v4.1.9 を入手したいのですが、TIのサイトからダウンロード可能でしょうか。 -

投稿者検索結果

フォーラム検索:page

フォーラム検索:page