-

投稿者検索結果

-

2020年6月2日 11:39 AM #10970

ishi1126 様

追加でご確認させて頂きたいのですが、Ferrite Beadsの型番をご教示頂けますと幸いです。

Kato

2020年6月2日 10:26 AM #10967ご連絡頂き有難う御座います。

> Inductor L5、L6をFerrite Beadsに変更することで、短絡試験時に/FAULTはLowに

> Assertされるとのことですが、回路図上、/SDと/FAULTが直接接続されているため、

> 自動復帰を繰り返す動作になりますが、実機でもそのような動作でしょうか?はい。/SDと/FAULTは直接接続のため、自動復帰を繰り返します。

> また、ご使用のInductorの型番よりWebでSpecを確認致しましたが、直流重畳特性のDataがなく、

> 参考値として22uHと47uHで確認しますと、直流重畳許容電流が小さいようです。

> 例えば、直流重畳許容電流が大きい別のInductorでご確認頂くことは可能でしょうか?確認致します。何か進展があればまた連絡致します。

2020年6月2日 10:21 AM #10966ishi1126 様

申し訳ございませんが、TPA3112D1EVMは保有しておらず、実機確認は行っておりません。

Inductor L5、L6をFerrite Beadsに変更することで、短絡試験時に/FAULTはLowに

Assertされるとのことですが、回路図上、/SDと/FAULTが直接接続されているため、

自動復帰を繰り返す動作になりますが、実機でもそのような動作でしょうか?また、ご使用のInductorの型番よりWebでSpecを確認致しましたが、直流重畳特性のDataがなく、

参考値として22uHと47uHで確認しますと、直流重畳許容電流が小さいようです。

例えば、直流重畳許容電流が大きい別のInductorでご確認頂くことは可能でしょうか?Kato

2020年6月2日 8:44 AM #10962ご回答ありがとうございました。

試しにKaを 0.5から0.75に変えてみました。若干FET AB間の中点波形の変化はありましたが、Rabを10kΩ等にするほど変わらず

軽負荷時効率の変化もわずかでした。軽負荷時効率の特性を現状で我慢するか、定数を全て調整しなおすかで考えます。

2020年6月1日 11:10 AM #10957ishi1126 様

追加でご確認頂きたいのですが、入力を1kHzから無信号にした際に

OUTP-OUTNをShortすると/FAULTはLowにAssertされますでしょうか?Kato

2020年5月29日 6:58 PM #10956ishi1126 様

追加の波形情報をご提供下さり、ありがとうございます。

同様にOUTPを+12.5V、及びGNDにShortした際の波形もご提供頂くことは可能でしょうか?

正常にOvercurrent Protectionが機能していると思われるので、実測による過電流の閾値を

確認したいと考えております。Kato

2020年5月29日 4:32 PM #10948> OUTP-OUTNをShortした際、入力にはAudio Sourceや1kHzなどを

> 入力して検証を実施されたのでしょうか?入力ソースはオーディオアナライザから1kHzを入力しています。

参考になるかわかりませんが、OUTP-OUTNのShort保護のためにPSW2(ポリスイッチ)を追加しており、

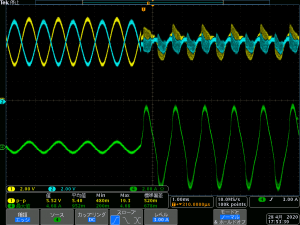

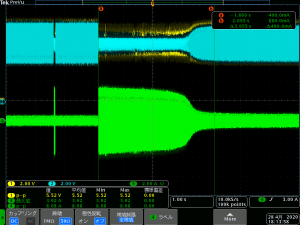

ポリスイッチの動作を確認した波形を添付致します。黄色と青色の波形がそれぞれOUTP、OUTNになります。

緑色の波形が電流波形です。OUTP-OUTNをShortした瞬間にp-pで9A程度の電流が流れます。

ポリスイッチが温まると電流は抑制されます。Attachments:

2020年5月29日 4:21 PM #10947ishi1126 様

回路図の情報をご提供下さり、ありがとうございます。

TPA3112D1は過電流を検出した際に/FAULTをLowにAssertしますので、

OUTP-OUTNをShortした際に過電流が流れるような条件に対しては

短絡保護が働きます。

OUTP-OUTNをShortした際、入力にはAudio Sourceや1kHzなどを

入力して検証を実施されたのでしょうか?Kato

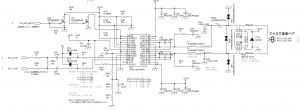

2020年5月29日 4:07 PM #10945回路図を添付致します。

Shortした箇所は「LC Filter後のSpeaker端子」になります。

回路図のRL29の3pin、6pinにあたります。オシロの波形について、申し訳御座いませんが、

現在、測定基板が手元に無いため、すぐには波形を出せないです。TPA3112D1は「(2)OUTP-OUTNのショート」のショートも保護される仕様なのでしょうか。

Attachments:

2020年5月29日 2:17 PM #10937返信先: DGKパッケージの機械的強度について

yhatagishi様

お世話になっております。

OPA2376 DKGパッケージの機械的強度について確認致しましたが、

PKGの構造や機械的強度に関する設計値については非開示な情報となるとの事でございます。

また、機械的強度に関するデータはHTSSOPに関する物であれば存在する状況となります。

そちらの情報を元にVSSOPに関して、貴社条件をお伝えした上で見解を求めたところ、

あくまで参考情報となりますが1.2MPaに耐えうるとの見解を得ました。

ただし、OPA2376は精密にトリミングされた製品となり、電気的特性が変化することが懸念され、

データシートで規定された特性を満たせない場合がございますのでご留意頂ければ幸いでございます。

念のため以下に原文を記載させて頂きます。(原文)

We have data on HTSSOP on another gullwing leaded package in SOP family, but not on 8-lead VSSOP. Based on HTSSOP data (enclosed) and scaling back to VSSOP package size, it seems the 1.2MPa is OK.数値情報を提示できず申し訳ございません。

何卒宜しくお願い致します。Undertale

2020年5月29日 1:41 PM #10935wtidesigner様

返信頂き、ありがとうございます。

ADELピンとADLEFピンがCSピンと分圧抵抗を介して接続している場合、

貴社の御認識通り、CS電圧にバイアスをかける(CS電圧を変化させる)ことで、AB間だけでなく、CD間,AF間,BE間のTime Delayの値も変化致します。また、もし他のTime Delayを変えずにTABSETだけを変化させる場合、Rab=13kΩでCS電圧(もしくはADELピンに印加する固定電圧)を設定して頂いた上で、

Rcd、Refの値を調整して、他ののTime Delayを元の値に合わせて頂く方法しかございません。以上、よろしくお願い致します。

2020年5月28日 6:31 PM #10929ishi1126 様

TPA3112D1に関してOUTP-OUTN間のShortにおいて/FAULTがLowにAssertされないとのことですが、

出力間をShortした際の入力条件とShortした箇所(出力端子 or LC Filter後のSpeaker端子)をご教示頂けますでしょうか?

また、Short時のOscilloscopeの波形を共有して頂けますと幸いです。Kato

2020年5月28日 1:34 PM #10920ご回答ありがとうございます。

ご回答いただいた回答の前者、KAの値を調整する方法は軽負荷時ですから CS=0。

よって RABできまる固定値になりますから13kΩ以下にできないのであれば、現状より TABSETは小さくすることができません。後者の固定電圧(最大2Vが推奨)を印加の方法では、出力電力増加つまりCS電圧の上昇によりAB間のTime Delyを短くすることができません。

この二つの問題を解消するためにCS電圧にバイアスをかけることを二つ目の投稿で述べたのですが、そうするとCD間,AF間,BE間のTime Delyが変わってきます。

制御特性の意味合いが異なっているようですが、各FET間のTime Delyが微妙に変わると、効率など電源特性が変わっています。このことを(電源)制御特性が変わると述べています。

例えばCS電圧にバイアスを加えると、AB間のTime Delyは短くなりますが、出力電力が増えた際のAF間Time Delyは広がってしまいます。これら全ての調整のやり直しが発生するためTABSETだけを変える方法を模索しているものです。どうも良い案はなさそうですね。

2020年5月28日 11:07 AM #10917返信先: マイコンリセット条件について

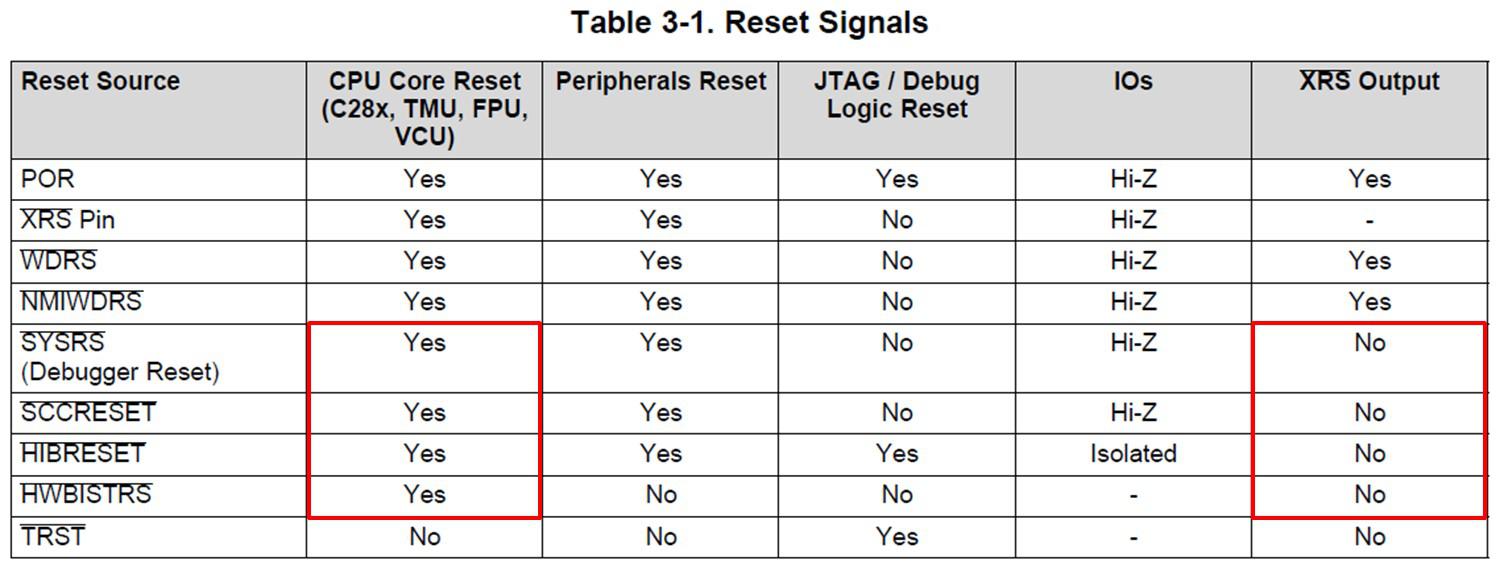

お問い合わせありがとうございます。

外部リセットが出力されず、CPUリセットがかかるものは以下の4つのReset信号となります。

TMS320F2837xS Dual-Core Delfino Microcontrollers Technical Reference Manual (Rev.G)https://www.tij.co.jp/jp/lit/ug/spruhx5g/spruhx5g.pdf

P.90 Table 3-1. Reset Signalsまた、リセットによる問題である場合には、上記マニュアルのP.356に記載されているRESCレジスタを確認することで、リセット要因を特定することができますので、調査にはこちらのレジスタもご活用いただければと思います。

以上、宜しくお願い致します。

2020年5月27日 10:57 PM #10915返信先: DGKパッケージの機械的強度について

yhatagishi様

お世話になっております。

OPA2376 DKGパッケージの機械的強度について資料有無を確認し

折り返しご連絡致します。

少々お時間を頂ければ幸いでございます。

何卒宜しくお願い致します。Undertale

-

投稿者検索結果

フォーラム検索:page

フォーラム検索:page