-

検索結果

-

トピック: リセット時間について

お世話になります。

データシートのTable 5-5に電源電圧安定からリセット解除までの時間が

tw(RSL1)として記載されているかと思います。

この間にマイコン内部の発振が安定すると考えて良いでしょうか。また、外部水晶振動子を用いる場合、

水晶振動子の安定化を考慮した上で

リセット時間を決定した方が良いのでしょうか。

指針等ございましたらご教授願います。以上よろしくお願いいたします。

トピック: AMC1301の内部抵抗について

お世話になります。

AMC1301のフロント部分の抵抗などについて質問があります。

1) DS上に”The gain of the differential amplifier is set by internal precision resistors to a factor

of 4 with a differential input impedance of 22 kΩ”と記載がありますが、ここでいうdifferential input impedanceとは何を指すのでしょうか。

R4とR5の直列合成抵抗でしょうか。2) 実態として、RINは何でしょうか。

3) R4, R5, RINの誤差、温度係数を教えていただけますか。

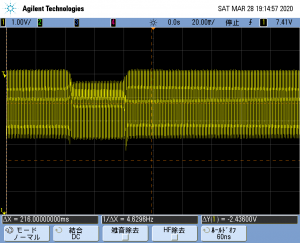

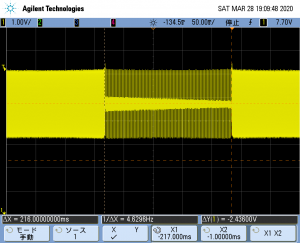

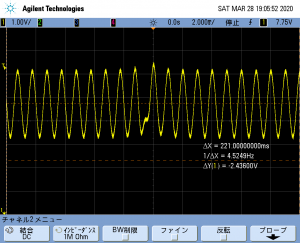

トピック: F2837xD SPI通信について

度々お世話になっております。

SPI通信についての質問です

FPGA側がマスタ、DSP側がスレーブで

DSP側が受信割込み完了後、受信データを解析し

送信処理を行うようなプログラムを製作しております初期設定にてSPICCRのSPILBKビットをゼロ(ループバック禁止)にしているにも関わらず、

受信波形をそのまま送信している現象が何回か発生しています。この現象について何か考えられる原因はございませんでしょうか?

トピック: XRSピンのH/L閾値について

お世話になります。

データシートのP.56にHigh-level input voltageが定義されておりますが、

これはmin値以上の値を印加すればHと認識すると考えて良いでしょうか。

例えばAll other pinsではmin値が2Vとなっておりますので、

2V以上を印加すればHとなるのでしょうか。また、XRSピンも同様に2Vが閾値と考えてよろしいでしょうか。

フォーラム検索:page

フォーラム検索:page