-

検索結果

-

トピック: TLV320AIC3109-Q1について

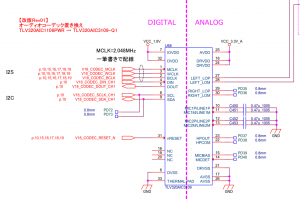

TI製TLV320AIC3109-Q1のレジスタ設定について、

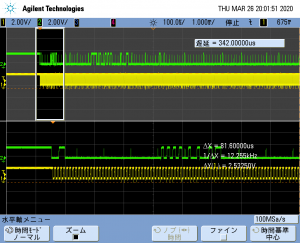

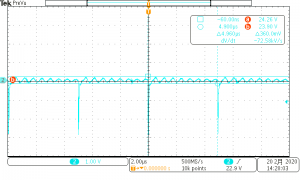

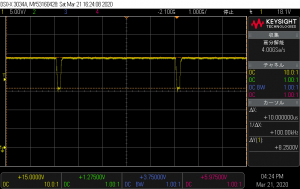

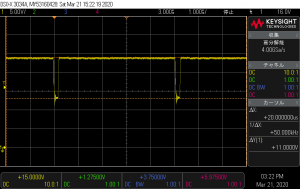

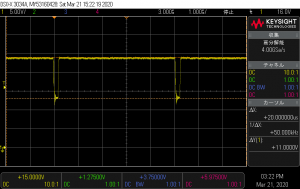

以下のように設定していますが、問題無いかご確認頂けないでしょうか。通信時の波形を添付致します。

回路図も添付致します。また、Register 0にアクセスした後にreadが推奨されていますが、

readしないで続けてアクセスすることは可能でしょうか。以下の設定としています。

・DSPモード

・Fs(ref)=48KHz

・FS=8KHz

・MCLK=2.048MHz

・TDM Offset = 1

・Right Channel = all’0′

・256クロックモード

・Left Justified【レジスタ設定 Page0のみ】

————————————————————

Register 書き込みデータ

3~0 91 AA 00 00

7~4 08 00 00 C0

11~8 01 00 40 00

15~12 00 00 00 00

19~16 84 FF FF 80

23~20 78 78 08 78

27~24 02 00 00 78

31~28 00 FE 00 C0

35~32 00 00 00 80

39~36 00 00 80 00

43~40 00 64 00 00

47~44 00 00 00 80

51~48 04 00 00 00

55~52 00 00 00 00

59~56 00 04 00 00

63~60 00 00 00 00

67~64 00 00 04 00

71~68 00 00 00 00

75~72 00 00 00 04

79~76 00 00 00 00

83~80 00 80 00 00

87~84 00 08 00 00

91~88 00 00 00 00

95~92 00 00 00 00

99~96 00 00 00 00

103~100 00 02 00 00

107~104 00 00 00 00

111~108 00 00 00 00

115~112 00 00 00 00

119~116 00 00 00 00

123~120 00 00 00 00

127~124 00 00 00 00

————————————————————トピック: CCSv6 リソースエクスプローラーが機能しない

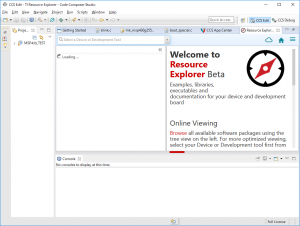

CCS v6.2 で、リソースエクスプローラーを起動すると、添付画像のように”Loading…”となったままになります。

Preference→General→Network Connections の Active Provider を”Native” にしてOK とし、

CCSを閉じて2回再起動しても治りません。

また、C:\ Users \ <Userid> \ tiにあるtirex-localserver- <version>フォルダーを削除して、

CCSを再起動でも治りません。

他に対処方法があればお教え頂けませんでしょうか?TMS320F28375Sの100pin製品で、UnbondedとなっているGPIOポートは、信号線を取り

出せないだけで、ポートとして利用することは可能でしょうか?質問の意図は以下のとおりです。

EPWM5AはGPIO8が通常の出力先となっていますが、100ピン製品では該当端子がありま

せん。

そこで、GPIO8をINPUT-XBARに取り込み、さらにOUTPUT-XBARから別なGPIOに出力する

ことを検討しています。例えば、GPIO8 -> INPUT5 -> OUTPUT2 -> GPIO59 のような流れで信号を外部に出力

する。実際に動作していることは確認済みですが、製品として許容されている使用方法であ

るか確認させてください。トピック: LM3478_COMP端子電圧について

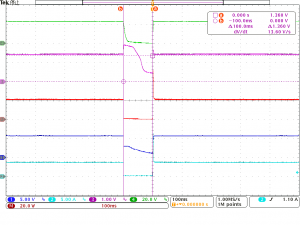

LM3478について

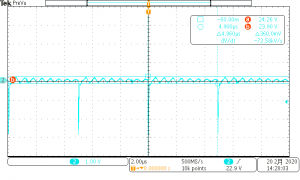

COMP端子電圧の充電について教えてください。添付波形のように、入力を遮断するとCOMP端子電圧が跳ね上がります。

この原因はなぜでしょうか?この現象は必ず起こるものなのでしょうか?

(添付波形 青色:Vin 水色:Iin 桃色:COMP端子 緑色:Vout 赤:Win )また、COMP端子の最大電圧は何V でしょうか。その影響する要因も踏まえてご教授ください。

以上、よろしくお願いします。

トピック: リセットICの閾値について

リセットIC TPS3703A4120DSERQ1について質問させていただきます。

データシートのP4には下記の記載があります。

Vmon=1.20 V

THRESHOLD TOLERANCE=4%

http://www.tij.co.jp/jp/lit/ds/jajsgg5a/jajsgg5a.pdfこれはVIT, VIT+(OV),VIT-(UV),VHYSとどのような対応になるのでしょうか。

下記対応であっていますでしょうか。

VIT=Vmon

VIT+(OV)=Vmon*(1+4%)

VIT+(OV)=Vmon*(1-4%)

VHYS=Vmon*(0.3%~0.8)EIA-422ドライバIC「DS96F174MJ/883」に「QS」のサフィックスが付いた型式があります。(DS96F174MJ/883QS)

この「QS」はどういった意味の記号でしょうか?TIのフォーラムに似たような投稿がありましたが、同じ意味でしょうか?(QはQML認証、Sはテストサイト)

該当のTIフォーラム投稿

フォーラム検索:page

フォーラム検索:page