-

投稿者検索結果

-

2020年2月27日 10:43 AM #9974

返信先: TPS40200のmax電流について

maida様

平均電流でディレーション可能です。例えば10Vin,5VoutならDutyは50%なので1回のスイッチングで流せる電流のピークは倍になります。

Gate抵抗0Ωの場合、理論上Drive電流は瞬間的には無限大となりますが、実際にはFETのGateに寄生抵抗があり、またQgが小さければ電流はその容量を満たす一瞬しか流れないため、平均電流は僅かです。

上記のGate抵抗の考え方は、・Qgが非常に大きいFETで・fswが低く・Dutyが広い(Vin-Vout間電圧差が小さい) 設計に適用されます。

つまりどのようなFETを使用し、入出力条件とスイッチング周波数により、Gate抵抗の有無は変わります。Fig31の設計について考察してみました。

Vin:8V

Vout:3.3V

Iout:2.5A -> Duty=41.25%

fsw:297.6kHz -> Tcycle=3.36usec Ton=1.39usec Toff=1.97usec

FET:FDC654P Rg=6Ω Qg=9nC(Vgs=10V)

FETのTurn-Off_Delayが20nsec(max)で、Qgに9nCの電荷を蓄えるとVgsが-10V(On)から0V(Off)になりますので、Gate_Drive回路に必要な電流供給能力Igateは

Igate=Qg/Toff=9nC/1.97usecc=4.57mA

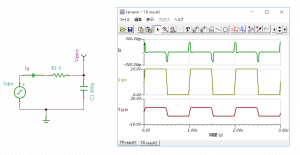

4.57mAですので、TPS40200で十分に補えるため、またFET自体に6Ω程度の抵抗があるため、外付けGate抵抗は基本的に不要と思われます。参考として900pFの容量と6Ωの抵抗で構成されたRCフィルタに、振幅10V(傾斜20nsec)1MHzの矩形波を入力した際の電流をシミュレーション致しました。添付画像を御参照ください。

電流のパルス幅は約60nsecでピークが230mAです。1MHzでも平均(引き抜き電流は除く)で11.5mAなので、周波数が1/3であれば平均電流も1/3になりますので、凡そ計算値と合致致します。御参考になれば幸で御座います。

PolnarefAttachments:

2020年2月27日 9:49 AM #9973返信先: 未使用端子処理方法について

Atlus様

本件お問い合わせ下さりありがとうございます。

お問い合わせ頂きました件について以下に回答を

ご連絡致します。————————————

端子”E/D Com”

⇒GNDにプルダウン

(回答)

ご連絡いただいた処理で問題ございません。端子”E/D(Enable/Disable)

⇒33pFのコンデンサ経由でGNDにプルダウン

(回答)

ご連絡いただいた処理で問題ございません。端子”Status Flag”

⇒GNDにプルダウン

(回答)

使用されない場合、未接続を推奨いたします。

————————————何卒宜しくお願い致します。

Undertale

2020年2月26日 10:22 PM #9971トピック: TPS40200の電源要求について

フォーラム内 電源ICTPS40200のデータシートp37の、9 Power Supply Recommendationsで

TPS40200で構成する電源回路が,入力電源より数インチ離れている場合、

入力のセラミックコンデンサとは別に、100uFの電解コンを用意することを

推奨されていりますが、

TPS40200で構成する電源回路が、電源供給用のコネクタに直結の場合

100uFの電解コンは不要でしょうか?

Figure47を確認すると、入力側に100uFではなく33uF用意されており

確認させてください。2020年2月26日 10:13 PM #9970返信先: TPS40200のmax電流について

ご回答ありがとうございました。

1点確認させてください。

データシート figure31,figure44ではDRVpinとFETのゲートは0Ωで接続しており、

データシート figure47はDRVpinとFETのゲートを直結しております。

教えて頂いた抵抗値(30~48Ω)より、ゲート抵抗が小さいようですが

データシート figure31,figure44,figure47の接続では、TPS40200のDRVpinを

駆動する回路が破損する恐れがありますでしょうか?2020年2月26日 9:59 PM #9969ご回答ありがとうございました。

こちらで設計しました、TPS40200を使用したVIN24V,VOUT12V回路で

Iout0Aのとき、コイルは電流不連続モードで動作していてGDRV端子には

最大24.3Vの電圧がかかり、VINの24Vを越える電圧が印加しております。

GDRV端子にはVinを超える電圧の印加は許容いたしかねると連絡頂きましたが

0.2~0.3V越えてもIC破損の原因になりますでしょうか?2020年2月26日 1:45 PM #9959返信先: CCS5から9への更新で

こんにちは

driverlib.libのファイル形式を TI-COFF から ELF に変更しなければならない。

ということでしょうか。

どのように対応すればよいでしょうか?

ライブラリのソースを提供していただけると、手っ取り早いのですけれど。よろしくお願いします。

2020年2月26日 1:05 PM #9958papiron様

回答が遅くなり、申し訳ございません。

MICRON製のNANDフラッシュ:MT29F1G08ABAEAについて以下回答させて頂きましたため、ご参照願います。

1.この製品の製造時におけるバットブロックは,およそ何%くらいでしょうか?

=>

本製品は、仕様上Bad Block数はおおよそ2%程度許容されております。

2.製品などに実装後,どのくらいの頻度でどの程度のバットブロックが発生しますか?

=>

温度環境やprogram方法にも依存いたしますが、

本製品のP/E cycle寿命指針に近づくと、訂正能力以上のbit errorが発生し、

出荷後発生Bad Blockになりやすくなります。

なお、本製品のP/E cycle寿命指針は100k[P/E cycle]となります。

3.バットブロックとは正常に読み書きできないブロックだと思いますが,

ハード的なメカニズムを教えてください。

=>

本NANDセル内にある酸化膜がprogram/eraseの繰り返しにより、劣化していき、

後にbit errorとして顕在化し、読み書きできない領域としてBad Blockの発生につながっております。

補足ですが、Endurance P/E cycle数を超えるとBad Blockになるわけではございません。

4.ECC機能はNANDフラッシュに実装されているものなのでしょうか?

=>

本製品に関しては、Non-ECCの製品になるため実装されているものではなく、Host側が実装するものになります。

5.ECCのやり方は,どのような方法となるのでしょうか?

=>

Hamming符号,Reed-Solomon,BCHにて実装頂けます。BCH符号方式がMicron製品の推奨実装方法になります。

詳細はテクニカルノートがございます為、営業担当までご連絡頂けますようお願い致します。

6.ECCに失敗すると,どのような方法でデータを確保するのでしょうか?

=>

基本的に実装された訂正能力以上のbit化けは回避できません。

そのため、NAND Flash単品を扱う場合Block管理等ケアし、使用する必要がございます。

例)ECC, Bad Block management, Wear leveling

注)’23年終息予定の製品になりますため、非推奨品になります。その点ご了承頂けますようお願い致します。2020年2月26日 12:51 PM #9953返信先: Flashburnについて

OM様

TMS320C6211 DSKは販売終了かつ、製品サポートが終了した製品となりましてこちらに関する情報がございません。

またFlashburnは、Software Design Solutions(SDS)社から提供されているツールとなりますので、

大変お手数でございますが、直接SDS社へお問い合わせいただけますようお願い申し上げます。以上、よろしくお願いいたします。

UNA2020年2月26日 11:35 AM #9951返信先: CCS5から9への更新で

クライフさま

返信ありがとうございます。

足りないソースファイルをまず探してみました。

それらをCCSv9のフォルダ内で探したのですが見つかりませんでした。

仕方ないので、CCSv5もインストールして、その中からソースファイルを探してコピーしました。driverlib.lib はプロジェクト内にコピーして、Linker の File Seartch Path に設定しました。

そしてビルドしてみたら以下のエラーが出ました。

何が原因かおわかりになりますか?

よろしくお願いします。“C:\\Users\\xxx\\AppData\\Local\\Temp\\{9AF1E810-B8B9-43FF-8BD2-4F5A9232C00B}”, line 27: fatal error:

object files have incompatible formats (“../driverlib.lib<uart_baudrate.o>”

= TI-COFF, “./gpio.obj” = ELF)2020年2月26日 11:02 AM #9950トピック: Flashburnについて

フォーラム内 Code Composer StudioCCSで作成したHexファイルを、XDS560 JTAG PCI EMULATION KIT 経由でTMS320C6211_DSKのFlashROMへ

ダウンロードしたいのですが、Flashburnというソフトを使用すればダウンロード可能なのでしょうか?

また、Flashburnを使用すればダウンロード可能である場合ですが、

Windows-XPで動作可能なFlashburnを入手する方法はありませんでしょうか?2020年2月26日 10:51 AM #9947ご連絡ありがとうございます。

HD8 pinの設定については、起動時にPLDからHiにしていると推測しますが、PLDからの接続を切断してHD8pinをLow固定にした場合、

XDS560との通信がNGになりました。この基板については、Little Endianでの動作を前提にしているものと理解しました.

また、エミュレータの設定に関しても特に情報なしとのことで了解しましたので、本件クローズさせて下さい。

ご対応ありがとうございました。2020年2月26日 10:43 AM #9946返信先: TPS40200軽負荷時の動作について

maida様

一般的なDC/DCにおきましてパルススキップのような「軽負荷時効率改善機能」を有するICにて、例えば定格3A出力の電源回路で、1mAの出力電流条件時にてボード線図をプロット致しますと、出力電圧が完全に静定(安定)していてもクロスオーバー周波数が高め、且つ位相余裕低めとの測定結果となってしまいます。

軽負荷(無負荷)時の安定性(位相余裕度)は、ICの制御特性よりも出力コンデンサの容量に依存致します。>> FB制御ループの安定性は確保されるのでしょうか?

上記の理由の通り、多くの電源ICでは軽負荷における「安定性の確保」はされておりません。

出力電流が過渡的に変化することが予想される場合にはCoutを大きく、Lを小さく、fswを高めに設定することをお勧め致します。Polnaref

2020年2月26日 10:26 AM #9945返信先: TPS40200のmax電流について

maida様

Gate抵抗に関しまして、具体的な抵抗値の指針は御座いませんが、電流値の目安はデータシートp5[Gate Driver]に記載の値が参考にできます。

Gate_Drive回路は125mA(min)の電流ソース能力とと200mA(min)の電流シンク能力を有しており、この電流値を上回るとGate電圧(8Vtyp)が低下、FETのスイッチング速度が致します。

Gate電圧の最小値は6Vなので、それぞれ電流値で割りますと、Gate抵抗は

6V/125mA=48Ω

6V/200mA=30Ω

となります。

実基板上では他の寄生成分/抵抗成分もありますので、付加するGate抵抗はさらに小さい値でも問題無い場合が多いです。御参考になれば幸で御座います。

Polnaref2020年2月26日 9:49 AM #9944maida様

>> 頻繁に入力の電源をOn/Offしない装置では、SSpinに1MΩを接続する必要はございませんでしょうか?

その御認識で問題御座いません。以上、宜しくお願い申しげます。

Polnaref2020年2月26日 9:24 AM #9942OM様

ご確認いただき、ありがとうございます。

TMS320C6211のデータシートを確認しますと、HD8 pinのリセット時のIO極性によって、デバイスのEndian Modeが決まるとの記述が御座います。

Little EndianでロードができることからHD8 : 1(Little Endian)でDSKが設計されているのでないかと推測いたします。参考資料:TMS320C6211, TMS320C6211B Fixed-Point Digital Signal Processors datasheet (Rev. L)

P.23 Terminal Functions (Continued)またC6211はデバイスが古くメーカサポートも終了しており、弊社でも本デバイスに関する情報がございません。

大変恐縮ではございますが、ご理解いただけますようお願いいたします。以上、よろしくお願いいたします。

クライフ -

投稿者検索結果

-

検索結果

-

トピック: TPS40200の電源要求について

TPS40200のデータシートp37の、9 Power Supply Recommendationsで

TPS40200で構成する電源回路が,入力電源より数インチ離れている場合、

入力のセラミックコンデンサとは別に、100uFの電解コンを用意することを

推奨されていりますが、

TPS40200で構成する電源回路が、電源供給用のコネクタに直結の場合

100uFの電解コンは不要でしょうか?

Figure47を確認すると、入力側に100uFではなく33uF用意されており

確認させてください。トピック: Flashburnについて

CCSで作成したHexファイルを、XDS560 JTAG PCI EMULATION KIT 経由でTMS320C6211_DSKのFlashROMへ

ダウンロードしたいのですが、Flashburnというソフトを使用すればダウンロード可能なのでしょうか?

また、Flashburnを使用すればダウンロード可能である場合ですが、

Windows-XPで動作可能なFlashburnを入手する方法はありませんでしょうか?

フォーラム検索:page

フォーラム検索:page