-

検索結果

-

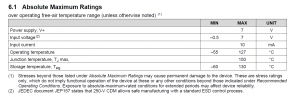

トピック: TMP275の絶対最大定格について

TMP275データシート内の絶対最大定格にInput voltage -0.5V~7V とあるが、

SCL,SDAピンにこの値を適用してもよいか教えてください。トピック: A,B同時オンの可否

お世話になります。

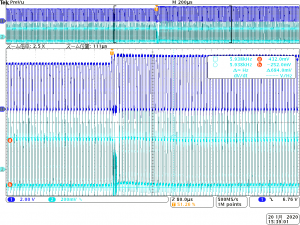

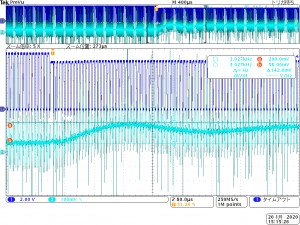

UCC21520の使用を検討しております。

動作上、A chとB chの同時オンが必要となるのですが、

典型的なハーフブリッジドライバーを用いた場合、

保護機能が働き、排他動作あるいは同時OFFとなるかと思います。

当該ドライバーでは、このような保護動作なく

A chとB chの同時オンを行うことが可能でしょうか。

よろしくお願いいたします。-

このトピックは

ETが5 年、 10 ヶ月前に変更しました。

トピック: TPS259230について

TPS259230のOV CLAMP機能について。

本機能の応答速度はどの程度になるでしょうか。

例えば、100ns間、6.1Vを越えるような、

スパイクノイズを、クランプすることは可能でしょうか。トピック: NAND Flashのbadblockについて

ある製品が起動しなくなり,メーカに確認したところ,

MICRON製のNANDフラッシュ:29F1G08ABAEAを使用しており,

NANDフラッシュにバッド・ブロックが発生し,CPUからアクセスができなくなったといわれました。

ある時期まで,正常に動作していたのですが,急にアクセスできなくなりました。質問は,

・バッド・ブロックとはどのようなものか?

・使用しているうちにバッド・ブロックが発生するものなのか?

→発生する場合,どのような要因が考えられるか?(読み込みだけで発生するのか?,書き込みをおこなうと発生?など)よろしくお願い申しあげます。

-

このトピックは

フォーラム検索:page

フォーラム検索:page