-

投稿者検索結果

-

2019年10月14日 4:22 PM #8551

返信先: F2837xD CPU間の割込み

上記サンプルとは異なりますが、

ControlSUITEのLab11_cpu01, Lab11_CPU02をContrlCARDにダウンロードし評価を行っております割込みが入るかどうかを確かめるため

IPC1_ISRの先頭にてブレイクポイントを張りましたが、

以下のエラーが発生します。Trouble Reading Register PC:

(Error -1142 @ 0x0)

Device blocked debug access because it is currently executing non-debuggable code. Choose ‘Rude Retry’ to disable polite mode and force the operation.

(Emulation package 8.0.27.9)CPU間の割込み等はLEDで確認するしかないのでしょうか?

2019年10月11日 6:27 PM #8548返信先: UCC29950の設計について

SUNCON様

ご投稿頂き、ありがとうございます。

頂いたお問い合わせに対する回答ですが、以下の内容となります。

1.GD1,GD2に関して

データシートにはトランスもしくはゲートドライバを使用して、

FETにつなげておりますが、それがないとFETは動作しないのでしょうか?【回答】

GD2はHigh-side_FETをドライブするため、耐圧的にゲートドライバが必須です。

GD1は、動作しないことは御座いませんが、内部に2桁Ωの抵抗成分が有り、

Qgが大きい大電力用のFETを使用する場合には、ゲートに流入する電流が増え、

抵抗によりゲート電圧が低下する為、FETのON抵抗が増大する恐れが御座います。

FETのON抵抗は電源回路の効率と発熱に大きく影響します。

FETの高速ON/OFFと回路の低損失化にはゲートドライバを御使用頂くのが効果的です。②AC1,AC2には9.3MΩを、PFC段の電圧調整用の抵抗には30MΩと73.33kΩを

使用しなければならないと書いていますが

抵抗が少ないとどういう影響があるでしょうか?【回答】

ACx端子には60kΩの抵抗が内蔵されており、ACラインの周期的な電圧変化を内蔵抵抗により電流に変換し、

その電流値を読み取ります。

電流値のレンジは7uA~40uA程度です。

ACxに流入する電流が増えますとこの範囲から外れますので、正確なAC電圧検出が出来なくなる可能性が御座います。

そのため、AC1、AC2に接続する抵抗はデータシートの記載通りの9.3MΩのものをご使用頂ければと存じます。

また、PFC段の電圧調整用の抵抗(RTOP、RBOT)ですが、RTOPとRBOTの抵抗比率(30MΩ/ 73.33kΩ= 409.28)を大きく外れない限り、

抵抗値を小さくしていただくことは可能ですが、おっしゃる通り待機電力は大きくなります。以上、よろしくお願い致します。

2019年10月11日 5:11 PM #8547>別の書き込みケーブルというのは、

>「MSP-FET」等のJTAG4線式対応のツールという認識であっていますでしょうか。

★合っています。

>上記の場合、

>お手数ですが、以下の項目をお試しいただけますでしょうか。

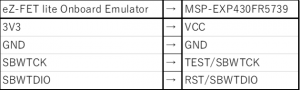

>①MSP-EXP430F5529のeZ-FET lite Onboard Emulatorを使用し、

>MSP-EXP430F5529のMSP430F5529を、Spy Bi-wire経由で書き込めるかどうか。

★書き込めます。

>②別の書き込みケーブルを使用し、

>別ボードに実装されたMSP430FR5739IRHARを、Spy Bi-wire経由で書き込めるかどうか。

★試してみます。2019年10月11日 5:05 PM #8546aikawa様

ご回答いただきありがとうございます。

別の書き込みケーブルというのは、

「MSP-FET」等のJTAG4線式対応のツールという認識であっていますでしょうか。上記の場合、

お手数ですが、以下の項目をお試しいただけますでしょうか。①MSP-EXP430F5529のeZ-FET lite Onboard Emulatorを使用し、

MSP-EXP430F5529のMSP430F5529を、Spy Bi-wire経由で書き込めるかどうか。②別の書き込みケーブルを使用し、

別ボードに実装されたMSP430FR5739IRHARを、Spy Bi-wire経由で書き込めるかどうか。以上、よろしくお願い致します。

2019年10月11日 3:08 PM #8545Akinobu様

ご投稿ありがとうございます。以下回答致します。

1.LPFの適切なカットオフ周波数について

LPFのカットオフ周波数=960Hzでよろしいでしょうか?【回答】

カットオフ周波数は960Hzとはなりません。

ΔΣADCのサンプリング周波数は、Modulator FrequencyとDecimation filterの

関係によって決定します。

英文データシートP18のDigital Filter章をご参照ください。

(日本語データシートP16)2.LPF(RC回路)の適切な時定数について

※ADS1256のデーターシートの表13を見ますと、Date_rate[sps]=10

にしたときのセトリング時間[ms]=100.18で良いでしょうか?【回答】

表13は、IC内部のDecimation filterのセトリングタイムです。下記、計算であっていますでしょうか?

Rin×Cin<(セトリング時間/必要な時定数の倍数)

Rin×Cin<(100.18[ms]/15.25)

Rin×Cin<6.57[ms]

よって、RC回路の時定数は6.57[ms]以下が良い【回答】

申し訳ございませんが、添付頂きました資料に関してのお問い合わせに

つきましては、資料発行元へお問い合わせ頂けますようお願いします。

外部のフィルターに関して、TI社から設計ツールを提供しておりますので

ご利用ください。

http://www.tij.co.jp/ja-jp/design-resources/design-tools-simulation/filter-designer.html以上、宜しくお願い致します。

KJ2019年10月11日 1:56 PM #8544言葉足らずで申し訳ありません。

MSP-EXP430F5529のeZ-FET emulatorを使用し、別ボードに実装されたMSP430FR5739IRHARをSpy Bi-wire経由でに書き込みをして、

失敗しております。別の書き込みケーブルを使用し、JTAG4線式では書き込みできております。

2019年10月11日 1:43 PM #8542aikawa様

大変失礼いたしました。一部説明が不足しておりました。

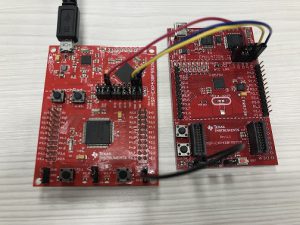

弊社で所有している評価ボード「MSP-EXP430FR5739」に搭載された「MSP430FR5739」に対して、

「MSP-EXP430F5529LP」に搭載されている「eZ-FET lite Onboard Emulator」を使用し、

同様にJTAG の2線式を使用して、CCSからプログラムを書き込めることが確認出来ました。

※写真を添付致しますので、ご参考いただければと思います。>弊社では、MSP-EXP430F5529を使用し、Spy Bi-wire経由でMSP430FR5739IRHARに書き込みをし、

>デバイス認識ができませんでした。MSP430FR5739IRHARが搭載されているボードは、御社のカスタムボードでしょうか。

お手数ですが、上記についてご教示いただけますと幸いです。以上、よろしくお願い致します。

Attachments:

2019年10月11日 11:56 AM #8541返信先: Inhibitピンについて

VAB様

お問い合わせありがとうございます。

仮に電源入力ピン(Vi)が正常かつ,InhibitにもViを入力した場合、PTH04070WAHは動作すると予想されます。

しかしながら、InhibitはIC内部でInput voltage(Vi)にプルアップされている為、オープンでも動作する仕様となっており、

open-collector or open-drainでの制御が推奨されておりますので、データシートP12 Figure11のようなMOSFETの接続構成を推奨させて頂きます。

<データシートP3 (3)コメント抜粋>

This control pin has an internal pullup to the input voltage VI. If it is left open circuit, the module operates when input power is applied. A

small low-leakage (<100 nA) MOSFET is recommended for control. Do not tie the inhibit pin to VI or to another module’s inhibit pin. See

the application section for further guidance.

<データシートP12 Output On/Off Inhibitコメント抜粋>

Figure 11 shows the typical application of the inhibit function. Note the discrete transistor (Q1). The Inhibit control

has its own internal pullup to VI potential. An open-collector or open-drain device is recommended to control this input.

何卒よろしくお願いします。

GC

cloudwork様

ご投稿いただきありがとうございます。

MSP430F6436に内蔵されているチャージポンプを使用している場合、

「LCDCPEN」レジスタと「VLCDx」レジスタを操作していただくことで、

VLCD(=供給電圧)を特定の電圧値に設定することが可能です。レジスタの設定値は、データシートの

「5.36 LCD_B, Electrical Characteristics」をご参考いただければと思います。

MSP430F643x ミクスト・シグナル・マイクロコントローラ datasheet (Rev. E)また、VLCDの推奨値についてですが、

ユーザーズ・ガイドの「34.2.5.3 LCD Contrast Control」に、

推奨値を算出する式が記載されております。

※VLCD = Vth,10%/(VRMS,OFF/VLCD)Vth,10%は、LCDディスプレイに依存する値ですので、

LCDディスプレイのデータシート等と合わせて、ご参考いただければと思います。

MSP430x5xx and MSP430x6xx Family User’s Guide (Rev. Q)以上、よろしくお願い致します。

2019年10月11日 9:48 AM #8535ご確認ありがとうございます。

弊社では、MSP-EXP430F5529を使用し、Spy Bi-wire経由でMSP430FR5739IRHARに書き込みをし、

デバイス認識ができませんでした。slau647mの表を見ると、MSP-EXP430F5529は、”Supports all programmable MSP430 and

CC430 devices”の項目にチェックが入っていない為、書き込みできない認識でおります。お試し頂いたMSP-EXP430FR5739は、”Supports FR57xx, F5638, F6638”の項目にチェックが入っている為、

書き込みできる認識です。2019年10月11日 9:40 AM #8533aikawa様

>JTAG の2線式を使用して、MSP430FR5739IRHARに書き込みを試みました。

ご回答いただきありがとうございます。

弊社で所有している評価ボード「MSP-EXP430FR5739」で、

同様にJTAG の2線式を使用して、CCSからプログラムを書き込めることが確認出来ました。

接続方法を「Spy Bi-wire.png」に記載いたしますので、ご参考いただければと思います。>eZ-FET Lite EmulatorにMCUが実装されておりますが、

>Updateしないと本事象が起きる可能性はありますでしょうか?firmwareをUpdateをした場合、改善される可能性も考えられますので、

eZ-FET Lite EmulatorとCCSと接続した際に、

Updateを推奨される画面が表示された場合、Updateしていただければと思います。以上、よろしくお願い致します。

Attachments:

2019年10月10日 4:35 PM #8527度々、申し訳ありません。

eZ-FET Lite EmulatorにMCUが実装されておりますが、

Updateしないと本事象が起きる可能性はありますでしょうか?2019年10月10日 4:32 PM #8526JTAG の2線式を使用して、MSP430FR5739IRHARに書き込みを試みました。

2019年10月10日 4:16 PM #8525aikawa様

>実際、eZ-FET lite Onboard Emulatorを使用し、JTAG経由で書き込みを使用とした際、

>デバイスの認識ができませんでした。上記についてですが、F5529以外のデバイスに書き込みを行っていますでしょうか。

その場合、お手数ですが型番をご教示いただけますでしょうか。ご参考までに、eZ-FET lite Onboard Emulatorを使用し、

JTAG経由で「MSP430G2553」に書き込むことを確認致しました。>また、slau533 12ページの内容を見ると、”backchannel” UART-over-USB に関してのみの記載と

>認識致しましたが、上記、回答の通りでしょうか?上記に関しましては、再度調査致します。

以上、よろしく願い致します。

2019年10月10日 3:46 PM #8523dededengen様

回路図の添付ありがとうございます。

TI社に確認したところ、スタートアップ時はソフトスタート機能によりDutyを徐々に開くようです。

データシートのp.18 7.3.4 Soft Start and Enable (SS/EN)にある通り、コンデンサを介して0.55Vになるまでソフトスタート機能が有効となります。

そのため、スタートアップ時はDutyが最大になることは無いと考えます。

恐れ入りますが、SSpinの電圧を頂き電圧の推移をご確認頂けますでしょうか。

また、他の要因として2次側のフォトカプラ後段の基準電圧ICが上手く動作していない可能性がございます。

その場合はアノード/カソード間に22uF程度のコンデンサを挿入頂き波形をご確認頂けますでしょうか。

以上です。

-

この返信は6 年、 2 ヶ月前に

LuckyRiver さんが編集しました。

-

投稿者検索結果

フォーラム検索:page

フォーラム検索:page