-

検索結果

-

トピック: ADS1254:CH+<CH-電圧入力時について

トピック: 入力電圧範囲の確認

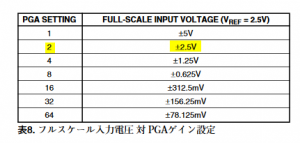

データーシートの表8を見ますと、REF電源=+2.5VでPGA GAin=2にした場合。

入力電圧=±2.5V入れられる用に記載がありますがシングル入力で±2.5V入力可能なのでしょうか?トピック: 電圧レベルシフト SN74LV1T34について

データシートを拝見すると、

電気定格の箇所で、推奨仕様動作条件の箇所で、

VI=0V~5.5V

となっておりますが、

これは

VCC端子に電源電圧を供給しない時も、

入力端子に5.5Vまで印加しても良いということでしょうか。

それとも、

VCC端子に電圧を印加する前には入力ポートには電圧を印加してはいけないのでしょうか。

以上、御多用中とは存じますが、御回答頂けないでしょうか。トピック: ADS1256について

担当者様に直接、問合せをしていまおりFAEに展開されているかと思いますが再度、投稿しました。

ADS1256について下記①~③について確認させて下さい。

①温度ドリフトについて

温度ドリフトをデーターシートで確認したい場合、関係してる箇所は

オフセットドリフトとゲインドリフトでよろしいでしょうか?②安定度について

安定度も同様、データシート上で確認したいのですが、

そういった場合、データーシートの12頁目の表1、表4が

関係してると考えでよろしいでしょうか?

また、3頁目の電気的特性で関係してる箇所はないでしょうか?③デジタルフィルタ

ADCProでADS1256EVMを動かした場合、デジタルフィルタはどうなってるのでしょうか?トピック: LMK04803の仕様確認3

お世話になります。データシート(SNAS489K –MARCH 2011–REVISED DECEMBER 2014) の記載に関して ご教⽰ください。

P65 8.6.3.2.2 CLKoutX_Y_ADLY

These registers control the analog delay of the clock group CLKoutX_Y. Adding analog delay to the output will

increase the noise floor of the output.

上記に noise floor が増加すると記載があります。相対値で構いませんので情報を頂けますでしょうか。

PLL2の fvcoを使い遅延させる事から PLL2の特性に関係するのではと予想しております。トピック: NAND ブート(ARM Master)について

66K2H12のNANDブートについて質問がございます。

ONFI対応のNAND FLASH(MT29F4G08)にU-BOOTを書き込み、

NAND ブート(ARM Master)を行いましたが、U-BOOTが立ち上がりませんでした。

MT29F4G08は8bit幅のNAND Flashです。そこで質問があります。

Boot Configuration Pins以外に必要な設定がありますでしょうか?

また他に考えられそうな原因がありますでしょうか?【 確認したこと 】

・U-BOOTをNAND Flashに書き込む際、VerifyはOKとなっています。

・DEVSTATレジスタのBOOTMODEを確認すると、

Boot Configuration Pinsの設定が正しく反映できています。

・NAND Boot Parameter Tableを確認すると、

GeometryをDeviceに問い合わせる設定となっています。

・RESET_STATレジスタのGR(Global Reset)を確認すると、発生(1)になっていますが

BOOTCOMPLETEレジスタは0のままでBootが完了できていません。

※ RESET_STATはClearできるのでリセットは解除できています。

・また、U-BOOTが展開されるはずの0x0C00 1000の内容を確認すると、

U-BOOTが展開できていません。

フォーラム検索:page

フォーラム検索:page