-

検索結果

-

トピック: 外部入力信号がピン端でなまる理由について

いつも大変お世話になっております。

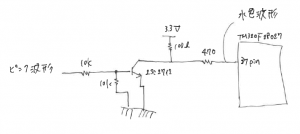

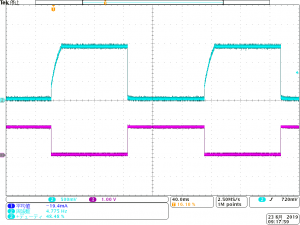

早速ですが、37pinへの外部入力信号が添付のようにピン端でなまってしまいます。

お手数ですが、原因についてご教示願います。なお、回路図は添付の通りであり、

37pinの設定は以下の通りとしております。GpioCtrlRegs.GPBMUX1.bit.GPIO37=0;

GpioCtrlRegs.GPBDIR.bit.GPIO37=0;お忙しい中、大変恐縮ですが、宜しくお願い致します。

トピック: DP83816の動作について

PCIインタフェースにDP83816を使用しておりますが,下記のような事象が発生しております。

そこで同様の事象や発生する条件,通信対象との相性の影響があればご教示いただきたく

よろしくお願い致します。

(通信対象により事象の発生頻度が大きく異なっております。)【事象】

DP83816を使用したイーサネットパケットの受信で,実際に受信したパケット長が64Byteであるにも関わらず

デスプリクタで通知されたパケット長が1536Byteであり受信したパケットサイズになっていない。必要に応じて周辺回路や使用部品の情報提供可能ですので必要あればご連絡をお願い致します。

トピック: IQ型のデジタル演算式について

いつも大変お世話になっております。

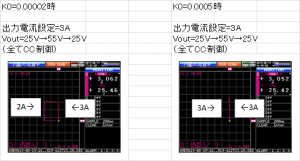

早速ですが、現在、添付のような不具合が起こっております。

なお、添付の通り、K0の値を大きくすると本不具合の程度が収まります。

また、<< 14によりMSBが0になっているのではと考え、*16384に変えてみましたが、

効果はございませんでした。ソースコード上でこのような不具合が起こりうりますでしょうか。

_iq IoutCommand_Ch1; //grobal 宣言

_iq IoutDetect_Ch1; //grobal 宣言

_iq Ierror1_Ch1; //grobal 宣言

_iq Ierror0_Ch1; //grobal 宣言

iq K0; //grobal 宣言

iq K2; //grobal 宣言IoutCommand_Ch1=3070; //別関数で代入

K0= _IQ(0.00002); //別関数で代入

K2= _IQ(1); //別関数で代入interrupt void ADCINT1_ISR(void){

_iq NxtCntVal_Ch1;IoutDetect_Ch1=AdcResult.ADCRESULT2;

Ierror0_Ch1= (IoutCommand_Ch1 – IoutDetect_Ch1) << 14;

NxtCntVal_Ch1 = __IQmpy(K0,Ierror0_Ch1,16)+__IQmpy(K2,CtrlVal1_Ch1,16);

EPwm3Regs.CMPA.all=__IQsat(NxtCntVal_Ch1, MAX_CNTVAL, MIN_CNTVAL);

CtrlVal1_Ch1=EPwm3Regs.CMPA.all;

Ierror1_Ch1=Ierror0_Ch1;

}以上、宜しくお願い致します。

フォーラム検索:page

フォーラム検索:page