-

検索結果

-

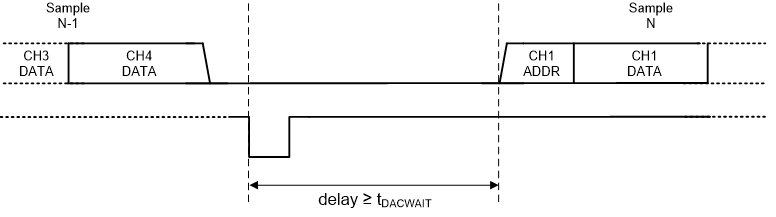

トピック: DAC update wait timeについて

DAC81408のデータシートにされております

Sequential DAC update wait timeと、Broadcast DAC update wait timeは、

何の時間か教えて下さい。

Data Registerにデータを設定してから、次にData Registerにデータを設定するまでの

必要なwait時間でしょうか?BQ24770のIBATピン(バッテリ電流モニタ)の充電電流のモニタリングができません。

放電電流はモニタリング可能です。

充電時のIBATピンの出力はほぼ0mV(5mV~10mV)となります。

IBATピンの接続先は直接テスター(電圧計)となります。

0.8A充電で評価しております。データシートにて

V(IBAT) = 20 × (V(SRP) – V(SRN)) for charge current,

との記載があり、充電電流のモニタリングも可能と読み取れます。周辺部品の定数は下記となります。

電流検出抵抗(データシートP36:RSR):10mΩ

C8,C9,C10:0.1uF

R11:30kΩ

R11と並列にコンデンサ:100pFIBATと関係のあるレジスタ設定は下記となります。

ADD:0x12H Charge Option 0

Bit[12] = 0b IDPM AUTO DISABLE

Bit[1] = 1b IDPM EnableADD:0x3BH Charge Option 1

Bit[11] = 1b IBAT EnableADD:0x38H Charge Option 2

Bit[6] = 1b IBAT OUTPUT SELECTADD:0x15H Max Charge Voltage Register

0x2EE0HADD:0x14H Charge Current Register

0x0400H上記以外で必要な設計や設定、モニタリングできない理由等ございますでしょうか。

お手数をお掛けしますがご対応よろしくお願い致します。

トピック: DACを外部リファレンスで使う

お世話になっています。

DAC80508はデフォルトでは内部リファレンスになっているようです。

外部リファレンスを使いたいのですが、どのように設定すれば良いでしょうか?33ページの Config Register の Bit8 を 1 にすれば良いと考えました。

これで良いでしょうか?

電源を起動してから、ここのビットに1 を書き込むまでの間、内部リファレンスと外部リファレンスは衝突しないのでしょうか?

ご確認お願いします。

フォーラム検索:page

フォーラム検索:page