-

検索結果

-

トピック: TLV320AIC3109-Q1について

TI製TLV320AIC3109-Q1のレジスタ設定について、

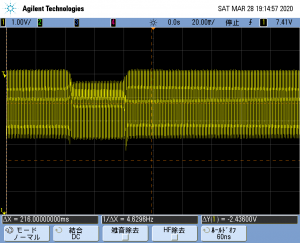

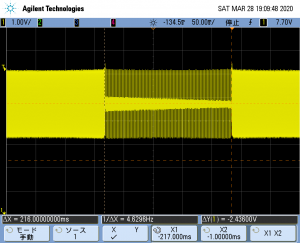

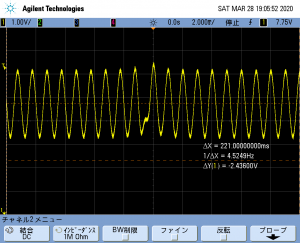

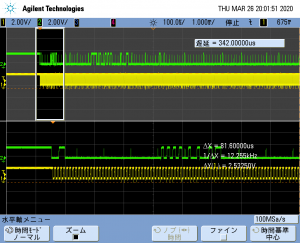

以下のように設定していますが、問題無いかご確認頂けないでしょうか。通信時の波形を添付致します。

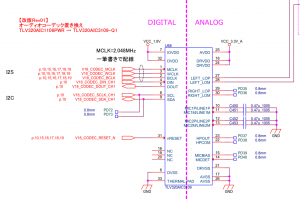

回路図も添付致します。また、Register 0にアクセスした後にreadが推奨されていますが、

readしないで続けてアクセスすることは可能でしょうか。以下の設定としています。

・DSPモード

・Fs(ref)=48KHz

・FS=8KHz

・MCLK=2.048MHz

・TDM Offset = 1

・Right Channel = all’0′

・256クロックモード

・Left Justified【レジスタ設定 Page0のみ】

————————————————————

Register 書き込みデータ

3~0 91 AA 00 00

7~4 08 00 00 C0

11~8 01 00 40 00

15~12 00 00 00 00

19~16 84 FF FF 80

23~20 78 78 08 78

27~24 02 00 00 78

31~28 00 FE 00 C0

35~32 00 00 00 80

39~36 00 00 80 00

43~40 00 64 00 00

47~44 00 00 00 80

51~48 04 00 00 00

55~52 00 00 00 00

59~56 00 04 00 00

63~60 00 00 00 00

67~64 00 00 04 00

71~68 00 00 00 00

75~72 00 00 00 04

79~76 00 00 00 00

83~80 00 80 00 00

87~84 00 08 00 00

91~88 00 00 00 00

95~92 00 00 00 00

99~96 00 00 00 00

103~100 00 02 00 00

107~104 00 00 00 00

111~108 00 00 00 00

115~112 00 00 00 00

119~116 00 00 00 00

123~120 00 00 00 00

127~124 00 00 00 00

————————————————————トピック: CDCI6214の仕様確認

お世話になります。データシート(SNAS734C –JULY 2017–REVISED NOVEMBER 2018)の記載に関して 質問させてください。

P84 8.6.1.53 CHX_CTRL2 Register (Address = 3Dh)の Bit=4 をそれぞれ “0h =IOD1” と “1h =direct” にした場合の接続 (Figure 17の様なブロック図)を ご教示ください。”0h =IOD1″ の場合は 8.6.1.29 CH1_CTRL2 Register (Address = 25h) の Bit15-14 で選択した “IOD への入力clock” になると推測していますが 正しいでしょうか。-

このトピックは

astro383が5 年、 7 ヶ月前に変更しました。

-

このトピックは

フォーラム検索:page

フォーラム検索:page