フォーラムへの返信

-

投稿者投稿

-

aikawa様

USに確認を行いましたのでそのご連絡になります。

LMR23630-Q1の(17)式については記載ミスと確認ができました。

データシートの更新を進めると報告がありました。そのため、現時点では(17)式についてはLMR23630のデータシートをご参考頂くようにお願い致します。

大変お手数をお掛けして申し訳ございませんでした。以上、よろしくお願い致します。

4ug

maida様

先日ご回答致しました内容の追記になります。

オーバーレンジに適したVOPSを15Vで設定頂ければ

問題ないかと思われます。以上、よろしくお願い致します。

4ug

aikawa様

ご連絡ありがとうございます。

大変申し訳ございませんでした。

LMR23630-Q1に記載の式が間違っている可能性がございます。

LMR23630のデータシート(http://www.tij.co.jp/jp/lit/ds/symlink/lmr23630.pdf)の

(17)式をご参考頂ければと思います。LMR23630-Q1の(17)式については、USに確認を行っておりますので

そちらをお待ち下さい。以上、よろしくお願い致します。

4ug

astro383様

ご投稿ありがとうございます。

ご質問頂いた内容に回答致します。ご確認下さい。【ご質問】

4pin(Y端子)における 出力インピーダンスを教えてください【回答】

電源電圧に依存致しますが、

VCC = 2.3 Vの場合、ワーストケースの出力インピーダンスは

VOL / IOL = 0.6 V / 9 mA = 66.7Ωとなります。以上、よろしくお願い致します。

4ug

aikawa様

ご投稿ありがとうございます。

ご質問頂いた内容に回答致します。ご確認下さい。【ご質問】

IOH, IOLの値はどのような値を使用すればよいのでしょうか?

【回答】

想定される負荷電流の最大電流(IOH)と最小電流(IOL)の値をご使用下さい。以上、よろしくお願い致します。

4ug

maida様

ご投稿ありがとうございます。

ご連絡が遅くなり大変申し訳ございません。

ご質問頂いた内容に回答致します。ご確認下さい。DAC8771のover-rangeとは、

Output Currentが0 mA – 20 mA; 4 mA – 20 mA; ±24 mA

Output Voltageが0 V – 6 V; 0 V – 12 V; ±6 V; ±12 Vのレンジで

Configuration DAC Register (address = 0x04) [reset = 0x0000]の

bit[3:0]のRENGE[3:0]で設定できますでしょうか?

【回答】

はい、Output Current / Output Valtageは、0x04のbit[3:0]で設定することができます。また、Buck-Boost Converterをenableに設定し、

over-rangeで出力することは、可能でしょうか?

【回答】

はい、Buck-Boost電圧がover-range電圧以上であれば出力することは可能かと思われます。

どの電圧設定以上が適切であるかUSに確認を行っておりますのでお待ち下さい。以上、よろしくお願い致します。

4ug

aikawa様

ご投稿ありがとうございます。

ご質問頂いた内容に回答致しますのでご確認下さい。【質問】

SN65HVD7xを使用する際の終端抵抗について、教えて下さい。

差動信号の間に入れる、終端抵抗 RTの耐電力は、どのように考えて選定すればよろしいでしょうか?

以上、ご回答の程よろしくお願い致します。【回答】

終端抵抗に流れる電流は、差動入力電圧(-12V to 12V)とその終端抵抗値、

また、差動出力電圧(-7V to 12V)とその終端抵抗値により決まります。

そこから抵抗と電圧で電流を導き、必要に応じた耐電力の抵抗を選定下さい。以上、よろしくお願い致します。

4ug

astro383様

ご投稿ありがとうございます。

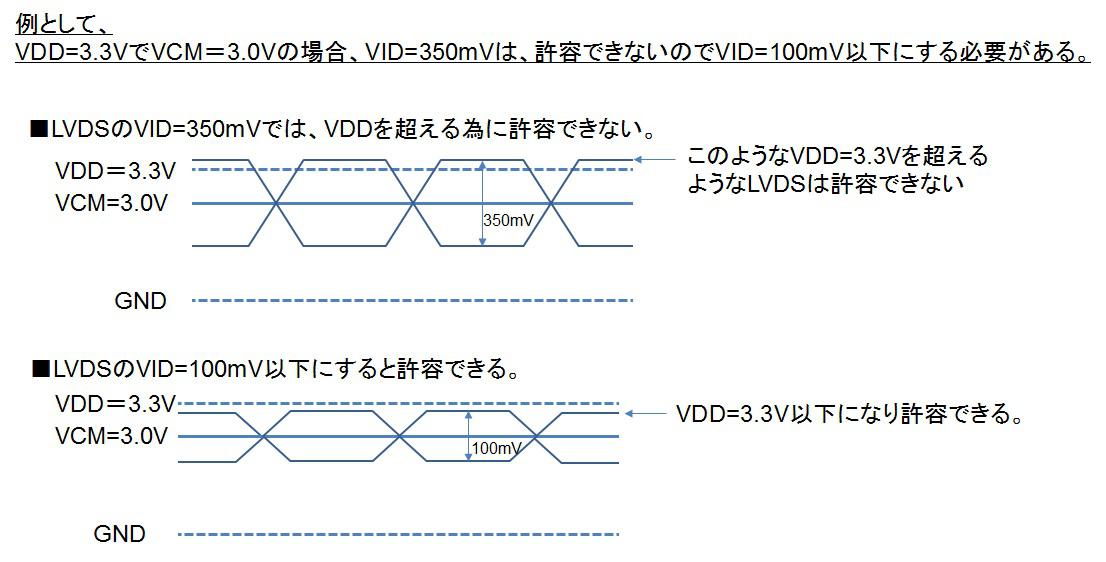

ご質問頂いた内容に回答致しますのでご確認下さい。P4 Electrical Characteristics (continued) にあります注記(3)より判断すると 一般的なLVDS信号(VCM=1.25, VID=350~400mV)を

入力する事はできない という認識で正しかったでしょうか。

【回答】

こちらの注釈の意味は、VCMが下限や上限になった場合に、VDDを超えるまたはGNDを下回るVIDのLVDS入力はできず、

その場合にVIDは100mV以下にする必要があり、100mVを超える電圧を許容しないという意味になります。下記参考図になりますので合わせてご確認下さい。

また本デバイスが理想とするLVDS信号入力の VCMおよびVIDの例を ご教示いただけませんでしょうか。

【回答】

先のご質問ありました”一般的なLVDS信号(VCM=1.25, VID=350~400mV)”で問題ございません。

また、VTH/VTLを満たすLVDS入力であれば問題ございません。以上、よろしくお願い致します。

4ug

astro383様

ご投稿ありがとうございます。

ご連絡が遅くなりまして申し訳ございません。

ご質問頂いた内容ですが、現在USへ確認を行っておりますので

回答までもう少々待ち下さい。以上、よろしくお願い致します。

4ug

Osugi様

ご連絡が遅くなり申し訳ございません。

ご投稿ありがとござます。

ご質問頂いた内容に回答致しますのでご確認をお願い致します。①ICの12pin(A),13pin(B)に正極性印加時(定格+12Vに対し+16V印加)の故障モードを

教えて頂けないでしょうか。(IC内部に電流経路はできていない)

[回答]

→I/O端子には電源GND間に保護ダイオードが内蔵されているかと思います。

その保護ダイオードの定格を超えた場合に端子が故障します。

定格を超えた電圧が印加された場合、電流経路により故障が異なりますが、

GNDショート、電源ショート、端子のOpen状態の3つが考えられます。定格+12Vに対して、+16V印可時故障した場合、通信不能となるような故障モードに移行する事はありますでしょうか。

(電圧が低くなるだけで、通常の通信は可能?など)

実機では電圧は低くなりますが、通常の通信はできています。

[回答]

→電圧が低くなっているという状況だけで推察するとGNDショートしているように思われます。

定格以上の電圧が印加されたことで保護ダイオードが完全には破壊されずソフトショートの状態となっている為に

正常動作より電圧が低く出力されているかと思われます。②の質問に対しても①と同様の回答となります。

以上、よろしくお願い致します。

4ug

HIGA様

ご連絡が遅くなり大変申し訳ございません。

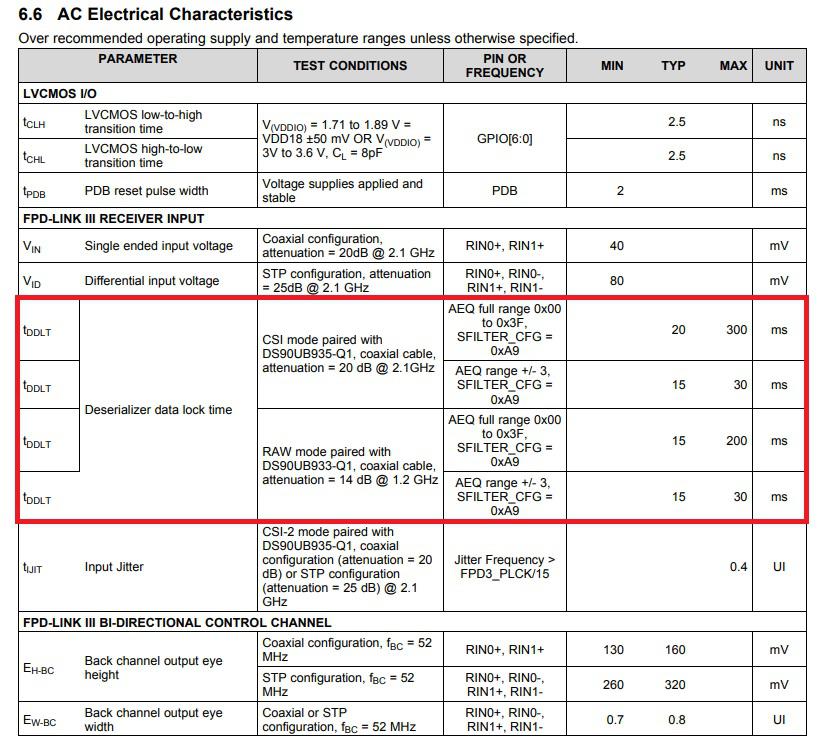

ご連絡ありがとうございます。Datasheet記載のtDDLTは、PLLのLock timeになります。

FPD-Linkのリンクが確立後は、HighになっておりますのでON/OFFは行わないかと思います。

そのため、LOCK信号がHighになったあとでリモートIOやリモートI2Cの初期設定は

可能かと思われます。以上、よろしくお願い致します。

F.T.様

ご連絡が遅れまして申し訳ございません。

質問2.についてですが、USに確認を行ったところ

タイミングチャートはないという回答でした。

大変申し訳ございません。

関連資料の紹介がございましたのでご連絡させて頂きます。

下記URLをご確認頂ければと思います。

http://www.ti.com/lit/an/slla056/slla056.pdf以上、よろしくお願い致します。

4ug

sefuku様

ご投稿ありがとうございます。

ご質問頂いた内容に回答致します。REF5010Aですが、2段重ねて使用することはできません。

2段で使用することで製品仕様スペックを満たさなくなる可能性がございます。

ご希望に沿える回答とならず大変申し訳ございませんが、ご確認をお願い致します。以上、よろしくお願い致します。

4ug

F.T.様

ご投稿ありがとうございます。

頂いたご質問に回答致しますので

ご確認下さい。質問1.

ESD保護回路ですが、ご質問で頂いた内容のご認識で合っております。

また、絶対最大定格もご認識通り、-0.5V to VDD + 0.5Vとなります。質問2.

こちらについてですが、只今USへ問い合わせを行っております。少々お待ち下さい。

回答内容によりご希望に沿えない場合もございますので、

その際はご理解頂ければと思います。以上、よろしくお願い致します。

4ug

HIGA様

ご投稿ありがとうございます。

頂いたご質問に回答致しますので

内容をご確認下さい。Lock Timeですが、

Datasheetのp.13 6.6 AC Electrical Characteristicsの

tDDLTとして記載しておりますのでそれぞれのモードに対して

Lock Timeをご確認頂ければと思います。

以上、よろしくお願い致します。

4ug

-

投稿者投稿