フォーラムへの返信

-

投稿者投稿

-

本投稿はFAQになりますので、クローズ致します。

フォーラムにお問い合わせ頂き、誠にありがとうございます。

お問い合わせ内容につきましてはメールにてご対応させて頂きます。

Kato

フォーラムにお問い合わせ頂き、誠にありがとうございます。

お問い合わせ内容につきましてはメールにてご対応させて頂きます。

Kato

本お問い合わせにつきましてはテスト投稿と思われますので、解決済みとさせて頂きます。

問い合わせ頂きましてありがとう御座います。

配線長だけでなく、配線の太さ、屈曲やビア、並走する配線の有無、レジストの誘電率など、様々な要因が配線上の寄生成分に関わってくるため、一概に回答することはできません。

下記の弊社のコラムが参考になるかと思います。

https://www.macnica.co.jp/business/semiconductor/articles/basic/120269/

https://www.macnica.co.jp/business/semiconductor/articles/basic/110489/

https://www.macnica.co.jp/business/semiconductor/articles/basic/110557/

https://www.macnica.co.jp/business/semiconductor/articles/basic/112905/御参考になれば幸で御座います。

TLV320AIC3120EVM-Uを使用されていると思いますが、PC上でUSB-AudioEVMとして認識されていれば、録音・再生が可能デバイスと考えます。

大前提としてCodecControlをサポートしているWindows OSはACEV-1A EVM User’s Guideに記載されている通り、XP、Vista、及び7になります。

念のため、ご使用のWindows OSをご確認頂けますと幸いです。

また、CodecControlを起動し、[View]⇒[Init Script…]を選択しますと、[AIC3120_USB_Init.txt]が表示されます。

Data Sheet p.42の7.3.11 Example Register Setup to Record Analog Data Through ADC to Digital Outに記載されているScriptをCopy & Pasteし、実行(Execute)して頂けますでしょうか?

その後に録音が可能なPCアプリを起動し、録音が可能かどうかをご確認下さい。

また、再生につきましてはData Sheet p.62の7.3.12.15 Example Register Setup to Play Digital Data Through DAC and Headphone/Speaker Outputsに記載されているScriptをご活用下さい。

上記の手順で正常に動作しない場合、別のPCでも同様に動作をご確認頂けますと幸いです。

※TLV320AIC3120はオーディオ製品になりますので、フォーラムにご投稿の際はオーディオのカテゴリーにお願い致します。Windows PCでEVMがUSB Audio Deviceとして認識されているようですので、PC上で外部デバイスから録音・再生が可能なアプリケーションを起動し、録音、及び再生を実施してみて下さい。

お問い合わせ頂きましたTLV320AIC3120のRegister設定に関しまして以下の通り、

コメントさせて頂きます。① Page 0 / Register 1 : Software Reset

ResetがActiveのように見えますがReadbackした際、D0は常に”1″のままでしょうか?② Page 0 / Register 4 : Clock-Gen Muxing

CODEC_CLK=PLL_CLKで、PLL_CLK=BCLKが選択されています。

外部から供給されるBCLKを内部のPLLに入力し、PLLでMaster Clockを生成して使用することを

想定されておりますでしょうか?

同様にPLLに関する設定(Register 5からRegister 20)につきましてはData Sheet p.67

「7.3.13 CLOCK Generation and PLL」をご参照頂き、意図した設定かどうかをご確認願います。

これらの設定はBCLK、WCLKに適用される周波数に依存致します。

最終的にADC_fsが所望のfsになるかどうかがポイントになります。③ Page0 / Register 36 : ADC Flag Register

ADCがPower-downしているように見えますが、一方でPage 0 / Register 71 : ADC Digital Micでは

D7が”1″ですので、Power-upの設定が適用されています。④ Page 0 / Register 60 : DAC Processing Block / miniDSP Selection

0x0Bを設定されておりますが、Data Sheet p.94に記載されている通り、Do not useになります。⑤ DACの設定

現状の設定ではDACは使用しない設定としてReviewさせて頂いております。お手数をお掛け致しますが、PLL関連の設定を今一度ご確認頂けますと幸いです。

お問い合わせ頂き、ありがとうございます。

CCSとDRV8301-69M-KITを接続することが出来ない場合には以下のトラブルシューティングが参考になりますので、ご確認頂けますと幸いです。

Kato

NT 様

フォーラムにお問い合わせ頂き、誠にありがとうございます。

お問い合わせ内容につきましてはメールにてご対応させて頂きます。

Kato

ET 様

追加のご質問がないようですので、本件に関しましてクローズとさせて頂きますが、

ご不明点等がございましたら、遠慮なくお問い合わせ下さい。Kato

yong 様

ISO7141のData Sheet p.10のTEST CONDITIONSに以下の記載がございます。

「AC signal: All channels switching with square-wave clock input; CL = 15 pF」

ご認識の通り、p.10の試験条件における4CH分のTyp、及びMaxの消費電流になります。

また、ご参考までにp.12のFigure 3.も合わせてご参照頂けますと幸いです。Kato

ET 様

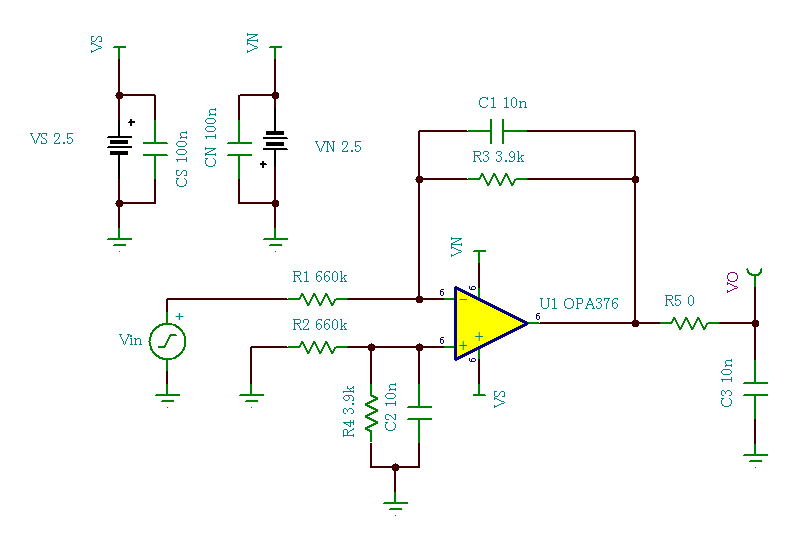

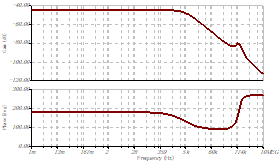

Closed LoopのGain特性は以下の通りで、回路図と合わせてご確認下さい。

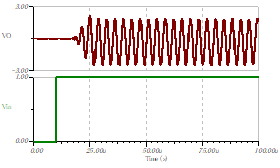

出力負荷が10nFですので、「位相余裕がない」条件です。

次にTransient解析のStep応答についての例ですが、発振しています。

「実機で何をどのように確認するのか?」についてですが、もちろんFRAなどを使用して

ループゲインを確認することは可能ですが、Simulationで行ったStep応答でも

Loopの安定性を簡易的に確認することが出来ます。

Simulationと実機との差についてコリレーションを取り、その差を埋めることが重要です。FRAで測定する場合はSimulationで用いた手法とは異なりますので、詳細に関しましては

測定器メーカにお問い合わせ頂けますと幸いです。

Kato

ET 様

OpAmpを用いて負帰還回路を構成する場合、ご用途にもよりますが、Gain Marginは7dB~10dB、

Phase Marginは45°~60°以上を一つの目安としています。

低周波領域であれば、帯域との兼ね合いもありますが、個人的にはPVT変動を考慮し、

特にPhase Marginは60°以上を確保するようにします。

また、実際にご使用になるClosed LoopでGain Peakの有無をご確認下さい。

いずれに致しましてもSimulationはあくまでSimulationですので、実機にてご確認頂くことを

推奨させて頂きます。

その方が得られるものが多いと思います。初歩的な内容になりますが、ご案内させて頂きましたOpAmpのWebinarにご参加頂けますと幸いです。

Kato

ET 様

こちらの位相線図は180°から始まっておりますが、

これは”Vout” / “Vin” =–Aβ になるからだと考えれば良いでしょうか。→ ご理解の通りです。

実数ではなく、振幅と位相の成分を持つ複素数とお考え下さい。

また、位相は180°からスタートしておりますが、位相遅れ0°に相当します。また、このボード線図の場合、下記認識で正しいでしょうか。

・位相余裕はゲインクロスオーバー周波数における位相の絶対値

・位相が0°となる周波数においてゲインが>0dBのとき発振する→ 上記のループゲイン特性に対するPhase MarginとGain Marginの考え方についてはご認識の通りです。

今週の8/19にオペアンプに関する第1回目のWebinarを開催致しましたが、第2回目を9/2に予定しております。

次回は「AC特性の基礎」で、既にご存知の内容かと思いますが、ご参考までにご案内させて頂きました。初心者のためのオペアンプセミナー

https://www.macnica.co.jp/business/semiconductor/events/texas_instruments/134775/Kato

-

投稿者投稿