フォーラムへの返信

-

投稿者投稿

-

ET 様

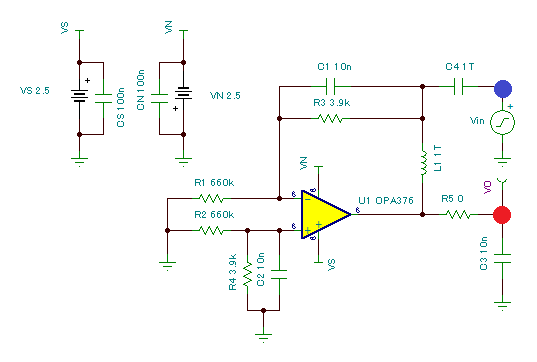

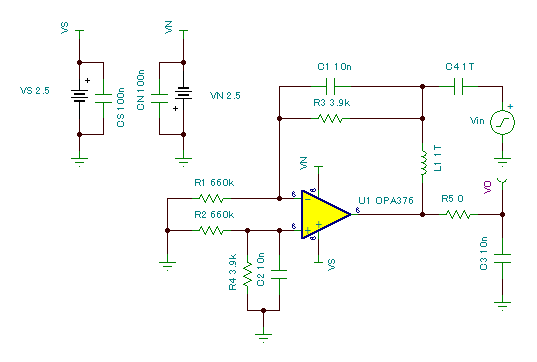

TINA-TIの場合には信号源と出力Pinにより自動的にGain特性を取得することが出来ます。

入出力電圧ノードの指定が必要ということでしたら、「”Vout” / “Vin” = “赤のノード” / “青のノード”」になります。

Kato

ET 様

・貼付いただいたボード線図はどの電圧比を示しているのでしょうか。

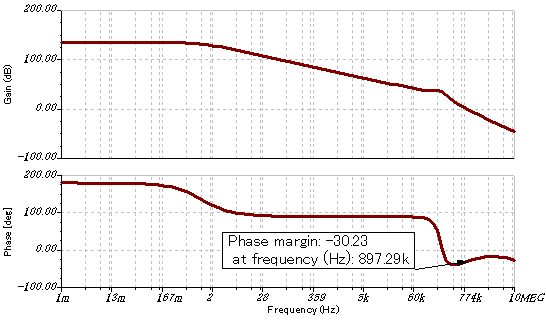

→ ループゲインAβになります。

・ご教示頂いたシミュレーション回路で安定性を見れる理屈についてご教授頂けないでしょうか。

→ 若干手法は異なりますが、検証の目的はご教示頂きました資料に記載されている内容と同様です。

ループのDCに影響を与えないように容量結合(C4)で信号を入力し、Inductor(L1)で

周波数成分をカットし、ループゲインを検証した一例になります。Kato

ET 様

TINA-TIを用いてPhase Marginを確認致しましたが、残念ながら、既に位相が180°以上遅れております。

現状の回路構成ですと、出力負荷C3=0.01uFを例えば10pFに変更して頂けますと、Phase Marginが確保できるようです。

また、OPA2376の推奨動作電圧範囲は2.2V(±1.1V)~5.5V(±2.75V)になりますので、ご注意下さい。

Kato

ishi1126 様

原因調査のご進捗状況を共有して下さり、ありがとうございます。

追加でご不明な点などございましたら、新規でご投稿頂けますと幸いです。

Kato

ishi1126 様

その後、ご状況はいかがでしょうか?

本件に関しまして一旦クローズとさせて頂きますが、ご不明点等がございましたら、

遠慮なくお問い合わせ下さい。Kato

ishi1126 様

Ferrite Beadsの短絡試験に対して低抵抗を挿入して実施した場合の結果はいかがでしたでしょうか?

TPA3112D1の過電流検出の閾値はバラツキもありますが、4A程度になります。

実測結果と一致しておりますでしょうか?Kato

ishi1126 様

原因調査に関する追加情報をご提供下さり、ありがとうございます。

InductorのDCRが大きいことが起因していると予想されているとのことですが、裏取りのために

Ferrite Beadsで短絡試験を行う際、定格電力の高い低抵抗を挿入して短絡して頂くことは可能でしょうか?

また、VCCやGNDに短絡した際に/FAULTがLowにAssertされる際の出力電流の実測値をご教示願います。念のための確認になりますが、短絡試験はSP_L1_OUT_DB1とSP_L2_OUT_DB1に対して実施されているという

認識ですが、正しいでしょうか?Kato

ishi1126 様

お忙しい中、Ferrite Beadsの型番をご教示下さり、ありがとうございます。

Inductorよりも定格電流が高いFerrite Beadsをご使用頂いているということを理解致しました。

Kato

ishi1126 様

追加でご確認させて頂きたいのですが、Ferrite Beadsの型番をご教示頂けますと幸いです。

Kato

ishi1126 様

申し訳ございませんが、TPA3112D1EVMは保有しておらず、実機確認は行っておりません。

Inductor L5、L6をFerrite Beadsに変更することで、短絡試験時に/FAULTはLowに

Assertされるとのことですが、回路図上、/SDと/FAULTが直接接続されているため、

自動復帰を繰り返す動作になりますが、実機でもそのような動作でしょうか?また、ご使用のInductorの型番よりWebでSpecを確認致しましたが、直流重畳特性のDataがなく、

参考値として22uHと47uHで確認しますと、直流重畳許容電流が小さいようです。

例えば、直流重畳許容電流が大きい別のInductorでご確認頂くことは可能でしょうか?Kato

ishi1126 様

追加でご確認頂きたいのですが、入力を1kHzから無信号にした際に

OUTP-OUTNをShortすると/FAULTはLowにAssertされますでしょうか?Kato

ishi1126 様

追加の波形情報をご提供下さり、ありがとうございます。

同様にOUTPを+12.5V、及びGNDにShortした際の波形もご提供頂くことは可能でしょうか?

正常にOvercurrent Protectionが機能していると思われるので、実測による過電流の閾値を

確認したいと考えております。Kato

ishi1126 様

回路図の情報をご提供下さり、ありがとうございます。

TPA3112D1は過電流を検出した際に/FAULTをLowにAssertしますので、

OUTP-OUTNをShortした際に過電流が流れるような条件に対しては

短絡保護が働きます。

OUTP-OUTNをShortした際、入力にはAudio Sourceや1kHzなどを

入力して検証を実施されたのでしょうか?Kato

ishi1126 様

TPA3112D1に関してOUTP-OUTN間のShortにおいて/FAULTがLowにAssertされないとのことですが、

出力間をShortした際の入力条件とShortした箇所(出力端子 or LC Filter後のSpeaker端子)をご教示頂けますでしょうか?

また、Short時のOscilloscopeの波形を共有して頂けますと幸いです。Kato

ishi1126 様

LEFT_LOPの出力歪みに関しまして以下の項目をご確認頂き、

情報をご提供下さいますよう、宜しくお願い致します。<ご確認事項>

(1) 回路図について

・各電源端子にDecoupling Capacitorの記載がないようですが、Device直近に

高周波用と低周波用のCapacitorが実装されておりますでしょうか?・各Clock Lineにダンピング抵抗が挿入されていないようですが、

送信回路側に挿入されておりますでしょうか?・LEFT_LOP/Mの負荷は何になりますでしょうか?

後段にClass-D Ampが接続されている場合、Codecによって生成される帯域外Noiseが出力されるため、

30kHz程度のLPFを追加することを推奨致します。(2) 各Clock波形の追加取得

・BCLK、WCLK、DINについて位相関係がわかるレベルのScreenshotを取得願います。Kato

-

投稿者投稿