フォーラムへの返信

-

投稿者投稿

-

ten様

ご確認いただき、ありがとうございます。

添付いただいた資料はRST端子をJTAGモードで使用する場合の推奨回路になります。

赤枠のプルアップ抵抗値、コンデンサ値は同データシート 4.4 Connection of Unused Pinsにも記載されておりますので、合わせてご確認ください。現在発生している症状はリセットICを接続されず、添付いただいた回路通りでしょうか。

また、もし可能でしたらコンデンサ値を低い値のもの(例:1nFなど)に変更頂いても現象発生するかご確認いただけますでしょうか。

コンデンサ値はデータシート4.4より、2.2nFを超えてはならない旨、記載されておりますが、下回る場合は特に問題ございません。

また追加で恐縮ですが、次の点についてもご教授いただけますでしょうか。

1. CCSのバージョンはいくつを使用しておりましたでしょうか。

以上、よろしくお願いいたします。

Cruijfften様

ご返信ありがとうございます。

初期設定についてサンプルプログラム記述の通りとのこと、承知いたしました。I2Cのプルアップ抵抗値については推奨値はメーカーで規定されておりませんが、1kΩで問題ないものと考えております。

電源のご確認(1,2)について、お手数ですがわかりましたらご連絡いただけますようお願いいたします。

Cruijff

madridista様

1. 先程の回答から1点追加でご確認をいただけますでしょうか。

- 貴社ソフト設計にて、SFRRPCRレジスタ「SYSRSTRE」ビットはクリアされておりますでしょうか。

当ビットはRESETピンの内部プルダウン/プルアップ抵抗を有効にするビットで、デフォルトは「1(有効)」となります。

ただ、MSP430FR6989のErrata「PORT28」によると、このビットをクリアするとTESTピンの内部プルダウン抵抗が無効となり、消費電流増加する恐れがございます。お手数ですが、上記の可能性があるかご確認をいただけますでしょうか。

2. ノイズ対策として、先程の回答に加えて、次の点についてご確認ください。

- TEST端子のトレースを短くできるか

- 外部プルダウン抵抗によって、消費電流増大を防げるか

TESTピンは通常、内部プルダウン抵抗が有効となっておりますが、ノイズの影響を受け、ピンレベルHighとなる可能性があります。これを抑制するため、上記2点でノイズ対策を強化できるか貴社にてご評価をいただければ幸いです。

メーカーフォーラムでも上記のようなTEST端子に関するスレッドが御座いましたので、ご参考いただけるものと考えております。

TI E2E Community – MSP430FR6922 TEST Pin Noise Immunity

TI E2E Community – MSP430F5419A: Noise on TEST pin回答が前後した形となり、お手数おかけしますが、

まずはじめ本投稿内容についてご確認を頂き、こちらでもノイズ影響を受ける場合は、先投稿の内容をご確認ください。以上、よろしくお願いいたします。

Cruijffmadridista様

MSP430のESDは、HBMで±1000V、CDMで±250Vと定義されており、

それぞれJEDECに規定されたモデルに従うものと考えております。

これはMSP430すべてのシリーズで共通の規定となります。JEDECに規定されたモデル以外での静電気試験はメーカでの試験例がなく、どのような挙動になるか情報がございませんでした。

「特定ピンにのみ静電気を印加する」といった場合は、絶対最大定格(Voltage applied to any pin)の規定を超えた電圧を印加しており、デバイスを破損させる可能性がございます。

絶対最大定格、ESD定格はそれぞれデータシート(5.1 Absolute Maximum Ratings)、(5.2 ESD Ratings)にて記載されております。静電気ノイズへの対策についてですが、システムレベルでの対策も一つの検討方法ではないかと考えております。例として、GND層、パターンを厚くする、パターンの引き回しをお見直しいただく、筐体レベルでシールドにより保護するなどございます。

下記資料には、MSP430におけるESD定格の情報や静電気へのシステム単位での対策案等も記載されております。

ご参考にいただければと考えております。MSP430™ System-Level ESD Considerations

http://www.ti.com/lit/an/slaa530/slaa530.pdf以上、よろしくお願いいたします。

CruijffdengensekkeiGT様

恐れ入りますが、ご所望の資料についてはメーカーおよび弊社にて用意がございません。

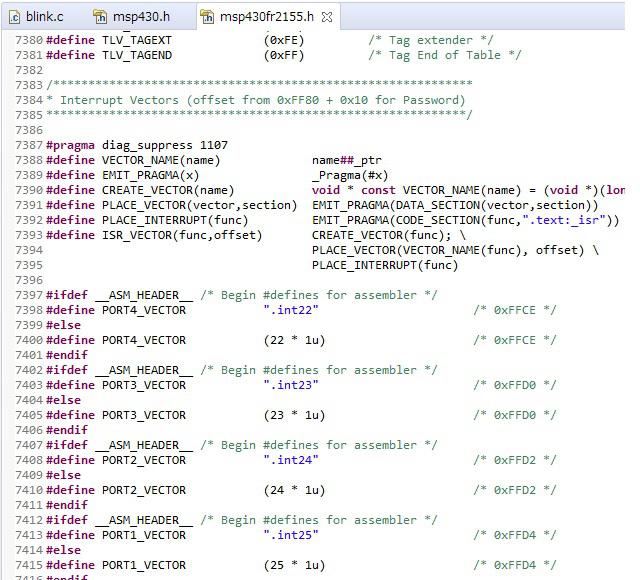

ただ、msp430fr2155.hにてVECTOR名と対応アドレスの定義が記載されております。

ご認識いただいているユーザーズガイドでの記載と合わせてお読みいただけますと、C言語で割り込みベクタを記述する際のご参考になると考えております。ご不便をおかけしますが、同ヘッダファイルの内容をご確認いただければ幸いです。

以上、よろしくお願いいたします。

Cruijfften様

MCLKを12MHzとして使用する場合、データシートP.20 5.3 Recommended Operating Conditionsより

fsystem (with FRAM wait state)の通り、NWAITSx = 1と設定する必要がございます。

お客様のソフトウェアにてそのように設定されているかご確認いただけますでしょうか。

下記サンプルプログラムは内部DCOでの設定になりますが、16MHz設定する際、NWAITSx = 1と設定されており、ご参考いただけるものと存じます。MSP430Ware – msp430fr69xx_cs_02.c

その他については恐れ入りますが、現時点の情報では原因特定は難しく、

いくつか切り分けが必要であると考えております。

そこで、以下についてご確認をいただけますでしょうか。1. ツールを外しての電源供給はDVCC何Vでしょうか。

2. 安定化電源による電源供給でも、こちらの現象は発生しますでしょうか。3. LPMは使用されておりますでしょうか。使用されている場合、その種類をお教えください。

4. I2Cのプルアップ抵抗は外付けで用意されておりますでしょうか。お手数ですが、ご確認のほどよろしくお願いいたします。

CruijffOZSHG1231様

お問い合わせ頂き、ありがとうございます。

DCOのクロックはFLLのリファレンスオシレータ(REFO)に依存し、その精度は±3.5%になります。(データシート 5.19 Internal reference, Low-Frequency Ocillatorより)

UARTのボーレートはBRCLKにて入力するクロック精度に依存しますので、DCOを使用される場合は、ボーレートの精度は±3.5%となります。

参考までに外部水晶振動子を使用したときのボーレートとエラー率の参考値がUser’s Guideにございます。

基本的にUser’s Guideのエラー率よりもDCOで使用したときのほうが精度は落ちるものとお考えいただければと思います。

MSP430x5xx and MSP430x6xx Family User’s Guide (Rev. Q)

36.1.13 Typical Baud Rates and Errors

http://www.tij.co.jp/jp/lit/ug/slau208q/slau208q.pdf以上、よろしくお願いいたします。

CruijffTKS18様

お問い合わせいただきまして、誠にありがとうございます。

大変恐れ入りますが、本件につきまして弊社担当者よりご連絡させていただきます。

ご不便をおかけしますが、何卒よろしくお願い申し上げます。Crujff

temper様

記述いただきましたサンプルプログラムファイルはMSP-EXP430F5529LP(評価ボード)用のサンプルプログラムでございます。

実験ボード(MSP-EXP430F5529)はご案内したURLより「設計ファイルのダウンロード」にアクセスいただくと、ハード設計ファイル/デモ用サンプルコードがございますので、こちらを参照ください。こちらよりサンプルプログラムをダウンロードいただき、「SDcard.c」「SDcard.h」というファイルがあり、こちらがご参考いただけるのではないかと思われます。

詳細はこちらのファイルにてご確認ください。また、実験ボードのユーザーズガイドは下記URLよりご参照いただけますので、合わせてご参照ください。

http://www.ti.com/lit/ug/slau330b/slau330b.pdf以上、よろしくお願いいたします。

Cruijfftemper様

MSP430F5438A – TUSB3410構成では、ソフトウェアを変えても機能追加することは難しいものと思われます

MSP-EXP430F5529(実験用ボード)は下記ページにてMSP430F5529のサンプルプログラムも公開されておりますので、ご参考いただけるかと思います。

http://www.tij.co.jp/tool/jp/MSP-EXP430F5529

以上、よろしくお願いいたします。

Cruijfftemper様

こちらの基板につきまして、TI社製基板になりますでしょうか。その場合型番についてお教えください。

TI社製基板でない場合、大変恐れ入りますが、

基板販売元へ同内容をお問い合わせ頂ますよう、お願いいたします。Cruijff

dengensekkeiGT様

「SHIは外部信号なのでDownするのがもっと後になる場合かあると思います。

その場合にはStopSamplingについてはSHI信号のDownと同期せず、SHIのDownよりも前にStopSampling完了する」上記のご理解で問題ございません。

以上、よろしくお願いいたします。

CruijffUBS様

お問い合わせいただきまして、ありがとうございます。

MSP-FETならびにGANGプログラマには、MSP430との通信のノイズ対策として、

調整済みの抵抗、ESD保護ICが筐体内部回路にて取り付けられております。このため、MSP430との間に推奨値以上のコンデンサ、または抵抗を入れると、

JTAG通信が失敗する可能性があります。

基本的に推奨回路通りに設計いただくことをお願いいたします。MSP-FETの回路は下記資料よりご確認をいただけます。

MSP Debuggers User’s Guide (Rev. L)

P.22~ 5.6.5.4 Scematics

http://www.tij.co.jp/jp/lit/ug/slau647l/slau647l.pdfJTAGラインの推奨回路につきましては下記資料をご確認ください。

MSP430 Hardware Tools User’s Guide (Rev. AD)

P.21 Figure 2-3.Signal Connections for 2-Wire JTAG Communication (Spy-Bi-Wire) Used by All MSP430 SBWCapable Devices That are Not Part of F2xx, G2xx, F4xx Families

http://www.tij.co.jp/jp/lit/ug/slau278ad/slau278ad.pdf以上、よろしくお願いいたします。

CruijffdengensekkeiGT様

メーカーへ確認したところ、

「SHI信号はあくまでサンプリング開始のトリガのみで、Pulse Sample Modeではサンプリング時間までHighを維持する必要はありません。」

この解釈で間違いない、とのことでした。Figure 21-8について非常に分かりづらく紛らわしいと思いますが、上記解釈でご覧いただければと思います。

以上、よろしくお願いいたします。

CruijffdengensekkeiGT様

Pulse Sample Modeではあくまで、ADCSHP=1に設定し、ADCSHTxで設定することでサンプリング時間をユーザーの任意に設定することができるモードになります。

そのため、SHI信号はあくまでサンプリング開始のトリガのみで、Pulse Sample Modeではサンプリング時間までHighを維持する必要はありません。

上記はUser’s Guide P.544 21.2.5.2 Pulse Sample Mode の内容になりますので、合わせてご確認ください。Figure21-8の表記につきましては、メーカーへ問い合わせをさせていただきますので、少々お待ちください。

お手数ですが、よろしくお願いいたします。

Cruijff -

投稿者投稿