フォーラムへの返信

-

投稿者投稿

-

ご回答くださりありがとうございます。

「非常に弱いプルダウン」とのことですが、具体的に何を指すのでしょうか。ご回答ありがとうございます。大変勉強になります。

最後の質問と申し上げておりましたが、

すみません、もう少々追加させていただきます。・また、実際にご使用になるClosed LoopでGain Peakの有無をご確認下さい。

Closed LoopのGain Peakの有無が何を意味するのかご教示頂けないでしょうか。・実機にてご確認頂くことを推奨させて頂きます。

通常、実機で確認する場合もシミュレーション回路のように

LとCを接続し、FRAで測定するのでしょうか。

もしそうであれば1TF,1THは現実的でないと思いますが、

どの程度の定数を用いるのでしょうか。ご回答くださりありがとうございました。

セミナーの方も参加を検討したいと思います。最後にもう1点質問させてください。

こういった増幅回路におけるゲイン余裕と位相余裕の推奨値があればご教示願います。ご回答くださりありがとうございます。

こちらの位相線図は180°から始まっておりますが、

これは”Vout” / “Vin” =–Aβ になるからだと考えれば良いでしょうか。

また、このボード線図の場合、下記認識で正しいでしょうか。

・位相余裕はゲインクロスオーバー周波数における位相の絶対値

・位相が0°となる周波数においてゲインが>0dBのとき発振する

※実際には余裕が必要だと思いますが。ご回答くださりありがとうございます。

>→ ループゲインAβになります。

こちらで同様のシミュレーションを行いたいため、

具体的にどの部位の電圧比か教えて頂けないでしょうか。あるいはTINAの場合、特に電圧比を取らずとも

ループゲインが選択肢としてあるのでしょうか。ご回答くださりありがとうございます。

追加質問させていただきます。

・貼付いただいたボード線図はどの電圧比を示しているのでしょうか。

・ご教示頂いたシミュレーション回路で安定性を見れる理屈についてご教授頂けないでしょうか。

https://kobaweb.ei.st.gunma-u.ac.jp/lecture/2016-6-21gendai.pdf P16のような資料、

あるいはご説明を頂ければ大変助かります。失礼いたしました。

ICT=インサーキット・テスタの略称です。

NCピンを含むあらゆる電位にチェッカーランドを設けて、

電位間のインピーダンスを測定する検査となります。NCピンを一括でまとめられる場合、

チェッカーランドの数を減らすことができるため、

このようなご相談をさせていただきました。既にUCC21520を手配済みのため、

こちらの素子で進めたく考えております。残念ですが、規定されていない旨承知しました。

ご回答くださりありがとうございました。ご回答くださりありがとうございます。

承知しました。ご回答くださりありがとうございます。

>そのため、システムに併せて電源IC(TPS62420)のEN2端子の電圧などの調整をお願いします。例えば、EN2の端子の電圧を変えて、EN2のスレッショルドをより高いところにもっていくなどです。

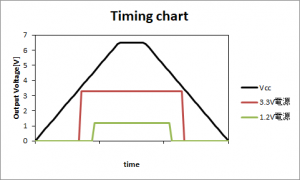

EN1,EN2端子の電圧を調節して、例えば、

3.3VはVcc=4Vで起動、1.2VはVcc=4.5Vで起動することで

3.3V<1.2Vの状態を回避するという理解で正しいでしょうか。

※添付図この場合、起動電圧が異なりますが、

5.9.1.3 V DD Requirementsは満たせるものとして考えて良いでしょうか。

・V DDOSC and V DD must be powered on and off at the same time.

VDDOSC(3.3V)とVDD(1.2V)は同時にオン/オフしなければならない。

・V DDOSC should not be powered on when V DD is off.

VDD(1.2V)がオフの時、VDDOSC(3.3V)はオンすべきではない。別のトピックで以前質問した際に、下記回答を頂いております。

>電源の立ち上がりタイミングにつきましては、特に明記はなく、

>5.9.1.2 VDDIO, VDDA, VDD3VFL, and VDDOSC Requirements、

>5.9.1.3 VDD Requirements

>に各電源が0.3Vに収まる、かつVDDはVDDIOより0.3Vを超えないことが記載されております。

>この範囲であれば、開始点は異なっていても問題はございません。

https://emb.macnica.co.jp/forums/topic/10450/

結局のところ、他の要件が満たせるのであれば

「同時にオン/オフ」は気にしなくてよいのでしょうか。ご回答くださりありがとうございます。

>「C:\ti\c2000\C2000Ware_3_01_00_00\boards\controlCARDs\TMDSCNCD28379D\R1_3」

ローカルファイルへのパスとなっているため、

ネットワークへのパスをご教示頂くか、ファイルをアップロードいただけると大変助かります。>保護ダイオード

品番確認できていないため、憶測で恐縮ですが、

どんなにVfが小さいダイオードでも電流値によっては0.3Vを超過するかと思います。

1.2V系に比して3.3V系の負荷が大きい場合は、3.3V系 < 1.2V系となり、

それなりの電流が流れることが考えられます。

この場合、0.3Vを超過する可能性があるかと思うのですが、

ご回答いただいた構成であれば問題ないでしょうか。ご回答くださりありがとうございます。

下記URLの評価ボードの回路図を拝見しましたところ、

保護ダイオードがあるようには見受けられません。

http://www.ti.com/lit/ug/sprui25d/sprui25d.pdfP10によると3.3Vから1.2Vを作られていますが、

この構成であれば遮断時も要件を満たすと考えて良いでしょうか。

あるいは問題があるのであれば推奨構成をご教示頂きたく思います。ご回答くださりありがとうございます。

・いずれの誤差も偶然誤差として扱えると考えて良いでしょうか。

それぞれの誤差は無相間とのことですので、

温度や個体による系統誤差ではなく、偶然誤差と考えて良いでしょうか。・誤差の原因について

内部トランジスタの誤差や熱雑音による誤差などがあるかと思うのですが、

熱雑音による誤差が支配的なのでしょうか。・データシートの記載値と6σについて

各誤差は正規分布を仮定できるとのことですが、

データシートの記載値が±Err LSBであった場合、

±Err LSBが±6σ区間になると考えて良いでしょうか。

※±Err LSB=±6σ区間を逸脱する確率は3.4ppm程度ご回答くださりありがとうございます。

もう一点質問がございます。

max値がVDDIO + 0.3Vと定義されていますが、これは最大定格であって、

閾値の最大値ではないとの認識で相違ないでしょうか。※もし、閾値の最大値がVDDIO+0.3Vであれば、

場合によってはVDDIO相当の電圧を印加してもHにならないかと思います。 -

投稿者投稿