フォーラムへの返信

-

投稿者投稿

-

本件メーカーに確認をしたところ、この抵抗値の明確な最大・最小値については公開されていませんでしたが、メーカー見解としては、おそらく50kOhm±20%以内には収まるだろうとの回答でした。

こちらの値を目安にご設計をお願いできますでしょうか。以上、宜しくお願い致します。

返信が遅れ申し訳ございません。

お問い合わせのADCINポートのプルダウン抵抗の最大・最小値についてはOpenな情報が御座いませんでした。

本件、メーカーに確認致しますので少々お待ちいただけますでしょうか。以上、宜しくお願い致します。

ご返信ありがとうございます。

推奨外部負荷容量以外のものを選定した場合には、正常に発振しないなどの問題が起きる可能性が御座いますので、

ご利用の際には推奨の外部負荷容量の範囲内で設計いただけますでしょうか。以上、宜しくお願い致します。

zen様

お問い合わせありがとうございます。

ご質問の件、以下に回答致します。> データシート(JAJSEZ6H)のP68 表5-15に記載されているCL1,CL2というのは外部負荷容量のことでしょうか?

> 水晶振動子のCLとは違う?

> 下記リンク 4-1 に記載されているC1、C2という認識でよろしいでしょうか?

> https://www.macnica.co.jp/business/semiconductor/articles/basic/127525/ご認識通り、外部負荷容量になります。データシート(JAJSEZ6H)のP68 表5-15の一つ前のページにCL1,CL2の位置について図がございますので、こちらも併せてご参考ください。

> 評価基板のLAUNCHXL-F28379Dでは下記部品を使用されておりますが、データシートのMax24pFを超える外部負荷容量が

> 接続されております。問題ないのでしょうか?評価基板はデータシートの要求を満たしていない設計となっている場合がございますが、もし評価基板とデータシートで差異があった場合には、データシートのパラメータを参考に設計いただけますでしょうか。

> また、外部負荷容量12pF~24pFとのことですが、上記リンクの式 CL=(C1xC2)/(C1+C2)+4に当てはめると、

> 選定される水晶振動子のCLは10pF~16pFの物という理解でよろしいでしょうか?理論的にはその様になると思いますが、実際の最適値については水晶メーカーのマッチングサービスなどをご利用いただき最適値を解析されることをお勧め致します。

以上、宜しくお願い致します。

GPIOピンのプルアップダウンに推奨される抵抗値範囲は御座いません。

GPIO内蔵のプルアップ・ダウンについては、データシートに以下のように定義されております。ここから計算するとおおよそ20kΩ程度の抵抗になっております。また、GPIOにはノイズ対策のためにQualification Windowという機能を使用することもできます。機能の詳細についてはテクニカルリファレンスマニュアルをご参考ください。

以上、宜しくお願い致します。

お問い合わせの件、メーカー確認が取れました。

IDDの最大電流値400mAは、起動時の過渡的な電流も含むものとなりますので

VDDに接続するキャパシタ値についてはこの400mAをベースに設計いただけますでしょうか。以上、宜しくお願い致します。

お問い合わせありがとうございます。

起動時のVDDの消費電流最大値については情報がございません。

本件メーカーに確認いたしますので、少々お待ちいただけますでしょうか。以上、宜しくお願い致します。

ご質問の件、以下に回答致します。

> 各MCUのピンに依存すると言われればそれまでなのですが、

> プルダウン/プルアップ抵抗の強弱の境界値はどのあたりに存在するのでしょうか。申し訳ございませんが、明確な強弱の境界は定義されておりません。

> 当該ピンのようにデータシートに推奨値の記述があれば良いのですが、

> 中には記述のないピンもございます。

> そういった他のGPIOをプルダウン/プルアップする際の抵抗値を決めたく、

> ごきょじ頂けないでしょうか。GPIOの場合には、内部のプルアップ/ダウンを無効にすることが可能となりますので、

外部でプルアップダウンする場合には、無効にしてご利用いただけますでしょうか。

GPIO以外のピンで、内部プルアップ/ダウンが固定となっており、外部抵抗の推奨値の記述のないピンが御座いましたらご連絡いただけますでしょうか。メーカーに確認させていただきます。以上、宜しくお願い致します。

ご連絡いただけますでしょうか。ご返信ありがとうございます。

> 「非常に弱いプルダウン」とのことですが、具体的に何を指すのでしょうか。

紛らわしい表現で申し訳ございません。

内部のプルダウン抵抗値が大きいということになります。

そのため、外部ノイズには弱いということになります。ET様

お問い合わせありがとうございます。お問い合わせの件、以下に回答致します。

> TRSTピンには内部プルダウン抵抗が存在するとあります。

> これについて3点質問させていただきます。

> 1.こちらの抵抗値をご教示頂けないでしょうか。

> 可能であれば最小・最大値もいただけますと助かります。申し訳ございませんが、内部抵抗値については公開されておりません。

> 2.内部プルダウン抵抗があるにも関わらず

> 外部プルダウン抵抗が必要な理由についてご教示頂けないでしょうか。内部プルダウン抵抗は非常に弱いプルダウンとなっておりますので、

外部プルダウン抵抗を接続する必要がございます。> 3.質問2の答えと重複するかもしれませんが、

> 外部プルダウン抵抗が無い場合、どのような不具合が想定されるでしょうか。データシートのTRSTピンの説明を見ますと、以下の記述がございます。

TRST, when driven high, gives the scan system control of the operations of the device.上記は簡単に説明するとデバッグモードになるというものです。

TRSTピンの内部プルダウン抵抗は弱いため、外部プルダウン抵抗がない場合には、

ノイズなどの影響により、このデバッグモードに入ってしまい、誤動作の原因となってしまいます。以上、宜しくお願い致します。

ET様

お問い合わせありがとうございます。

ADCINピンに接続するコンデンサとありますが、R-CフィルタのCと認識しております。

こちらのCの値については推奨値は御座いませんので、御社のアプリケーションに併せてこのR-Cフィルタを設計いただけますでしょうか。一般的には、R-Cフィルタの値から、AD変換に要する時間を求めることが多い考えます。

R-Cフィルタの値からサンプリング時間を計算する例が以下にございますので、こちらもご参考ください。

TMS320F2837xS Microcontrollers Technical Reference Manual

http://www.ti.com/lit/ug/spruhx5g/spruhx5g.pdf

(p.1461) 10.15.2 Choosing an Acquisition Window Duration以上、宜しくお願い致します。

お問い合わせありがとうございます。

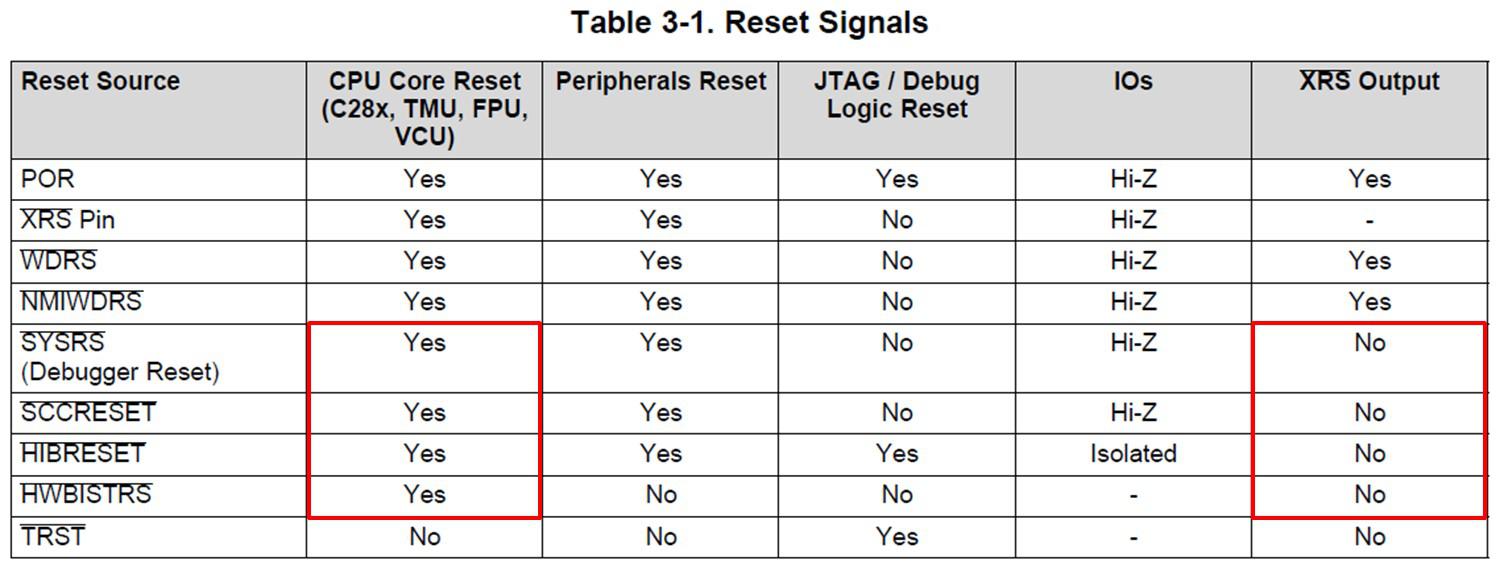

外部リセットが出力されず、CPUリセットがかかるものは以下の4つのReset信号となります。

TMS320F2837xS Dual-Core Delfino Microcontrollers Technical Reference Manual (Rev.G)https://www.tij.co.jp/jp/lit/ug/spruhx5g/spruhx5g.pdf

P.90 Table 3-1. Reset Signalsまた、リセットによる問題である場合には、上記マニュアルのP.356に記載されているRESCレジスタを確認することで、リセット要因を特定することができますので、調査にはこちらのレジスタもご活用いただければと思います。

以上、宜しくお願い致します。

お問い合わせありがとうございます。

外部クリスタルを使用する場合には、ご認識の通り、VSSOSCはGNDと接続をしません。

この場合、VDDOSCのデカップリングコンデンサはVDDOSC-GND間に接続をお願い致します。以上、宜しくお願い致します。

ET様

お問い合わせありがとうございます。

> ば、EN2の端子の電圧を変えて、EN2のスレッショルドをより高いところにもっていくなどです。

> EN1,EN2端子の電圧を調節して、例えば、

> 3.3VはVcc=4Vで起動、1.2VはVcc=4.5Vで起動することで

> 3.3V<1.2Vの状態を回避するという理解で正しいでしょうか。

> ※添付図ご認識のとおりとなります。

> この場合、起動電圧が異なりますが、

> 5.9.1.3 V DD Requirementsは満たせるものとして考えて良いでしょうか。

> ・V DDOSC and V DD must be powered on and off at the same time.

> VDDOSC(3.3V)とVDD(1.2V)は同時にオン/オフしなければならない。

> ・V DDOSC should not be powered on when V DD is off.

> VDD(1.2V)がオフの時、VDDOSC(3.3V)はオンすべきではない。

>

> 別のトピックで以前質問した際に、下記回答を頂いております。

> >電源の立ち上がりタイミングにつきましては、特に明記はなく、

> >5.9.1.2 VDDIO, VDDA, VDD3VFL, and VDDOSC Requirements、

> >5.9.1.3 VDD Requirements

> >に各電源が0.3Vに収まる、かつVDDはVDDIOより0.3Vを超えないことが記載されております。

> >この範囲であれば、開始点は異なっていても問題はございません。

> https://emb.macnica.co.jp/forums/topic/10450/

> 結局のところ、他の要件が満たせるのであれば

> 「同時にオン/オフ」は気にしなくてよいのでしょうか。VDDとVDDOSCが同時にONできない場合には、以下のエラッタに該当し、内蔵クロック(INTOSC)が低速で動作してしまう可能性が御座います。

TMS320F2837xS MCUs Silicon Errata (Rev. H)

http://www.ti.com/lit/pdf/sprz422

INTOSC: VDDOSC Powered Without VDD Can Cause INTOSC Frequency Driftそのため、同時にONしない場合にはエラッタシートに記載の対応(外部のクロックを使用する)をお願い致します。

以上、宜しくお願い致します。

ご返信ありがとうございます。

説明が不足しており申し訳ございません。保護ダイオードはあくまでも補助の目的で接続されており、ご認識の通り、負荷の状態によっては、シーケンスを守ることができない可能性が御座います。そのため、システムに併せて電源IC(TPS62420)のEN2端子の電圧などの調整をお願いします。例えば、EN2の端子の電圧を変えて、EN2のスレッショルドをより高いところにもっていくなどです。

> >「C:\ti\c2000\C2000Ware_3_01_00_00\boards\controlCARDs\TMDSCNCD28379D\R1_3」

> ローカルファイルへのパスとなっているため、

> ネットワークへのパスをご教示頂くか、ファイルをアップロードいただけると大変助かります。こちらについても説明不足で申し訳ございません。以下のC2000wareをインストールいただく、上記のフォルダが展開されますので、こちらをご入手いただけますでしょうか。

C2000ware

http://www.tij.co.jp/tool/jp/C2000WARE以上、宜しくお願い致します。

-

投稿者投稿