フォーラムへの返信

-

投稿者投稿

-

Osugi様

いつも大変お世話になっております。

掲題の件、ご質問ありがとうございます。TMP709 データシートP.8 7.3.3 Set-Point Resistor (RSET)の項内に

記載されたT = temperature threshold in degrees Celsiusは、正確には

IC内部のダイの温度を指します。しかしながら、データシートP11 10.3 Thermal Considerationsに述べられていますように、

IC自体の消費電流は40uAと低いため、コンパレータ出力が高いインピーダンスの負荷を駆動していれば、

基本的に、ICの消費電流による自己発熱は無視することができます。つまり、パッケージ表面とダイの温度は等しいものと考えることができます。

仮に、電源電圧5V、ICの消費電流が40uA、パッケージの熱抵抗がデータシート記載の通り217.9°C/Wであった場合、

計算上ですと、測定環境の温度に対してダイの温度は、40uA×5V×217.8°C/W≒0.044℃高いこととなります。

但しこれは、ICの消費電力(40uA×5V=200uW)が全てパッケージ表面から放熱された場合となります。

通常は、ICのリードからパターンへの放熱等もあり、すべてがパッケージ表面からは放熱されないため、

外部温度とダイ温度の差分はより小さいものとなります。どうぞ宜しくお願い致します。

GT

foobaa001様

いつも大変お世話になっております。

掲題の件、ご質問ありがとうございます。

以下文中にて回答させて頂きます。・TPSM84624を使う場合、AGNDとPGNDは独立したパターンにする(IC内部で一点GNDされている)

・PGNDは大電流が流れ、ノイズが乗って変動しやすいので、変動しないようにインピーダンスの低いパターンにする→はい、上記2点につきましてはご理解の通りになります。

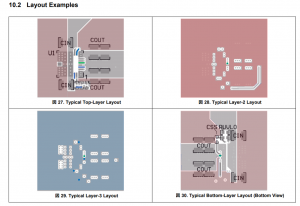

添付しました、データシートP24のパターンレイアウト例をご参照下さい。

図内の赤くなっているパターンがPGND,青のパターンがAGNDとなります。

このパターンレイアウトの場合、多層基板で内層にPGND,AGNDのベタパターンをそれぞれ設けています。

PGNDについては、TOP層、BOTTOM層、内層の各PGNDのパターンを数多くのビアで接続し、インピーダンスを

下げています。・PGNDが変動した場合、供給される電源出力はどのように変化するのでしょうか。

また、それが原因で部品が破損するような可能性はありますでしょうか。→PGNDが変動した状態で、出力電圧の波形を確認しますと、PGNDの変動の影響受け、振幅が広くなった波形が観測されます。

また、動作に対しては一概にどのような影響が出るかは規定できませんが、PGNDが大きく変動することにより、仮にAGNDも

変動してしまうと、内部の制御回路に影響し、設定通りの出力電圧が出なくなってしまう等の不具合が出る恐れが考えられます。

また、上記のような不具合動作に至り、TPSM84624 データシートP5 “Absolute Maximum Ratings”の項に記載されました

各ピンの絶対最大定格値の範囲を逸脱するような電圧が各ピンとICのGND間に印加された場合、デバイスがダメージを負う可能性もございます。・TPSM84624を同じ基板に複数個載せて異る電圧を発生・供給する場合、

それぞれのPGNDはどのように接続することが適切でしょうか。

また、AGND同士は接続する必要はあるのでしょうか。→添付しましたパターンレイアウトを例にしますと、同一基板上の複数のDC/DCコンバータのPGNDについては、

各ICの近くのTOP面(部品面)で大電流ループを形成するのが理想的で、それぞれの大電流ループに

組み込まれるPGNDを内層のベタパターンに接続する形となります。

AGNDに関しては、各PGNDがベタパターンで接続されているのであれば、IC内部でPGNDとAGNDは接続されているため

AGND同士は接続しなくても問題ありません。また、補足となりますが、添付致しましたデータシート記載のレイアウト例に誤りがございました。

添付ファイル内に緑色で記載したTTピン(5ピン)の接続となります。

添付のレイアウトですと、TTピンはフローティングとなっておりますが、データシートP4 TTピンの説明に

ありますように、フローティングにはせず、抵抗を介してAGNDに接続する必要があります。どうぞ宜しくお願い致します。

GT

Attachments:

foobaa001様

いつも大変お世話になっております。

掲題の件、ご質問ありがとうございます。先般の回答の中で、分かりづらい表現及び、説明の不足がございました。

誠に申し訳ございません。

PGNDとAGNDを1点で接続する目的としては、回路内のすべての電圧に対し、基準電位となる1点を定める

ためとなります。

お考えの通り、もし仮にPGNDが電圧変動を起こした場合、AGND側も影響を受けることとなります。

そのため、大電流が流れることが想定されるPGNDに関しては、太く短いパターンレイアウトを用いて、インピーダンスを

下げることを意識して、電圧変動が出ないようにすることが必要となります。お問い合わせ頂きましたTPSM84624に関しましては、ICの内部でAGNDとPGNDの接続が取られていますので

外部での接続は必要ございませんが、通常は基板上のどこか1点でAGNDとPGNDを接続します。この時、DC/DCコンバータのPGNDパターンの位置によって、大きいノイズの発生が想定される箇所があります。

(降圧型のDC/DCコンバータの場合、ICの入力コンデンサのGND側などが該当します。)

DC/DCコンバータのAGNDとPGNDの一点接続の箇所としては、そのようなノイズの発生が想定される箇所を

避ける必要がございます。どうぞ宜しくお願い致します。

GT

foobaa001様

いつも大変お世話になっております。

掲題の件、ご質問ありがとうございます。

また、回答が遅くなりましたこと、お詫び申し上げます。DC/DCコンバータ回路のおけるPGNDは、一般的に大きな電流の流れるループに組み込まれるGNDを指し、

今回お問い合わせ頂きましたTPSM84624であれば、入力コンデンサ/出力コンデンサのGND等が該当します。

PGNDは大電流が流れるラインのため、電圧変動があったり、ノイズが大きいGNDといえます。またAGNDは、ICの動作周波数やソフトスタート時間、出力電圧などの設定を行う外部部品のGNDが該当します。

そのため、ここのGNDレベルが変動してしまうとICがの動作に影響がでる可能性があるため、AGNDについては

安定したきれいなGNDであることが求められます。このように、PGND、AGNDについてはそれぞれ役割が異なるため、本デバイスのようにピンが分かれている

もののほうがより理想に近いパターンレイアウトが可能となります。

またPGND/AGNDについては、電位を合わせることが必要です。

通常は基板上のどこか1点でAGNDとPGNDを接続しますが、このICの場合はICの内部で接続が取られていますので

外部での接続は必要ございません。おっしゃられますように、ICによってはPGND/AGNDが分離していないものもあります。

理由としては、小型パッケージのためのピン数制限や、電流容量の小さい電源のため、

PGNDの電圧変動が小さいと考えられる場合等があります。

GNDが1つのDC/DCコンバータの場合、ハイサイド/ローサイドFETが内蔵されている製品では

通常、GNDはPGNDとして考えます。GT

Take様

“TL720M05GQKVURQ1″及び”TL720M05QKVURQ1″の差異につきましてですが、

モールド材及びボンディングワイヤの素材が異なります。

(Spec上の差異がございませんので、データシート上での差分の記載はございません。)詳細につきましては、すでにご確認頂いておりますTI Websiteの”Material Content Search”での、

“TL720M05GQKVURQ1″及び”TL720M05QKVURQ1″の検索結果でご確認頂けます。どうぞ宜しくお願い致します。

GT

Take様

掲題の件、お問い合わせありがとうございます。

ご指摘頂きましたのは、TI Websiteの”Material Content Search”での、

“TL720M05GQKVURQ1″及び”TL720M05QKVURQ1″の検索結果で、

それぞれのPackage Body Sizeが

TL720M05QKVURQ1 6.1×6.6×2.3

TL720M05GQKVURQ1 6.6×5.2×2.3

と異なっている点かと思います。メーカーサイドに確認しましたところ、TL720M05GQKVURQ1 6.6×5.2×2.3の記述が

誤りとなります。大変申し訳ございません。

本デバイスのTO252パッケージ製品のサイズにつきましては、上記の”6.1×6.6×2.3”

の1種類となります。どうぞ宜しくお願い致します。

GT

aspheric様

お問い合わせありがとうございます。

TPS5450につきましてですが、今回想定されております”入力電圧=出力電圧”という仕様には

対応することが出来ません。本デバイスの動作上の制限として、最大Dutyというものが規定されております。

(データシートP5 6.5 Electrical Characteristics内のMaximum duty cycleの項が該当し、

typ値で89%となっております。)

入出力電圧をスルーで出すには、Duty cycleが100%で動作する必要があります。常時、入出力電圧をスルーで出すことを想定される場合には、TIの製品カテゴリのうち、

・ホットスワップコントローラ

http://www.tij.co.jp/ja-jp/power-management/protection-monitoring-hot-swap/controllers/products.html

または

・電子ヒューズ

http://www.tij.co.jp/ja-jp/power-management/protection-monitoring-hot-swap/efuses/products.html

が、ご検討頂けると思います。どうぞ宜しくお願い致します。

GT

TKS18様

お問い合わせありがとうございます。

DAC7571のSDAピン説明欄に記載されました”Serial data input”の意味合いとしましては、

Serial dataは入力(Write)のみで、Serial dataの出力(Read)が出来ないことを指します。(DataSheet Page1 タイトル ”– I2C INTERFACE (RECEIVE ONLY) –“ および、

DataSheet Page16 DAC7571 I2C-SLAVE ADDRESS:LSB R/-W

‘0’ = Write to DAC7571 ‘1’ = Not Supportedと記載されています。)ただし、I2Cですので、DAC7571からAcknowledgeは出力します。

一方、例として挙げて頂きましたDAC8571では、SDAピン説明に、”Serial data input/output”

と記載されており、この場合は、DAC8571の内部レジスタに値を書き込んだ後で、そのデータが

正しいかを読み返して、確認することが可能です。どうぞ宜しくお願い致します。

GT

KATANA様

掲題の件、お問い合わせありがとうございます。

LM5106 英文データシートP11に記載されました 7.3.1 Start-up and UVLO 及び7.4 Device Functional Modes

の項内の記述によりますと、VDD立ち上がり時は、VDD電圧がUVLOのスレッショルド(6.9V typ)に達するまでは

強制的に出力(HO,LO)はLowとなります。

UVLO解除後につきましては、ENがLowであれば、入力の状態によらず、出力(HO,LO)はLowとなります。

UVLO解除後に、ENがHighとなった場合には、入力の状態によって、HOまたはLOのいずれかが、データシート

P6 Figure 1. LM5106 Input – Output Waveforms に記載されましたtenのDelay後に、Highとなると考えられます。

どうぞ宜しくお願い致します。

GT

-

投稿者投稿