フォーラムへの返信

-

投稿者投稿

-

ご回答ありがとうございました。

追加で質問です。

SYNCCONFIG Register(Offset = 06h)でsynchronous modeとasynchronous modeを選択できますが、

synchronous modeとasynchronous modeのどちらのモードでも

CH1のデータ設定後にCH3のデータ設定を行うまで、CSを2.4us以上Highにする必要がございますでしょうか?ご回答ありがとうございました。

念のため確認させてください。

DAC81408でCH1→CH3→CH5→CH7の順にSPIでDATAを設定しようとしております。

CH1のデータを設定した後にCH3のデータを設定するまでのCSをHighにする時間を、

tCSHIGHを参考に80nsにしようとしておりましたが、

Sequential DAC update wait timeより、CH1のデータを設定した後にCH3のデータを

設定するまでのCSをHighにする時間は2.4us以上必要でしょうか?ご回答ありがとうございました。

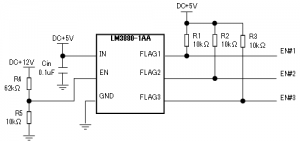

念のために確認しますが、未使用ピンをLowへ論理固定はNGでしょうか?LM3880のpower-down sequencingの質問の回答ありがとうございます。

LM3880の使用方法で追加の質問がございます。

お送りする資料の構成で、VCC+5Vで+12Vを監視しEN#1~3を生成することは

可能でしょうか?Attachments:

ご回答ありがとうございました。

念のため確認させてください。

LMZ12xxxやLMZ14xxxシリーズ以外のLMZシリーズの電源モジュールでは

下記レポートで報告されている不具合が起きてませんでしょうか?

Generic 8D REPORT Power Module LMZ12xxx & LMZ14xxxご回答ありがとうございました。

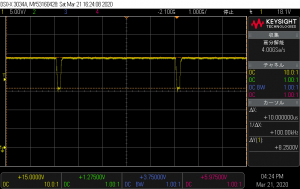

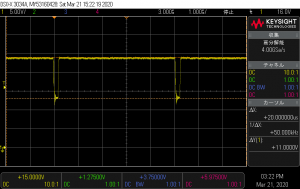

LMZ34002のデータシートFigure43,44の緑色のVinhの波形は、

Figure42の左側のFETのゲートの波形ではなく、U1のPNPのBaseの波形ということで

納得しました。ご回答ありがとうございました。

確認の質問ですが、LMZ34002のデータシートFigure43,44の緑色のVinhの波形は、

Figure42の回路図のどのポイントの波形になりますでしょうか?ご回答ありがとうございました。参考に致します。

ご回答ありがとうございます。

LMR33630はTIのBuck Converter Quick Reference Guideに掲載されているICでもあり、

webenchでのボード線図シミュレーション機能の追加を希望します。ご回答ありがとうございます。

VQFNパッケージのICのVINの配置が、低ノイズ/低EMIといわれているLM61460と似ており、

SOICパッケージのICより低ノイズ/低EMIかと思い質問しました。

念のため質問しますが、パッケージの違いによるノイズ/EMI特性について、

具体的な数値は公開されていないのでしょうか?ご回答ありがとうございます。

話は変わりますが、LMR33630は低EMI,低ノイズとデータシートに記載せれてますが、

パッケージによる違いはございますでしょうか?ご回答ありがとうございます。

例えば、VinのTyp値が12Vより高い例えば24Vで、出力が3.3Vや5Vの場合、

コイルの定数は、データシートのtable2,table3,table4で記載されている定数よりも

大きな定数を選んだ方がよろしいかと思っておりますが、認識は合ってますでしょうか?ご回答ありがとうございました。

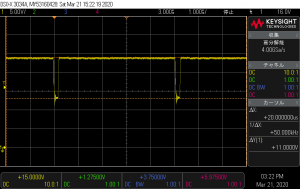

Ciss 340pFがSTD10P6F6を使用した場合、Vgsが11Vになり定格の10Vを越えてしまいました。(fig3参考)

TPS40200のデータシートに記載されているGate driver output voltageは6~10Vなので、

STD10P6F6を使用した場合もVgsが6~10Vになると思っていたので疑問に感じております。

TPS40200の不具合でしょうか?ご回答ありがとうございました。

絶対最大定格の10Vを越えた場合についてご回答頂きましたが、

fig1のように、Gate driver output voltageがmin値の6Vを下回る使い方をした場合はどうなりますでしょうか?

TPS40200は故障する可能性がございますでしょうか?

fig1.png

(※)FET:FDD4141 (Ciss 2085pF) /Vgs 3Vご回答ありがとうございました。

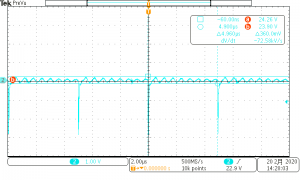

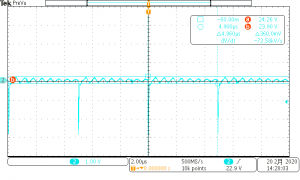

こちらで設計した回路で、Cissの異なる3種類のFETを使用し、出力電流が0Aの場合の

Vgsを確認ました。

FDD4141を使用した場合、データシートに記載されておりますGate driver output voltageのmin値 6Vを下回り、

STD10P6F6を使用した場合、定格の10Vを越えてしましました。

Gate driver output voltageがデータシートで記載されている6~10Vの範囲外で使用した場合

IC故障の原因になりますでしょうか?

特に、Gate driver output voltageのmin値の6Vより小さい場合、IC故障の原因になりますでしょうか?取得した波形もお送りします。

fig1.png FET:FDD4141 (Ciss 2085pF) Vgs 3V (問題点)Gate driver output voltage min値 6Vを下回る。

fid2.png FET:FDD5614 (Ciss 759pF) Vgs 8.25V

fig3.png FET: STD10P6F6 (Ciss 340pF) Vgs 11.00V (問題点)定格の10Vをover-

この返信は5 年、 12 ヶ月前に

maida さんが編集しました。

-

投稿者投稿