フォーラムへの返信

-

投稿者投稿

-

ご連絡が遅くなり申し訳ございません。

TXS0206の消費電力につきまして、以下のページをご参照頂きますようお願いいたします。

該当ページの下の方に計算用のExcelも記載されておりますので、そちらもご活用頂ければと存じます。

頂いたご質問に関して、メーカーに確認いたします。

少々お時間を頂けますと幸いでございます。

お問い合わせ頂きありがとうございます。

残念ながらTI製品で該当する製品はございませんでした。

仮に入力をLowに固定した場合は、R1, R2が消費電力に影響します。

またデータ書き込み時の消費電力はR1, R2も一因になるかと存じますが、実動作条件におきまして主な要因としては入力信号周波数とバスラインの寄生容量が関わってくるかと存じます。

入力信号周波数が早くなればなるほど、消費電力が大きくなります。

寄生容量が増えればVccからチャージしなければいけない電力が増えるため消費電力が増加します。

maida様

現在の初期設定の手順で問題ございません。

タイミングとしてはレジスタアドレス0x0Eh設定時にDACの更新を行っておりますので、2.4us以上待機時間を設けた後にレジスタアドレス0x09hにてPower-down modeを解除して頂ければと存じます。

以上、宜しくお願いいたします。

Nishie

maida様

■13でTRIGGER Register(0x0E)に0x0010をwriteして更新しようとしており、その場合LDACpinをLOWにする必要はないとの認識で合ってますでしょうか?

また、13~14の間に2.4us(Tdacwait)以上の待機時間が必要ということでしょうか?

→ご認識の通り、TRIGGER Registerに0x0010を書き込んで頂ければ、LDACピンをLowにする必要はございません。

はい、13~14の間に2.4us以上待機時間を設けて下さい。

■SPICONFIG Register(0x03)の初期値が0x0A24ですが、power-down modeからacitve modeにする為、1でSPICONFIG Register(0x03)に0x0A04を設定しておりますが、問題がございましたら教えて下さい

→問題ございません。

以上、宜しくお願いいたします。

Nishie

maida様

大変お待たせいたしました。

・初期設定時、1~13までのCS Highの時間は50ns以上設けて下さい。

13~14の間にLDACをLowにした後、DACレジスタ更新のため2.4us(Tdacwait)以上待機時間を設けて下さい。

また、レジスタアドレス0x03hのデフォルト設定は0x0A24になります。

・DAC出力更新において、1~5までのCS Highの時間は50ns以上設けて下さい。

5でLDACをLowにした後、DACレジスタ更新のため待機時間を2.4us(Tdacwait)以上設けて下さい。

以上、宜しくお願いいたします。

Nishie

maida様

大変申し訳ございません。

継続して、メーカーへ以下の内容で確認を行っているのですが回答が得られていない状況です。

1. 初期設定、DAC更新の方法に問題がないかどうか

2. 初期設定時、データレジスタ間のCS Highの時間が50nsか2.4usかどうか

3. DAC更新時、CS Highが80nsで動いているが問題ないかどうか

以上、宜しくお願いいたします。

Nishie

maida様

回答が遅くなってしまい申し訳ございません。

セッティングレジスタ(0x02h~0x0Eh)設定後のCS Highの時間は最低50ns設けて頂ければ問題ございません。

セッティングレジスタ以外のレジスタ設定に関しては、レジスタ設定後、2.4us以上待機時間を設けて頂きますようお願いいたします。

以上、宜しくお願いいたします。

Nishie

maida様

ご回答頂きありがとうございます。

・OUT1, 3, 5,7で負の出力電圧(-10Vと-5V)が発生しているとのこと承知いたしました。

正の出力電圧になることはないという認識でよろしかったでしょうか。

・ご認識の通り、DACレジスタをReadして確認して頂きたかったのですが、SDO接続しておらず値が読み出せないとのこと承知いたしました。

・アクセス間隔を長くしたとありますが、具体的にどの間隔をどの長さに変更したのかご教授頂けないでしょうか。

以上、宜しくお願いいたします。

Nishie

maida様

#14060にて「初期設定時には一部出力電圧が反映されないと言った現象が100%発生するものの」と記載されておりますが、どのCHにどんな異常が発生しているのか詳細をご教授頂けないでしょうか。

また異常が発生したCHのレジスタデータをフィードバックして頂けないでしょうか。

初期設定時のレジスタアドレスの順番やWait時間に問題がないかについては、現在メーカーに確認中です。

申し訳ございません。

考えられる原因としてClock等にノイズが入っておりシリアルデータが正確に反映されていない可能性がございます。

以上、宜しくお願いいたします。

Nishie

maida様

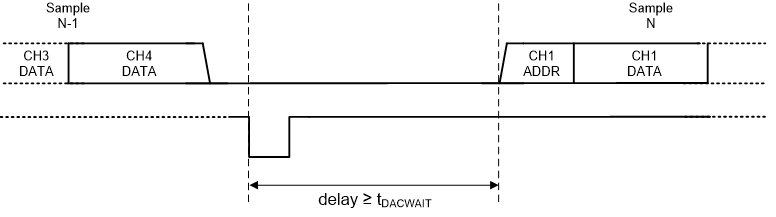

■LDACの立ち下りエッジから再度アドレス0x14(or 0x15)に16bitのデータを設定を行う(CSの立ち上がりエッジ)までの待機時間だと認識しておりますが、Synchronous mode時に、この時間を2.4us以上に設定して頂くことでデータシートの規定内での動作となります。

また5(LDACの立ち下がりエッジ)から再度5(LDACの立ち下がりエッジ)の間隔を2.4us以上に設定して頂く事でもデータシートの規定内になると存じます。

■タイムチャートのSample N-1はStreaming modeでの動作となるため、CH3とCH4の間にCS Highの時間はございません。

■申し訳ございません。

初期設定時の待機時間について、まだ明確な事が分かっていない為、分かり次第ご連絡できればと存じます。

年末のため回答にお時間がかかってしまう可能性がございます。ご了承ください。

以上、宜しくお願いいたします。

Nishie

maida様

お待たせして申し訳ございません。

TdacwaitはSynchronous modeの場合、LDACの立下りエッジから後続のLDACの立下りエッジまでの待機時間となります。

下の図の2番目の波形がLDACになります。

また、レジスタ設定において

5.LDACpinを20ns Low

から再度

1.アドレス0x14(or 0x15)に16bitのデータを設定

を行うまでの間に待機時間はどのくらい設けておりますでしょうか。

10.3.1.2.1 DAC Register Synchronous and Asynchronous Updatesの最後の行に記載されている「In both update modes a minimum wait time of 1 µs is required between DAC output updates.」につきまして、1us は 2.4usの誤記となります。

以上、宜しくお願いいたします。

Nishie

maida様

ご連絡ありがとうございます。

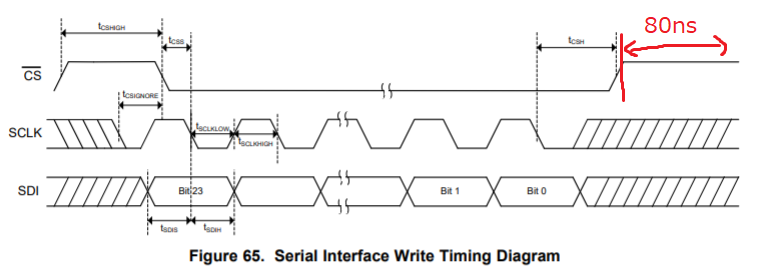

1, 2, 3, 4において「データを設定」と記載されておりますが、

このデータの設定はbit0までWriteを行い、Tcshも経過したタイミングという認識でよろしいでしょうか。

また、CS Highの開始タイミングは以下の画像の赤文字の通りでよろしかったでしょうか。

以上、宜しくお願いいたします。

Nishie

maida様

レジスタ設定に関して、データシートから読み取ることが出来ない為、詳細を確認したうえでメーカーに問い合わせをしたいと考えております。

80nsで設定できているレジスタアドレスと書き込んでいるデータの詳細をご教授頂けないでしょうか。

またTdacwaitに関して、メーカーに確認中ですのでもう少々お時間を頂けますと幸いです。

以上、宜しくお願いいたします。

Nishie

maida様

ご回答が遅くなり申し訳ございません。

■synchronous modeとasynchronous modeのどちらのモードでも、CH1のデータ設定後にCH3のデータ設定を行うまで、CSを2.4us以上Highにする必要がございますでしょうか?

→どちらのmodeも2.4us以上、CSをHighにする必要がございます。

Asynchronous modeの場合、CH1設定後からCH3の設定を開始するまでの待ち時間(2.4us)は必要ですが、1つのCHに対するデータの反映に待ち時間はございません。

■以下のレジスタ設定の中で、CS High時間2.4usにWaitが必要なレジスタはどこになりますか?

→すべてのレジスタ設定に2.4us以上の待ち時間が必要となります。

■LDAC端子制御に同期したDAC出力更新の場合でもDACnレジスタのCS High時間2.4usは必要となるのでしょうか?

→LDACによる制御(Synchronous mode)を行った場合も、2.4us以上必要となります。

本デバイスにはStreaming modeがございまして、こちらを使用した場合、連続した8つのDAC CHのレジスタ更新を待ち時間なく行うことが可能です。

ただしCH1→CH2→CH3というように連続して更新を行いますので、CH1→CH3というような更新方法ができなくなってしまいます。

以上、宜しくお願いいたします。

Nishie

-

投稿者投稿