フォーラムへの返信

-

投稿者投稿

-

wtidesigner様

追加でお問い合わせ頂き、ありがとうございます。

頂いたお問い合わせの件ですが、TI社に確認致しましたので、以下の内容で回答させて頂きます。

上記①の計算式に記載しておりますV_BULKminについてですが、

現在確認して頂いているExcel Design tooの場合、VBulk_min_tgtの値ではなく、

以下の式のようにExcel Design tool上のVin_Browninの値をもとに計算された値を用いております。

※上記の式は Vin_typeがACの場合の式となっております。Vin_typeがDCの場合は以下の式となります。

例えば、Vin_typeがACで、Lk=2.5uH, fsw=160kHz, Nps=5.25, Voutnom=20V, Vin_Brownin=80Vにて計算を行った場合、以下の値となります。

V_BULKmin=93.8896V

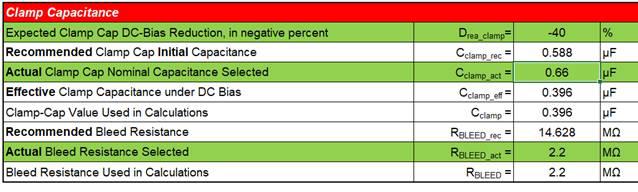

Cclamp_rec=0.353μF(DCバイアスの影響を考慮しない場合(Drea_clamp=0%))

Cclamp_rec=0.588μF(DCバイアスの影響を考慮した場合(Drea_clamp=-40%))

以上、よろしくお願い致します。

Ottey

kotauzu様

回答を御確認頂きありがとうございます。

追加で申し訳ございませんが、

BUF634Aの出力電流の規定は±250mA(Typical)となっておりますが、

基板放熱特性次第では出力電流を規定値以内になるように設計しても、Thermal Shutdownが働く可能性がございます。

そのため、基板放熱特性も考慮して頂きながら、設計を進めて頂ければと存じます。以上、よろしくお願い致します。

Ottey

kotauzu様

ご投稿頂き、ありがとうございます。

お問い合わせ頂いた電流制限機能に依存した使い方に関してですが、

もしBUF634Aの出力電流を電流制限値(±350mA程度)で使用する場合、デバイスのThermal Shutdown(データシートp.15に記載)が働き、出力が出なくなる(接続したヘッドフォンから音が出なくなる)可能性がございます。

そのため、出力電流250mA以内になるように回路を設計して頂ければと存じます。

(また、設計の際はデータシートp.6 “Output headroom to supplies”も御確認して頂ければと存じます。)

また、「BUF634Aの出力とヘッドフォン端子の間に保護抵抗を入れて保護した方が良いのか」については、アプリケーションや負荷条件によって変わります。そのため、貴社の実機(アプリケーション)で御確認して頂き、保護抵抗を入れるかどうかをご判断頂けますでしょうか。

以上、よろしくお願い致します。

Ottey

wtidesigner様

本件返信が遅くなり、大変申し訳ございません。

先日の回答にてデータシートとExcel Design toolのClampの式で差異があるとお答えさせて頂きましたが、

以下の内容をTI社に確認しましたので、回答させて頂きます。①Excel Design toolで使用されているClampの計算式について

Excel Design toolのClampには以下の式が使用されており、Lk, fsw, VBULKmin, Nps, Voutnomの値を入力することでClmapの計算値を求めることが可能です。②Excel Design toolに記載されているClampの値について

Excel Design toolでは、DCバイアスを考慮したClampの値を求めることが可能です。

以下の表は実際のExcel Design toolから抜粋したものとなり、それぞれのClampの値の説明は以下の通りとなります。

・Clamp_rec:上記の式から求めたClamp

・Clamp_act:実際に設計で使用するClampの値(手入力)

・Clamp_eff: Drea_clamp(手入力)をもとにDCバイアスを考慮して出したClampの実容量(Ccamp_actをもとに計算)

・Clamp:今後の計算で使用するClamp(Clamp_effの値を反映)③データシートとExcel Design toolから求められるClampについて

データシートやExcel Design toolで求められるClampの値はどちらも周辺回路の影響(漏れインダクタンス等)が考慮されていない、あくまで参考値となっております。

そのため、貴社の方でどちらかの方法でClampの値を設定して頂き、実機で動作を確認しながら、Clampの値を調整して頂けないでしょうか。以上、よろしくお願い致します。

ottey

wtidesigner様

ご投稿ありがとうございます。

返信が遅くなり、申し訳ございません。TI社にExcel Design Calculatorで使用されているClampの計算式について確認したところ、

データシート8.2.2.3項に記載されている計算式と差異があることは確認致しましたが、

詳細については引き続き確認をしている状況ですので、もう少々お待ち頂ければと存じます。以上、よろしくお願い致します。

ottey

wtidesigner様

返信頂き、ありがとうございます。

ADELピンとADLEFピンがCSピンと分圧抵抗を介して接続している場合、

貴社の御認識通り、CS電圧にバイアスをかける(CS電圧を変化させる)ことで、AB間だけでなく、CD間,AF間,BE間のTime Delayの値も変化致します。また、もし他のTime Delayを変えずにTABSETだけを変化させる場合、Rab=13kΩでCS電圧(もしくはADELピンに印加する固定電圧)を設定して頂いた上で、

Rcd、Refの値を調整して、他ののTime Delayを元の値に合わせて頂く方法しかございません。以上、よろしくお願い致します。

wtidesigner様

昨日の回答でご紹介したADELピンに固定電圧を印加する方法(Rabは13kΩに設定)について確認致しましたので、

追加で投稿致します。

まず、OUTA-OUTB(OUTC-OUTD)間のデッドタイムはRab(Rcd)の他にADELピンの電圧VADELによって調整することが可能です。

以前回答したKAの値を調整する方法では、ADELピンがCSピンと分圧抵抗を介して接続している場合の方法であるため、ADELピンの電圧VADELは、CSピンの電圧(CS)とADELピンの分圧抵抗によって決まります。(VADEL=CS×KA)

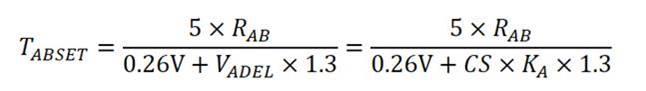

そのため、以下の式にてOUTA-OUTB間のデッドタイムを概算することが可能です。

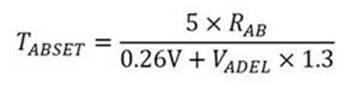

なお、今回のようにADELピンをCSピンと分圧抵抗を介して接続せず、直接固定電圧(最大2Vが推奨)を印加することにより、CSピンの電圧に依らず、デッドタイムを調整することが可能です。

(ADELピンはCSピン同様、他からバイアスをかける等で電圧が変化しても、制御特性は変化致しません。)

上記の方法では、VADEL には直接固定電圧を印加するため、OUTAーOUTB間のデッドタイムは以下の式にて概算することが可能です。

※上記に記載している2つの式は、外部のドライバ回路やスイッチングの応答時間の遅延などの外部遅延は考慮されておりません。

以上、よろしくお願い致します。

wtidesigner様

返信頂き、ありがとうございます。

システムが何かしらの内部制限(Dmaxなど)に達しない限り、他からバイアスをかける等でCSピンの電圧を変化させても、制御特性は変化しないと考えております。

また、他にデッドタイムを変更する方法として、ADELピンに固定電圧を印加する方法(Rab=13kΩに設定)がございますが、こちらについては詳細を確認しておりますので、少々お待ちいただければと存じます。

以上、よろしくお願い致します。

wtidesigner様

ご投稿ありがとうございます。

お問い合わせ頂いた内容についてですが、

Rabの許容範囲の下限13kΩはICの長期信頼性、上限90kΩはノイズ感度を考慮して設定されており、

Rabを許容範囲(13kΩ〜90kΩ)から外れた値に設定することは推奨されておりません。

(上記についてはTIにも確認いたしました。)また、デッドタイムを変更する方法としては、以下のデータシートp.19〜20に記載されているように

ADELピンに接続する抵抗値(RA, RAHI)を変更し、KAの値を調整する方法もございますので、

Rab=13kΩに設定して頂き、後はKAの値を変更することによりOUTA-OUTB間のデッドタイムを調整して頂けますでしょうか。

https://www.ti.com/lit/ds/symlink/ucc28950.pdf?&ts=1590138684360以上、よろしくお願い致します。

kaeru001様

返信が遅くなり、大変申し訳ございません。

今回貴社で確認されたVo(pin2)とVin(pin1)間の逆電圧に関してメーカーに確認致しましたところ、

データが無いため、許容範囲かどうか判断しかねるとのコメントを入手致しました。もしよろしければ、Vo(pin2)とVin(pin1)間の逆電圧をできるだけ小さくしていただくために

現在使用されている保護ダイオードを、Vfの小さいショットキーダイオードに変更して頂けますでしょうか。以上、よろしくお願い致します。

kaeru001様

ご投稿ありがとうございます。

返信が遅くなり、申し訳ございません。データシートを確認致しましたが、

Vo(pin2)とVin(pin1)間の逆電圧に対する規定はございませんでした。現在メーカーに確認をしておりますので、少々お待ちいただければと存じます。

以上、よろしくお願い致します。

SUNCON様

ご投稿頂き、ありがとうございます。

頂いたお問い合わせに対する回答ですが、以下の内容となります。

1.GD1,GD2に関して

データシートにはトランスもしくはゲートドライバを使用して、

FETにつなげておりますが、それがないとFETは動作しないのでしょうか?【回答】

GD2はHigh-side_FETをドライブするため、耐圧的にゲートドライバが必須です。

GD1は、動作しないことは御座いませんが、内部に2桁Ωの抵抗成分が有り、

Qgが大きい大電力用のFETを使用する場合には、ゲートに流入する電流が増え、

抵抗によりゲート電圧が低下する為、FETのON抵抗が増大する恐れが御座います。

FETのON抵抗は電源回路の効率と発熱に大きく影響します。

FETの高速ON/OFFと回路の低損失化にはゲートドライバを御使用頂くのが効果的です。②AC1,AC2には9.3MΩを、PFC段の電圧調整用の抵抗には30MΩと73.33kΩを

使用しなければならないと書いていますが

抵抗が少ないとどういう影響があるでしょうか?【回答】

ACx端子には60kΩの抵抗が内蔵されており、ACラインの周期的な電圧変化を内蔵抵抗により電流に変換し、

その電流値を読み取ります。

電流値のレンジは7uA~40uA程度です。

ACxに流入する電流が増えますとこの範囲から外れますので、正確なAC電圧検出が出来なくなる可能性が御座います。

そのため、AC1、AC2に接続する抵抗はデータシートの記載通りの9.3MΩのものをご使用頂ければと存じます。

また、PFC段の電圧調整用の抵抗(RTOP、RBOT)ですが、RTOPとRBOTの抵抗比率(30MΩ/ 73.33kΩ= 409.28)を大きく外れない限り、

抵抗値を小さくしていただくことは可能ですが、おっしゃる通り待機電力は大きくなります。以上、よろしくお願い致します。

SUNCON様

お返事いただき、ありがとうございます。

TLV2314のDatasheetに記載しているVo(Voltage output swing from supply rails)についてですが、

Voの値は電源電圧の値に対する値となります。

例えば電源電圧が5Vの場合、

Vo=5mVだとするとTLV2314の出力電圧範囲の最大値が4.995Vということになります。

(こちらの値は入力電圧がデータシートの範囲内の値の場合に限ります。)実際にご使用の際は、製品のバラツキも考慮してVoはmaxでの値で考えて頂ければと存じます。

以上、よろしくお願い致します。

SUNCON様

お世話になっております。

頂いた回路定数で弊社でも計算致しました。計算上はご指摘の通りではございますが、

TL3472の出力範囲(VOH)が、Typ:4V(Vcc+=5V)であるため、実機では計算上の値まで出力されず、

4.2V程度となっていると推察しております。

(現状の使用電源電圧は伺っておりませんでしたが、5Vで使用されていることを前提としております)そのため、現状の仕様(Gainなど)をTL3472の出力範囲に合わせて見直して頂くか、以下のような

Rail to Railの製品をご検討頂けますでしょうか。●TLV2314

HP:http://www.tij.co.jp/product/jp/TLV2314

DS:http://www.ti.com/jp/lit/ds/symlink/tlv2314.pdf以上、よろしくお願い致します。

otteyFJE

Osugi様

お世話になっております。

返信が遅くなり、申し訳ございません。

最初のご質問の件でメーカーに確認したところ、

データシートp.31にあるVQNパッケージのLAND PATTERN DATAについてはあくまで推奨例にすぎないので、その通りで設計する必要はないとのことです。

また、本ICでは発熱量が少ないので、VIAを追加する必要はないかもしれないとのことです。以上、よろしくお願いします。

-

投稿者投稿