フォーラムへの返信

-

投稿者投稿

-

wdwune様

お問い合わせ頂きましてありがとう御座います。

>> この原因はなぜでしょうか?

データシートの7.2項を御参照ください。COMPは内部エラーアンプの出力となって御座います。

Vinが喪失し、内部回路制御用バイアスが低下する際に、1.26Vの基準電圧も低下致します。

出力も戻り値であるFBの電圧が相対的にVrefよりも高くなるため、COMPの電圧も高くなります。>> この現象は必ず起こるものなのでしょうか?

必ず発生致します。

もし御不都合が無ければ、COMP電圧の上昇によって御社の設計に関し、どのようなデメリット/悪影響があるのか御教え頂けますでしょうか?>> COMP端子の最大電圧は何V でしょうか。

2.2V(typ)です。データシートのp6、表中のVEAO欄を御参照ください。

ちなみにエラーアンプのGainは38倍(typ)となって御座います。>> その影響する要因も踏まえてご教授ください。

現在起こっている使用上の御懸念や障害、不明点等を具体的に御指示頂けますでしょうか。宜しくお願い申し上げます。

Polnarefmaida様

Gate電圧が絶対最大定格を超えない条件下におきましては、Gate電圧が原因となる故障リスクは無いものとお考え頂きたく存じます。

Polnaref

maida様

紋切り型の回答で申し訳御座いませんが、GDRV端子の電圧が絶対最大定格を超える条件下におきましては、破損のリスクが御座います。

GDRV-FTE_Gate間に抵抗を入れる等、対策を施してお頂きたく存じます。Polnaref

wdwune様

メーカーより見解が得られましたので御報告申し上げます。

まず、snva742.pdfは5V入力/12V出力を条件としており、Vinが5Vより低い条件においては前提として最適化されておりません事、御了承ください。

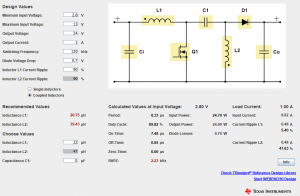

参考として2.8V入力/24V出力における定数設定(設計ツール)画面を添付いたしましたので御参照ください。

LM3478を用いてsnva742.pdfの回路を構成し、Vinが2.97V(UVLO_Max)より低いところから起動を開始した場合、スイッチングの度にVinが変動し、わずかな変動であっても正常軌道に必要なVinの閾値を下回る可能性があり、その度にスイッチングを停止、結果Dutyやfswが疎らになっていると思われます。

特に出力インピーダンスが高い入力ソースを用いた場合、その傾向が顕著に現れます。

対策としてはFA/SD端子を用いて、Vinが規定値未満においてはデバイスをDisableにすることをお勧め致します。Sepicトポロジーに関する詳細な解説は、下記URLを御参照ください。

http://www.ti.com/lit/an/slyt309/slyt309.pdf御参考になれば伊幸で御座います。

PolnarefAttachments:

wdwune様

メーカーへ回路図と波形を送り事象について質問いたします。

回答までしばらくお待ちください。Polnaref

aikawa様

御問合せ頂きましてありがとう御座います。

>> 同じシリーズでも、デバイスによっては、Back-Drive Protection機能有り無しがあるのでしょうか?

はい、373Aにはありますが125Aにはありません。

125AはNon Inverting Bufferですが、BufferでBack-Drive Protectionを御所望の場合には240や244Aをお勧めして御座います。

また、07Aもお使い頂けると存じます。御参考になれば幸で御座います。

Polnarefwdwune様

>> 起動時は、UVLOは働かないのでしょうか?

働きます。

御送り頂きました波形では、Vin(水色)は凡そ3V程度と見受けられます。

スイッチングが開始された時点のVin端子の電圧をお知らせ頂けますでしょうか?以上、よろしくお願い致します。

Polnarefwdwune様

>> Csepの容量を大きくするほど昇圧可能な電力が大きくなるという考えでしょうか?

はい、トランスに例えるなら、コンデンサの容量はコアサイズに相当します。>> 入力電圧が上昇していないにも関わらず

>> 発振を開始しているのはなぜだと考えられますでしょうか?

個体毎の特性バラツキによるものと思われます。以上、よろしくお願い致します。

Polnarefwdwune様

御指示頂きました回路例はSepicコンバータであり、昇圧コンバータとは設計方法が根本的に異なります。

昇圧コンバータはVin,Voutの電圧比からなるON_Dutyに従いインダクタに電力を蓄え、OFF_Dutyにてインダクタに蓄えられた電力を吐き出すことで昇圧を実現いたします。

Sepicは図中のL1,L2のインダクタンス比でDutyが決定され、昇圧に必要な電力の上限はCsepにより決定されます。SepicはL1,L2,Csepが疑似的なトランスのような動作を致します。>> 平均電流が抑えられる

前述のように、SepicはDutyがVin,Voutの電圧比ではなく、L1,L2のインダクタンス比で決定されるため、組み合わせ次第でDutyの「広がり過ぎ」を抑えることができ、結果的にピーク電流が抑えられます。

平均入力電流はVout*Iout/Vinの式で現わされるため、平均入力電流を小さくするにはVout又はIoutを小さくするか、Vinを大きくするしかありません。>> 使用するコンデンサの種類

セラミックコンデンサでも可です。必ず両極性のコンデンサを御使用ください。Polnaref

aikawa様

Back Drive protectionを有するICで出力がHigh_Zの時、出力端子にVcc以上(AbsMax未満)の電圧を印加しても問題御座いません。

ICがEnableに、出力端子にVcc以上の電圧を印加は定格違反となります。以上、宜しくお願い申し上げます。

Polnarefwdwune様

>>v入力電流を低く抑えたい

この電流が平均電流ではなくピーク電流を指しているのであれば、Lはそのままでfsw上げることで電流の低減は可能と思われます。

fswを上げますと、Duty(Vin,Voutの比で決定)は同じでも導通時間(ON_Duty時間)が短いため、インダクタ電流のΔIL(電流のピーク値とボトム値の差分)が減少するため、ピーク電流は抑えられます。

但し、結果的にL及びCoutの調整も必要になりますので併せて御検討下さい。Polnaref

etskbtskk様

御問合せ頂きましてありがとう御座います。

19pin,20pinはデバイス内部にてツェナーダイオード経由でGNDに接続されており、5.5V(Stand-Off電圧)にクランプされているため、Openでも問題御座いません。

もし浮遊ノイズなどによるピークチャージが心配でしたら、0Ω抵抗などにてGNDへ接続して頂きたく存じます。御参考になれば幸で御座います。

Polnarefaikawa様

Power_Off又はDisable時に出力をHigh_Zとし、更に出力から入力への逆電流を防止する機能を「Back Drive protection」と言います。

この機能はSN74LVC245Aには搭載されておりますが、SN74AHC125PWR/SN74AHC373PWRには搭載されておらず、この差分が反映された結果となって御座います。以上、宜しくお願い申し上げます。

Polnarefaikawa様

御問合せ頂きましてありがとう御座います。

御推察の通り、絶対最大定格を超えるため、使用条件としては定格違反となります。

SN74LVC8T245のような双方向レベルシフタを御検討下さい。御参考になれば幸で御座います。

Polnarefwdwune様

入力に安定化電源を使っても同様の現象となりますでしょうか?

御確認頂きたく存じます。Polnaref

-

投稿者投稿